Fターム[2H092JA31]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | チャネル長規定 (130)

Fターム[2H092JA31]に分類される特許

41 - 60 / 130

表示装置及び電子機器

【課題】半導体装置の回路規模を縮小する、または半導体装置の駆動能力の向上を図る。

【解決手段】酸化物半導体によりチャネル領域が形成されるトランジスタをプルダウントランジスタとして適用する。当該酸化物半導体は、2.0eV以上、好ましくは2.5eV以上、より好ましくは3.0eV以上のバンドギャップを有する。そのため、トランジスタにおけるホットキャリア劣化を抑制することができる。その結果、当該プルダウントランジスタを有する半導体装置の回路規模を縮小することができる。また、プルアップトランジスタのゲートを、当該トランジスタのスイッチングによって浮遊状態とする。なお、当該酸化物半導体を高純度化することで、トランジスタのオフ電流を1aA/μm(1×10−18A/μm)以下とすることが可能である。その結果、半導体装置の駆動能力の向上が図れる。

(もっと読む)

表示装置

【課題】表示装置の消費電力を低減すること及び表示の劣化(表示品質の低下)を抑制することを課題の一とする。また、本発明の一態様は、温度などの外部因子に対する表示の劣化(表示品質の低下)が抑制された液晶表示装置を提供することを課題の一とする。

【解決手段】表示装置の駆動回路部に、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示すると共に、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ、トランジスタをオフ状態として画面に書き込まれた画像をそのまま保持させておく機能を設ける。このような機能をオフ電流を、室温にてチャネル幅1μm当たり10zA/μm未満、85℃にて100zA/μm未満と極めて低いレベルにまで低減されたトランジスタによって実現する。

(もっと読む)

表示装置および電子機器

【課題】トランジスタのサイズ比を調整することにより、走査線駆動回路部の動作性能を向上させることが可能な表示装置を提供する。

【解決手段】この発明の液晶表示装置(表示装置)100では、トランジスタTr7のチャネル幅Wをチャネル幅Lで除したサイズ比(W/L)の大きさは、トランジスタTr1のチャネル幅Wをチャネル幅Lで除したサイズ比(W/L)の大きさの15%以上30%以下の大きさである。

(もっと読む)

表示装置および電子機器

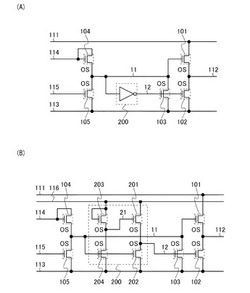

【課題】歩留まりを向上させることができ、かつ、消費電力が増加するのを抑制しながら、回路構成を簡素化することが可能な表示装置を提供する。

【解決手段】この発明の液晶表示装置(表示装置)100は、画素3に含まれる薄膜トランジスタ11と、薄膜トランジスタ11に接続されたゲート線9と、ゲート線9に接続されるメイン走査線駆動回路6およびサブ走査線駆動回路7と、通常時には、メイン走査線駆動回路6は、薄膜トランジスタ11を駆動する信号を出力するとともに、サブ走査線駆動回路7の出力がハイインピーダンスの状態になるように制御する走査線駆動回路制御部16とを備える。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、ホワイトバランスを維持しつつ、バックライトの赤色化による消費電力の低減を図る。

【解決手段】液晶パネルの各画素における緑サブ画素の開口率aGを所望値に固定した状態で、白輝度効率を、バックライトの色温度の低下に応じて増加する発光効率と、青サブ画素の開口率の増加に応じて減少する画素の透過率との釣り合いから定まる極大値にするように、赤サブ画素及び青サブ画素それぞれの開口率aR,aBを設定する。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

表示装置、スイッチング回路および電界効果トランジスタ

【課題】画素駆動用のスイッチング回路に用いる電界効果トランジスタのOFF電流特性の抑制およびON電流特性の向上を同時に図ることができ、スイッチング回路の高性能化により画質の向上を図ることができる表示装置を提供する。

【解決手段】一つまたは電気的に直列接続された複数の電界効果トランジスタを有するスイッチング回路において、少なくとも一つの電界効果トランジスタのチャネルとなる半導体層15の少なくとも一部の幅をチャネル長方向に連続的に変化させる。例えば、チャネル部における半導体層15のソース側の部分の幅をW50からW51に直線的に減少させ、他の部分は一定の幅W51とする。

(もっと読む)

液晶表示装置、液晶表示装置の駆動方法、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】端子部、スイッチングトランジスタ、及び画素電極を有する画素回路が形成された第1の基板と、対向電極が形成された第2の基板と、前記画素電極と前記対向電極との間には液晶素子が挟持されており、前記対向電極に入力される電位は、前記スイッチングトランジスタを介して端子部より供給され、前記スイッチングトランジスタが有する半導体層は、酸化物半導体層である。

(もっと読む)

表示装置

【課題】表示装置において、画素への信号の書き込み時間を短縮すること、また、高い電圧を印加する場合でも、信号の書き込みを高速に行うことを目的とする。

【解決手段】トランジスタと、前記トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、且つオフ電流が1×10−17A/μm以下であり、前記画素には、容量素子が設けられていない。容量素子を設けなくてもよいため、信号の書き込み時間を短縮することができる。

(もっと読む)

絶縁ゲート型トランジスタ

【課題】酸化物半導体を用いた絶縁ゲート型トランジスタに関し、短チャネル効果を極力抑えることのできる構成を提供する。

【解決手段】絶縁ゲート型トランジスタのチャネル領域を形成する酸化物半導体層に、脱水または脱水素化の工程及び酸素を添加する工程を施してキャリア濃度が1×1012/cm3未満となる真性又は実質的に真性な半導体を使用し、酸化物半導体層に形成されるチャネルの長さが0.2μm以上3.0μm以下であって、酸化物半導体層の厚さが15nm以上30nm以下で、かつゲート絶縁層の厚さが20nm以上50nm以下もしくは、酸化物半導体層の厚さが15nm以上100nm以下で、かつゲート絶縁層の厚さが10nm以上20nm以下とすることで短チャネル効果を抑え、上記チャネル長の範囲でしきい値の変動量を0.5V未満とすることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】不対結合手に代表される欠陥を多く含む絶縁層を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を間に介して、酸化物半導体層上に形成し、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を通過させて欠陥を含む絶縁層に拡散させ、上記酸化物半導体層中の不純物濃度を低減する。

(もっと読む)

液晶表示装置及び当該液晶表示装置を具備する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供する。

【解決手段】ゲート電極と、ゲート電極と重なるように設けられたゲート絶縁層及び酸化物半導体層と、酸化物半導体層の一部と重なるソース電極及びドレイン電極と、を有する薄膜トランジスタが、画素部に配設される信号線と画素電極との間に設けられており、薄膜トランジスタのオフ電流は、1×10−13A以下であって、液晶素子に並列した容量素子を設けずに液晶容量のみで電位を保持することが可能となり、画素部には画素電極と接続される容量素子が形成されていない構成の液晶表示装置とする。

(もっと読む)

半導体装置

【課題】寄生抵抗のさらなる低減を図る半導体装置を提供する。

【解決手段】ガラス基板1上にシリコン窒化膜2およびシリコン酸化膜3が形成されている。そのシリコン酸化膜3上に、ソース領域45、ドレイン領域46、チャネル領域40、GOLD領域41,42、ゲート絶縁膜5およびゲート電極6aを含むn型GOLD構造の薄膜トランジスタT4と、ソース領域45、ドレイン領域46、チャネル領域40、ゲート絶縁膜5およびゲート電極6aを含むn型SD構造の薄膜トランジスタT5と、p型のソース領域45、ドレイン領域46、チャネル領域40、ゲート絶縁膜5およびゲート電極6aを含むp型の薄膜トランジスタT6とが形成されている。

(もっと読む)

表示装置

【課題】結晶性シリコン薄膜トランジスタのオフ電流を低減させ、表示コントラストを向上させることが可能な表示装置を提供する。

【解決手段】基板SUB1上に形成されるゲート絶縁膜GIを介してゲート電極GTの上層に形成される第1の半導体層MSFと、第1の半導体層MSFの上面に形成され、凹部が形成される第2の半導体層ASFとからなる活性層と、凹部を挟んで対向配置される一対のコンタクト層CNLと、コンタクト層CNLの一方の上層に形成されるドレイン電極DTと、他方の上層に形成されるソース電極STと、活性層の上面及び前記ドレイン電極DTと前記ソース電極STの上面に連続して形成される保護膜PASiとを有する薄膜トランジスタを備え、凹部が形成されている領域の膜厚は160nm以上である装置。

(もっと読む)

半導体装置及び半導体装置を用いた表示装置

【課題】電極を精度良く形成できると共に、設計マージンを低減することが可能な構造の半導体装置を提供する。

【解決手段】薄膜トランジスタのゲート電極22と、このゲート電極22を覆って形成されたゲート絶縁膜23と、このゲート絶縁膜23上に形成され、薄膜トランジスタのソース領域、チャネル領域、ドレイン領域を構成する有機半導体層24と、この有機半導体層24上に形成された構造体31と、ゲート絶縁膜23上から構造体31よりも外側の有機半導体層24上にわたって形成された、薄膜トランジスタのソースドレイン電極25,26と、このソースドレイン電極25,26と同じ材料により、構造体31の上に形成された、電極材料層32とを含む半導体装置を構成する。

(もっと読む)

表示装置

【課題】D/A変換回路の構成を複雑にすることなく、多階調表示を可能とする表示装置を提供する。

【解決手段】外部から入力されるmビットデジタルビデオデータをnビットデジタルビデオデータに変換し、ソースドライバに前記nビットデジタルビデオデータを供給する回路と(m、nは共に2以上の正数、m>n)、を有する表示装置であって、電圧階調と時間階調とを同時に行い、2m-n個のサブフレームによって1フレームの映像を形成することによって表示を行う。

(もっと読む)

アクティブマトリクス基板およびその駆動回路

【課題】アクティブマトリクス基板において各信号線に存在する抵抗や容量の分布に起因して画素電位に生じるレベルシフトを当該基板内で略均一とすることを目的とする。

【解決手段】走査信号線に平行に共通電極線が形成されるアクティブマトリクス基板であるTFT基板において走査信号の立ち下がりの際に生じる画素電位のレベルシフトの不均一性を解消すべく、走査信号線駆動回路から電気的に遠ざかるにしたがって、また、共通電極線駆動回路から電気的に遠ざかるにしたがって、走査信号線−画素電極間容量Cgdが大きくなるように、各画素回路を形成する。

(もっと読む)

液晶表示装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成することにより、開口率を上げる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素部と駆動回路が設けられ、画素部の第1の薄膜トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する保護絶縁層と、保護絶縁層上に画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、保護絶縁層、及び画素電極層は透光性を有し、駆動回路の第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電材料である。

(もっと読む)

半導体装置およびその作製方法

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

41 - 60 / 130

[ Back to top ]