Fターム[2H092JA35]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | ゲート絶縁膜 (1,707) | 厚さ (297)

Fターム[2H092JA35]に分類される特許

161 - 180 / 297

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

基板、表示パネル、表示パネルの修正方法

【課題】参照配線や参照幹線に不良があった場合であっても、表示欠陥を防止できる基板、この基板を備える表示パネル、表示パネルの修正方法を提供すること。

【解決手段】参照配線113aに不良の有無を検出する工程と、不良が検出された場合には不良参照配線113sを特定して不良箇所Sを特定する工程とを有するとともに、不良が断線である場合には、不良参照配線113sと予備配線124とを短絡する工程と、不良参照配線113sが伝送する信号と同じ信号を伝送する所定の参照配線113mと予備配線124とを短絡する工程とを有し、不良が他の導体との短絡である場合には、不良参照配線113vの不良箇所Uの前後両側の箇所を切断する工程と、不良参照配線113vと予備配線124とを短絡する工程と、不良参照配線113vが伝送する信号と同じ信号を伝送する所定の参照配線113wと予備配線124とを短絡する工程とを有する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供する。

【解決手段】基板301上にゲート電極303を形成し、ゲート電極303を覆ってゲート絶縁膜304を形成し、ゲート絶縁膜304上に酸化物半導体膜305を形成し、酸化物半導体膜305上に第1の導電膜306及び第2の導電膜307を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも加熱処理LRTAにより結晶化した領域308を有する。

(もっと読む)

半透過性膜、表示デバイス、及びパターン基板の製造方法

【課題】生産性が向上し、かつ特性が良好な半透過性膜、表示デバイス、及びパターン基板の製造方法を提供することを目的とする。

【解決手段】本発明にかかる半透過性膜は、光学特性として光の透過特性と反射特性とを有する半透過性膜である。半透過性膜は、アルミニウム又はアルミニウムを主成分とする合金のいずれかに少なくとも40mol%以上50mol%未満の窒素を含む窒素含有膜である。また、半透過性膜は、上記の窒素含有膜と金属膜との積層膜とすることも可能である。

(もっと読む)

液晶表示装置

【課題】素子基板のマスク枚数を抑えて、ディスクリネーションを効率良く隠すとともに、比視感度の高い緑色を表示する画素については光漏れが目立ちにくくする。

【解決手段】直視型の透過型の液晶表示装置において、素子基板は、ゲート配線311と、ソース配線302と、画素TFTを有する画素部と、nチャネル型TFTやpチャネル型TFTを有する駆動回路とを含む。比視感度の高い緑表示の画素については、光漏れが目立ちやすいので、確実にディスクリネーションを遮光できるように、遮光膜を兼ねたドレイン電極313の面積を広くする。赤表示の画素については、遮光膜を兼ねた遮光電極314を狭い幅で設ける。青表示の画素については、明るさを優先して、遮光膜315を一部のみ形成する。

(もっと読む)

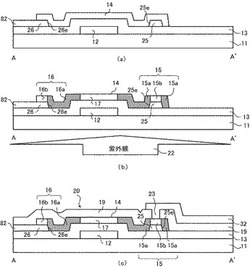

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層の高導電率化工程やソース電極及びドレイン電極のエッチング工程において、半導体層にダメージを与えないような薄膜トランジスタ及びこれを用いた液晶表示装置を提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の向こう側にソース電極又はドレイン電極が形成されてなるトップゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、紫外線の表面照射によって照射された半導体層部分を高導電率化するため、半導体層へのダメージが生じない。従って、高導電率化工程及びエッチング工程のいずれにおいても半導体層はダメージを受けることがないため信頼性が向上する。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

薄膜半導体装置、電気光学装置、および電子機器

【課題】各画素にN型とP型の2つの薄膜トランジスターを形成配置することによって、コンタクトホールの形成数が2つから4つに増え、薄膜トランジスターの平面的な占有面積が大きくなってしまう。

【解決手段】N型薄膜トランジスターNTのドレイン領域NDとP型薄膜トランジスターPTのドレイン領域PDとが部分的に隣接するように、また、N型薄膜トランジスターNTのソース領域NSとP型薄膜トランジスターPTのソース領域PSとが部分的に隣接するように、それぞれ配置されている。ドレイン領域NDとドレイン領域PDとの隣接部分に1つのコンタクトホール121が形成されて、ドレイン領域NDとドレイン領域PDとが、同時に信号線12と電気的に接続されている。ソース領域NSとソース領域PSとの隣接部分には、1つのコンタクトホール291が形成されて、ソース領域NSとソース領域PSとが、同時に容量電極29と接続されている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を無機絶縁膜で覆うことなく加熱処理を行って酸化物半導体層が結晶化されると、結晶化による表面凹凸などが形成され、電気特性のバラツキが発生する恐れがある。

【解決手段】酸化物半導体層成膜直後から酸化物半導体層上に接して酸化シリコンを含む無機絶縁膜を形成する直前までの間に1回も加熱処理を行わず、基板上の酸化物半導体層上に接して第2の絶縁膜を形成した後に加熱処理を行うプロセス順序とする。また、酸化シリコンを含む無機絶縁膜において、膜中に含まれる水素密度は、5×1020/cm3以上、または窒素密度は、1×1019/cm3以上とする。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

液晶表示装置及びその製造方法

【課題】FFSモードの液晶表示装置において、保持容量を増加させることなく液晶に印加される電界強度を維持又は増加させ、液晶駆動電圧の低電圧化、及びこれにともなう信号線ドライバー回路の発熱防止、高フレームレート化を実現する。

【解決手段】液晶の誘電率よりも誘電率の小さい絶縁層をコモン電極と複数のスリットが設けられている画素電極との間に設け、画素電極のスリット下の絶縁層の厚さを画素電極の透明導電層下の絶縁層の厚さよりも薄くなるように絶縁層をエッチングする。これにより、スリット下の絶縁層には凹部が形成され、液晶に印加される電界強度が増加し、より低電圧駆動が可能となる。また、絶縁層を一様に薄くするものではないため、保持容量の増加は少ない。

(もっと読む)

液晶表示装置用基板及びそれを用いた液晶表示装置

【課題】本発明は、スイッチング素子が形成されたアレイ基板側にカラーフィルタを形成したCF−on−TFT構造の液晶表示装置用基板に関し、フォトリソグラフィ工程を代表とする製造プロセスを簡略化でき、且つ高い信頼性を有する液晶表示装置用基板を提供することを目的とする。

【解決手段】ガラス基板3上にマトリクス状に配列された複数の画素領域Pから引き出されたゲートバスライン6に電気的に接続された第1の端子電極52aと、画素電極の形成材料でガラス基板3上に直接形成された第2の端子電極52bと、第1及び第2の端子電極52a、52bを電気的に接続する電極繋ぎ換え領域52cとを備え、外部回路とゲートバスライン6とを電気的に接続する外部接続端子を有するように構成する。

(もっと読む)

アクティブマトリックス基板の製造方法、アクティブマトリックス基板、電気光学装置、および電子機器

【課題】一枚の基板の両面にアクティブマトリックス回路が形成された基板の作成方法を提供すること。

【解決手段】アクティブマトリックス基板の製造方法は、基板1の第1面に第1のアクティブマトリックス回路を形成する第1工程と、第1工程の後に、基板1の第1面とは反対側の第2面に有機トランジスターを含む第2のアクティブマトリックス回路を形成する第2工程と、を有する。これにより、別々に作成した2枚の基板を貼り合わせるような方法と比べてより軽量かつ低コストで両面に機能を有するアクティブマトリックス基板を作成することができる。

(もっと読む)

電気光学装置及びその製造方法

【課題】例えば、液晶装置等の電気光学装置の製造に要するコスト削減と、表示性能の向上とを同時に実現する。

【解決手段】TFT(30)は、TFTアレイ基板(10)上において下側容量電極(80a)及び(80b)と同層に形成された半導体層(30a)と、その上に形成されたゲート絶縁膜(30b)と、ゲート電極(30c)とを備えて構成されている。半導体層(30a)は、TFTアレイ基板(10)の厚み方向に沿った厚みよりTFTアレイ基板(10)の基板面に沿った幅が大きくなるように形成されている。したがって、TFT(30)及び保持容量(70)によれば、液晶装置(1)の製造時に、ポリシリコン等の半導体からなる下側容量電極(80a)及び(80b)と共通の工程によってTFT(30)を形成可能であり、液晶装置(1)の製造プロセスを簡略化でき、且つ製造コストの低減できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含むIn−Sn−O系酸化物半導体層を用い、電気抵抗値の低い金属材料からなる配線層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含むIn−Sn−O系酸化物半導体層との間にソース領域又はドレイン領域を設ける。ソース領域又はドレイン領域、及び画素領域は同一層のSiOxを含まないIn−Sn−O系酸化物半導体層を用いる。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ソース・ドレイン電極形成時の活性層へのダメージを抑制するとともに、製造工程の簡略化を図ることが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】導電層50をエッチングによってパターニングすることにより、活性層18に接触するソース電極20及びドレイン電極22を形成するとともに、ソース電極20とドレイン電極22を除いた部分にソース電極20及びドレイン電極22よりも厚みが薄い導電層を第1保護薄膜56として残存させる工程と、第1保護薄膜56を半導体又は絶縁体に化学変化させて第2保護薄膜24を得る工程と、を含む薄膜トランジスタの製造方法を採用する。

(もっと読む)

結晶性半導体膜の作製方法及び薄膜トランジスタの作製方法

【課題】結晶粒径が大きく、均一な結晶性半導体膜を作製する方法を提供する。

【解決手段】絶縁膜上に接して結晶性半導体膜を形成する第1の工程と、前記第1の工程よりも核生成頻度が低い条件により結晶性半導体膜を成長させる第2の工程と、により結晶性半導体膜を作製する。第2の工程は、第1の工程よりも半導体材料ガスの流量比が小さい条件で行う。これにより、結晶粒径が大きく、均一性の高い結晶性半導体膜を得ることができ、結晶性半導体膜の下地膜に対するプラズマダメージを従来よりも低減することができる。

(もっと読む)

薄膜トランジスタ、その製造方法、半導体装置および表示装置

【課題】オン電流が大きく、かつ電気的特性のばらつきが小さな薄膜トランジスタおよびその製造方法を提供する。

【解決手段】周辺TFT110のチャネル層141を形成するシリコンの結晶粒径は、微結晶シリコンによって形成されているので、閾値電圧のばらつきをある程度抑えながら、オン電流を大きくすることができる。しかし、多結晶シリコンからなるチャネル層を有する周辺TFTと比べて、小さなオン電流しか流すことができない。そこで、周辺TFT110のゲート電極125と対向する窒化シリコン膜180の表面に、さらにゲート電極195を形成する。この結果、チャネル層341を流れるオン電流は、2つのゲート電極125、195によって制御されるので、オン電流の不足分を補うことができる。

(もっと読む)

161 - 180 / 297

[ Back to top ]