Fターム[2H092NA13]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 安定化 (3,125) | 素子欠陥減少 (75)

Fターム[2H092NA13]に分類される特許

1 - 20 / 75

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

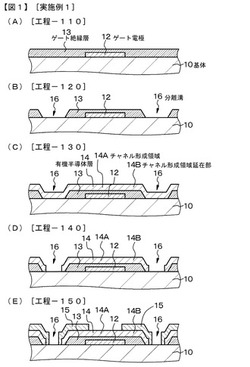

【課題】絶縁層上の有機半導体層をレーザ光を用いてパターニングしたときであっても、有機半導体層に損傷が生じ難い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(A)基体10上にゲート電極12を形成した後、(B)基体10及びゲート電極12上にゲート絶縁層13を形成し、次いで、(C)基体10に到達する分離溝16をゲート絶縁層13に形成した後、(D)ゲート絶縁層13上及び分離溝16の底部に露出した基体10上に有機半導体層14を形成し、次に、(E)少なくとも分離溝16の底部に露出した基体10上に形成された有機半導体層14の部分にレーザ光を照射して分離溝16の底部の少なくとも一部を露出させる一方、有機半導体層14の上に一対のソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

液晶ディスプレー、及びアレイ基板

【課題】本発明は、液晶ディスプレー、及びアレイ基板を提供する。

【解決手段】ベース基板と、前記ベース基板上に形成された第1層透明共通電極と、前記第1層透明共通電極上に形成されたゲート金属共通電極と、前記ゲート金属共通電極上に形成され、かつビアホールが形成されている絶縁層と、前記絶縁層上に形成された第2層透明共通電極とを備えるアレイ基板において、前記ビアホールの縁部は、一部がゲート金属共通電極に接触され、他の一部が第1層透明共通電極に接触されているので、前記第2層透明共通電極が前記第1層透明共通電極及び前記ゲート金属共通電極に電気的に接続されている。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】液晶表示装置において、製造工程中に残留する導電膜によって画素電極及びデータ配線が互いに短絡されることを防止して画素欠陥を減少させる。

【解決手段】液晶表示装置は、絶縁基板と、絶縁基板の上に位置するゲート線と、ゲート線を覆っているゲート絶縁膜30と、ゲート絶縁膜上に位置し、ドレーン電極とデータ線とを含むデータ配線と、データ配線を覆っている保護膜70と、保護膜の上に位置してデータ配線と電気的に連結されている画素電極80とを含み、ゲート絶縁膜は第1開口部を有し、保護膜は第2開口部と接触口72とを含み、第2開口部は前記第1開口部を露出させ、第1開口部と前記第2開口部は画素の縁領域に位置し、接触口72は前記ドレーン電極の一部分を露出させる。

(もっと読む)

液晶表示装置および電子機器

【課題】有機膜が剥離することに起因して、電極が腐食するのを抑制することが可能な液晶表示装置を提供する。

【解決手段】この液晶表示装置100は、基板1と、基板1の表面上に形成される薄膜トランジスタ16と、薄膜トランジスタ16の表面を覆うように形成される平坦化膜17と、平坦化膜17の側端面の下端部17bと平坦化膜17が設けられるゲート絶縁膜12の上面との境界領域を少なくとも覆うように設けられる導電層19と、導電層19の基板1の端部側の端部とゲート絶縁膜12の上面との境界領域を少なくとも覆うように設けられる低温パッシベーション膜20aとを備える。

(もっと読む)

表示装置、及び、表示装置の製造方法

【課題】第一の電極膜に接して形成されている導電膜を有する表示装置と、その製造方法の提供。

【解決手段】ゲート電極膜と、第一の電極膜及び第二の電極膜と、第一の電極膜に接続され、第一の導電層及び第一の導電層と重ねて形成される第二の導電層を含む導電層からなる導電膜と、を備える表示装置の製造方法であって、第一の電極膜と第二の電極膜とを形成する電極膜形成工程と、導電層を第一の電極膜及び第二の電極膜に接続するように形成する導電層形成工程と、導電層のうち所定の領域以外を除去することにより、導電膜を形成する導電膜形成工程と、を含み、導電層形成工程は、第一の導電層を第一の電極膜及び第二の電極膜それぞれの上面に形成する第一の導電層形成工程と、第一の導電層の上面に第二の導電層を形成する第二の導電層形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置、集積回路、マトリックス回路、表示素子、無線通信装置、電子機器、半導体装置の製造方法

【課題】エッチングによりソース・ドレイン電極を形成しても、有機半導体層が損傷を受けることなく、良好なオン/オフ比を示す有機半導体装置、及びその製造方法を提供することを目的とする。

【解決手段】基板1と、前記基板上に形成されたゲート電極2と、ゲート電極2及び基板1上に形成されたゲート絶縁層3と、ゲート絶縁層3上に形成されたp型有機半導体層4と、有機半導体層4上に形成された保護層5と、保護層5上に形成されたソース電極8及びドレイン電極9と、を有する半導体装置を構成する。

(もっと読む)

アレイ基板および当該アレイ基板の製造方法

【課題】 TFTアレイ基板の製造において、高開口率デバイスのようなアライメントルールが厳しい製品においても、マスク枚数を増やすことなく、アライメントずれによる容量起因の点欠陥が発生しないTFT構造を提供することを目的とする。

【解決手段】 第二の照射領域24よりも光量が高くて第三の照射領域25よりも光量が低い領域である第一の照射領域23と、パターン3と補助パターン10とが重畳してなす凸部11aとが重畳することにより、アライメントずれが生じても導電膜16が分断される。これにより、導電膜16からパターン形成される画素電極とソース配線9との近接による表示不良を抑制できる。

(もっと読む)

表示装置

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、上記腐食防止用塗料の塗布や剥離といった更なる工程を設けることなく、ピンホール腐食を防止することのできる表示装置を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、前記Al合金膜が、Niおよび/またはCoを0.15原子%以下(0原子%を含まない)、Geを0.2原子%以上2.0原子%以下、およびLa、Gd、NdおよびYよりなる群から選択される1種以上の元素を0.05原子%以上1.0原子%以下含有し、かつ、前記Al合金膜の表面において観察される腐食孔のアスペクト比(腐食深さ/腐食直径)が0.12以下であることを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ及びそれを用いた表示装置

【課題】薄膜トランジスタの膜中に発生する欠陥を低減させると共に、基板面内における欠陥発生位置のバラつきを低減させることが可能な薄膜トランジスタ及びそれを用いた表示装置を提供することである。

【解決手段】

ドレイン領域及びソース領域が形成される半導体層と、前記半導体層の下層に形成され前記半導体層への不純物の混入を防止するシリコン酸化膜層と、前記シリコン酸化膜層の下層に形成され前記半導体層への不純物の混入を前記シリコン酸化膜層と共に防止するシリコン窒化膜層とを備える薄膜トランジスタであって、前記シリコン酸化膜層は、前記シリコン窒化膜層の上層に形成される第1のシリコン酸化膜界面層と、前記第1のシリコン酸化膜の上層に形成されるシリコン酸化膜バルク層と、前記シリコン酸化膜バルク層の上層に形成される第2のシリコン酸化膜界面層とから形成され、前記第1のシリコン酸化膜界面層がシリコン酸窒化膜からなり、前記第2のシリコン酸化膜界面層が酸素欠損シリコン酸化膜からなる薄膜トランジスタである。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

表示装置

【課題】TFTと重なる領域に柱状スペーサを配置すると、一対の基板の貼り合わせ時に

圧力がかかり、TFTに影響を与える恐れ、クラックが発生する恐れなどがある。

【解決手段】TFTと重なる位置に形成される柱状スペーサの下方に無機材料からなるダ

ミー層を形成する。このダミー層をTFTと重なる位置に配置することによって、一対の

基板の貼り合わせ工程時にTFTにかかる圧力を分散し、緩和する。このダミー層は、工

程数を増やすことなく形成するため、画素電極と同じ材料で形成することが望ましい。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を示し、且つ、表示装置の製造過程における現像液耐食性や剥離液耐食性も高められた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、グループAに属するNiおよび/またはCoの元素を0.5原子%以下(0原子%を含まない。)と、Geを0.2〜2.0原子%と、グループBに属するYおよび/またはZrの元素を3原子%以下(0原子%を含まない。)とを含有する。

(もっと読む)

液晶装置の製造方法及び液晶装置の検査方法

【課題】例えば、ノーマリーブラック方式を表示方式として採用する液晶装置について、不具合が生じた保持容量を正確に破壊し、不良保持容量を含む画素部によって表示品位が低下することを抑制する。

【解決手段】不良保持容量(119A)を含む不良画素部(70A)は、走査線112A及びデータ線114Aの夫々に電気的に接続されており、不良保持容量(119A)を破壊する際に、走査線(112A)を介して不良画素部(70A)に供給された選択信号(SE)によって非導通状態から導通状態に切り替えられるTTF(30A)を介してデータ線(114A)及び不良保持容量(119A)が相互に電気的に接続された後、データ線(114A)を介して不良保持容量(119A)に電圧Vを印加される。

(もっと読む)

半導体素子の製造方法及び電気光学装置の製造方法

【課題】例えば、高い膜質を有する多結晶シリコン層を活性層とする薄膜トランジスタを製造する。

【解決手段】第1膜(211)の上面(211t)と、上面(211t)に交差する第1膜(211)の側面(211s)とによって構成された角部(212)をなくすように、第1膜(211)にスライスエッチング処理を施し、第1膜(211)から第2膜(220)を形成する。即ち、第2膜(220)の角部(222)の断面形状は、第1膜(211)の角部(212)に比べて、角が取れているように、或いは曲線で構成されるように形成されている。尚、スライスエッチング処理とは、第1膜(211)上から第1膜(211)にエッチング液を接触させることによって、通常のウェットエッチング法及びドライエッチング法に比べて、緩やかに、言い換えれば、マイルドに第1膜(211)をエッチング処理することをいう。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】、ポリシリコン膜に含まれる結晶欠陥を電気的に略不活性化させた場合でも、その後の工程での処理温度が限定されることがなく、かつ、能動層とゲート絶縁層との間に良好な界面を形成することができる半導体装置の製造方法、半導体装置および電気光学装置を提供すること。

【解決手段】半導体装置10tの製造工程では、電界効果型トランジスタ30nの能動層となるシリコン膜1sを結晶化させた後、シリコン膜1sに酸素プラズマ照射OPを行う酸素プラズマ照射工程と、酸素プラズマ照射工程によりシリコン膜1sに形成された表面酸化物1rを除去する表面酸化物除去工程とを行う。その後、シリコン膜1sをパターニングする。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】電界効果型トランジスタにおいて、半導体形成が簡便であり、かつ半導体形成によって前記上部画素電極への電圧の印加に問題が生じないようにバンク層を用いた構造を提供すること。

【解決手段】ゲート電極と、前記ゲート電極を覆うゲート絶縁層と、ソース電極と、下部画素電極と、前記下部画素電極に接続されたドレイン電極と、前記ソース電極及び前記ドレイン電極の間に形成された半導体と、前記半導体を囲み、前記下部電極を覆うように形成されたバンク層と、少なくとも前記下部画素電極上に開口部を有する層間絶縁層と、前記バンク層を介して前記下部画素電極に静電接続された上部画素電極とを備えることを特徴とする電界効果型トランジスタとする。

(もっと読む)

液晶表示装置用基板、液晶表示装置及びその製造方法

【課題】静電気の荷電量に関係なしに静電気から液晶表示基板を保護すること。

【解決手段】画像を表示する多数の画素電極と半導体素子とを有している透明な絶縁の第1基板と、前記第1基板上に形成され前記半導体素子と連結された配線と、隣接した前記配線との間に連結され、前記第1基板から発生される静電気を消耗させる多数のスパーク誘導回路とを含む。

(もっと読む)

表示装置

【課題】 薄膜トランジスタのドレイン電極とドレイン信号線との切断、および前記薄膜トランジスタのソース電極と画素電極との切断を行なう際に、ゲート信号線の損傷を回避させて行なうことのできる表示装置の提供。

【解決手段】 基板上に、複数のゲート信号線と複数のドレイン信号線を有し、当該ゲート信号線とドレイン信号線によって定義される画素領域に、薄膜トランジスタと画素電極を備えた表示装置において、前記薄膜トランジスタは、前記ゲート信号線に重畳する位置に形成された半導体層と、前記ドレイン信号線に接続されるドレイン電極と、前記画素電極に接続される前記ソース電極を備えて構成され、前記ドレイン電極およびソース電極は、前記ゲート信号線の長手方向の各辺のうち前記画素電極側の辺を越えて引き出されることを特徴とする。

(もっと読む)

1 - 20 / 75

[ Back to top ]