Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

561 - 580 / 766

金属配線形成方法、アクティブマトリクス基板の製造方法、デバイス及び電気光学装置並びに電子機器

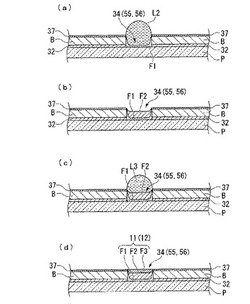

【課題】膜パターンの密着力を高めることができる膜パターンの形成方法を提供する。

【解決手段】基板P上に設けられたバンクBによって区画された配線形成領域34に液相

法により金属配線11、12が形成される。金属配線11、12は、配線形成領域の底部

、及び配線形成領域に臨むバンクBの側面に沿って成膜された第1膜F1と、第1膜F1

上に積層して成膜された第2膜F2とを有する。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタクト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクトホールを埋めるように形成されている。

(もっと読む)

絶縁膜の成膜方法、半導体装置の製法

【課題】 温度条件等を変えずに、炭素等の不純物が少なく、且つ欠陥が少ない良好な膜質の絶縁膜を得る。

【解決手段】 基板上にプラズマCVD法を用いて行う絶縁膜の成膜方法であって、前記プラズマCVD法において、絶縁膜の原料となる第一ガスと酸素を構成元素に含む第二ガスを用い、且つ該第一ガスを一定の時間間隔を設けて供給することを特徴とする絶縁膜の成膜方法である。

(もっと読む)

絶縁膜の成膜方法、半導体装置の製法、プラズマCVD装置

【課題】 プラズマCVD法により、原料となるガスとして有機材料ガスを用いて絶縁膜を形成する際、温度の上昇を抑制しつつ、有機材料ガスの乖離を十分に行い、絶縁膜を良好なものとする。

【解決手段】 基板にプラズマCVD法を用いて絶縁膜を成膜する方法であって、前記プラズマCVD法において、絶縁膜の原料となるガスとして有機材料ガスを用い、且つプラズマを発生させるために印加する高周波電力を、一定の時間間隔を設けて印加することを特徴とする絶縁膜の成膜方法である。

(もっと読む)

金属配線形成方法及びアクティブマトリクス基板の製造方法

【課題】下地層に対する導電層の密着性を向上させる。

【解決手段】基板P上に下地層形成材料を含む第1液状体を塗布する工程と、塗布した第1液状体を加熱処理して下地層F1を形成する工程と、下地層F1上に金属微粒子を含む第2液状体を塗布する工程と、塗布した第2液状体を加熱処理して導電層F2を形成する工程とを有する。下地層F1が未硬化状態となる条件で第1液状体を加熱処理した後に、第2液状体を塗布する。

(もっと読む)

半導体装置及びその動作方法

【課題】駆動用の電池の経時的劣化に伴う電池の残存容量の確認や電池の交換作業をすることなく、個体情報を送受信することができ、且つ外部からの電波または電磁波の電力が十分でない場合であっても良好な個体情報の送受信状態を維持するRFIDを有する半導体装置を提供することを課題とする。

【解決手段】RFIDにおける電力を供給するための電源としてバッテリー(2次電池ともいう)を設ける。そして、外部から受信した信号から得られる電力が所定の電力より大きいときには、その余剰電力をバッテリーに蓄え、外部から受信した信号から得られる電力が所定の電力より小さいときには、バッテリーから得られる電力を駆動するための電力に用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁性基板上に下地絶縁層を介して半導体層が形成された半導体装置において、絶縁性基板に含まれている不純物が半導体層に作用するのを防止して、半導体装置の信頼性を向上させる。

【解決手段】開示されるTFT10は、下地絶縁層2に、絶縁性基板1表面から略100nm以内の領域に、絶縁性基板1表面から半導体層3に向かってボロン濃度が平均的に1nmあたり略1/1000倍以下の割合で減少するようにボロンが含まれている。

(もっと読む)

自己整合電極を有するデバイスの作製方法

本発明は、薄膜トランジスタ、特に、パターニング技術が、下地電極に対して正確に整列される必要がある電極パターンの画定に使用される薄膜トランジスタなどの電子デバイスの作製に関する。作製方法は、狭い線幅を有する構造を形成することができない、及び/又は、先に堆積されたパターンに対してあまり正確に位置決めすることができない、レーザアブレーションパターニング技術または溶液ベースの直接書き込み印刷技法などの種々のパターニング技術に適用可能である。こうして、本発明者等は、減算的技法によるゲートパターニング、特に、選択的レーザアブレーションパターニングと、印刷などの加算的技法によるゲートパターニングの両方について適用可能である自己整合ゲート技法を述べる。技法は、低解像度ゲートパターニングの使用を容易にする。  (もっと読む)

(もっと読む)

積層配線及びその製造方法、並びに該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】開示される積層配線を用いたポリシリコンTFT20は、膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の15%以下となるように、あるいは、膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の85%以上となるように形成されている。

(もっと読む)

半導体接合部に薄膜物質を選択的に堆積させる方法

本発明の実施形態は、基板上に形成されたデバイスに高品質コンタクトレベル接続部を形成するプロセスを提供する。一実施形態において、基板上に物質を堆積させるための方法であって、基板を酸化物エッチング緩衝液にさらして、前処理プロセスで水素化シリコン層を形成するステップと、基板上に金属シリサイド層を堆積させるステップと、金属シリサイド層上に第一金属層(例えば、タングステン)を堆積させるステップと、を含む前記方法が提供される。酸化物エッチング緩衝液は、フッ化水素とアルカノールアミン化合物、例えば、エタノールアミン、ジエタノールアミン、又はトリエタノールを含有することができる。金属シリサイド層は、コバルド、ニッケル、又はタングステンを含有することができ、無電解堆積プロセスによって堆積させることができる。一例において、基板は、溶媒と金属錯体化合物を含有する無電解堆積溶液にさらされる。 (もっと読む)

薄膜光電変換装置

【課題】非晶質光電変換ユニットを含む薄膜光電変換装置に関して、その製造コストを抑制しつつ性能の優れた薄膜光電変換装置を提供する。

【解決手段】薄膜光電変換装置は、透光性基板(1)上に順に積層された主に酸化錫を含む透明導電層(2)、1以上の光電変換ユニット(3)、および裏面電極層(5)を含み、その透明導電層(2)の表面面積比が20%以上で40%以下の範囲内にあり、透明導電層(2)に接している光電変換ユニット(3)に含まれる非晶質光電変換層(3i)の厚さが0.3μm未満であることを特徴としている。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】 薄膜トランジスタの駆動特性を向上させることができる薄膜トランジスタ基板及びこれの製造方法が開示される。

【解決手段】 薄膜トランジスタ基板は、絶縁基板、絶縁基板上に形成されてゲートライン及びゲートラインに接続されたゲート電極を含むゲート配線、ゲート配線を覆うゲート絶縁膜、ゲート電極と対応してゲート絶縁膜上に形成された活性層、活性層上に形成された酸化防止層、並びにゲート絶縁膜及び酸化防止層上に形成され、データライン、ソース電極、及びドレイン電極を含むデータ配線を含む。ゲート配線及びデータ配線は、インジウム酸化物、銀、及びインジウム酸化物が順次積層された3層膜構造を有する。したがって、配線抵抗を減少させると共に薄膜トランジスタの駆動特性を向上させることができる。

(もっと読む)

金属膜、液晶表示装置、金属膜の製造方法

【要 約】

【課題】ITO膜との接触抵抗が低い金属膜を形成する。

【解決手段】アルミニウムを主成分とする金属膜25中にインジウム又は錫のいずれか一方又は両方を添加物として含有させ、アニールし、金属膜25内部の表面及び裏面付近に添加物の高濃度層25Iを形成する。金属膜25表面に形成されたITO膜から酸素が遊離しても、導電性を有するインジウム酸化物や錫酸化物が形成され、絶縁性のアルミニウム酸化物は形成されにくいので、接触抵抗が増大しない。

(もっと読む)

半導体装置の製造方法、電子光学装置の製造方法および電子機器の製造方法

【課題】不純物ドープ半導体膜を形成する際の熱負荷を低減する。また、熱負荷を低減することで、TFTの特性を向上させる。

【解決手段】半導体膜3および絶縁膜5を順次形成し、これらの膜よりなる積層膜した後、この積層膜を選択的に除去することにより、プール部7bおよびこのプール部7bに連結した一対の溝7aを形成し、プール部7bにドープ高次シラン組成物溶液9を充填し、この溶液9を溝7a内部に導入した後、熱処理によりドープシリコン膜9Aを形成する。次いで、溝7a間に位置する絶縁膜5上にゲート電極を形成することによりTFTを形成する。

(もっと読む)

TFT基板及びその製造方法

【課題】TFT基板の製造工程の工程数を削減し、製造処理時間を短縮し、よって製造コストを大幅に低減でき、且つ、製造歩留りを向上させる方法を及びそのTFT基板を提供することを目的とする。

【解決手段】ゲート配線及びゲート絶縁膜と、第1のシリコン層及び第2のシリコン層と、ソース・ドレイン配線及びソース・ドレイン電極と、前記ソース・ドレイン電極に電気的に接続された画素電極と、を具備したTFT基板であって、さらに、前記第1のシリコン層と、前記第2のシリコン層と、第1の金属膜と、層間絶縁膜と、前記層間絶縁膜のスルーホールを通して前記第1の金属膜と接続された透明電極層と、第2の金属膜と、の順に積層された積層膜を有し、前記積層膜の全部又は一部が 前記ソース・ドレイン電極であることを特徴とするTFT基板である

(もっと読む)

電界効果トランジスタ

【課題】ゲートリセス構造を有するIII−V族窒化物半導体を用いた電界効果トランジスタにおいて、ゲートリセス領域に生じる応力の影響に起因する高抵抗化を抑制し、寄生抵抗が小さい電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、第1のIII−V族窒化物からなる第1の半導体層14と、第1の半導体層14の上に形成された第2のIII−V族窒化物からなり、第1の半導体層14を露出するゲートリセス部16を有する第2の半導体層15と、第1の半導体層14におけるゲートリセス部16の上に形成されたゲート電極18とを備えている。第2の半導体層15が第1の半導体層14に加える応力と第2の半導体層14の厚さとの積は、0.1N/cm以下である。

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法

【課題】マスク工数を低減して生産性を向上した液晶表示装置用アレイ基板を提供する。

【解決手段】基板210上のゲート配線221及びゲート配線221から延びたゲート電極222と、ゲート配線221と交差し、ゲート絶縁膜230、半導体層240及びデータ金属層260からなるデータ配線261と、ゲート配線221とデータ配線261とから画定された画素に、第1透明金属層281aで形成された画素電極281と、データ配線261から延びたソース電極262及びソース電極262と離隔してチャネルを露出したドレイン電極263と、データ配線261、ソース電極262及びドレイン電極263、ゲート配線221上に形成され、ドレイン電極263と画素電極281とを接続し、ゲート配線221上で切断部を有する第2透明金属層291のパターンと画素電極281上の第2透明金属層291の近くに形成された隔壁293とを含む。

(もっと読む)

薄膜トランジスタ、TFTアレイ基板、及び薄膜トランジスタの製造方法

【課題】製造工程数の増加なく、ソース・ドレイン電極形成のための金属膜のドライエッチングに際して、下層の半導体膜の削れ量のばらつきを抑え特性の安定した薄膜トランジスタを製造する方法を提供する。

【解決手段】基板21上にゲート電極22を形成し、ゲート電極22上にゲート絶縁膜3を介して半導体膜4を形成する。そして、半導体膜4の主面上に、チャネル領域28を挟むように配置されたオーミックコンタクト膜5を介してソース電極24及びドレイン電極25を接合する。そして、オーミックコンタクト膜5上に、その一部が露出するように、かつチャネル領域28を挟むようにエッチストッパー層26を形成する。

(もっと読む)

異なった動作機能を示すゲートを有する2重ゲート半導体デバイスおよびその製造方法

2重ゲートFinFETおよびその製造方法を提供する。FinFETは、フィン(20)の各側面に隣接して第1および第2ゲート(72、74)を有し、第1ゲートのフィンに対面する少なくとも一部分を多結晶シリコンによって形成し、第2ゲートのフィンに対面する少なくとも一部分を金属シリサイド化合物によって形成する。2個のゲートの異なった組成は、それぞれ異なった動作機能を提供し、短チャンネル効果を減少させる。  (もっと読む)

(もっと読む)

薄膜トランジスタ基板とその製造方法、及び、薄膜トランジスタ基板製造用のマスク

【課題】ソース電極とドレイン電極との間の漏れ領域を縮小してオフ電流の経路長を増大させ、かつ薄膜トランジスタに照射された光によるキャリアの生成を抑え、それによりオフ電流を低減させる薄膜トランジスタ基板とその製造方法とを提供する。

【解決手段】本発明の一つの観点による薄膜トランジスタ基板では、薄膜トランジスタのチャンネル領域に露出した活性層がチャンネル領域から外に、ソースラインの幅に対して好ましくは30%以下の幅まで突出している。活性層をそのように露出させるために用いられるマスクでは、ソース遮光部とドレイン遮光部との間の凹形状の領域に、折線形状の細いスリットパターンから成る半透過部が形成されている。このマスクを用いてパターニングされた基板では、チャンネル領域から外に拡がる活性層の上記の突出部分から成るキャリアの移動可能領域(すなわち漏れ領域)が縮小する。

(もっと読む)

561 - 580 / 766

[ Back to top ]