Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

701 - 720 / 766

配線パターンを有する基板及びそれを用いた液晶表示装置

【課題】配線パターンを有する基板及びそれを用いた液晶表示装置において、配線パターンの多層金属構造を最適化し、インクジェット塗布等の液体プロセスにより主金属と副金属の配線パターンを形成することで、生産工程を簡素化する。

【解決手段】絶縁基板51上に形成した主金属のみのゲート電極11及び走査配線101と、これらの上に形成したゲート絶縁膜53と、このゲート絶縁膜上に形成した、走査配線と直交して主金属のみのソース電極12に接続する主金属のみのデータ配線201と、主金属のドレイン電極13と、ソース電極とドレイン電極とにそれぞれ接続する半導体層54,55と、このドレイン電極上に形成した副金属のキャップメタル67と、このキャップメタルとコンタクトホール59を介して接続する画素電極21とを備えた画素部300をマトリクス状に配置する。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】粗面を有する層を形成し、粗面上に導電性材料を含む組成物に対するぬれ性の低い領域と、組成物に対するぬれ性の高い領域を形成し、ぬれ性の高い領域に前記組成物を用いて導電層を形成する。ぬれ性が大きく異なる領域(ぬれ性に大きく差を有する領域)を形成できるので、液状の導電性材料又は絶縁性材料が、被形成領域のみに正確に付着する。よって、所望のパターンに正確に導電層、絶縁層を形成することができる

(もっと読む)

Al配線を備えた透明導電膜積層基板及びその製造方法。

【課題】 特定の金属を含有する透明導電材料を透明導電膜に使用することにより、Al配線を設けた積層基板の製造方法を簡略化する。

【解決手段】 透明基板と、前記透明基板上に設けられたAl配線と、酸化亜鉛を主成分とする導電性酸化物からなり、前記Al配線に直接接合する透明導電膜と、を含むことを特徴とするAl配線を備えた透明導電膜積層基板である。バリヤーメタルを間に設けず、直接Al配線と透明導電膜が直接接合しているので、製造工程を簡略化することができる。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び液晶表示装置

【課題】

本発明は、アルミ二ウム配線で発生するヒールロックを減少させる、薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】

本発明による薄膜トランジスタ基板は、下部アルミ二ウム層と、前記下部アルミ二ウム層の上に形成されている窒化アルミ二ウム層と、前記窒化アルミ二ウム層の上に形成されている上部アルミ二ウム層を含むことを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 微細な電極パターンを容易に実現し、かつ基材表面と電極パターン表面とが同一平面となるように形成することにより、電極の上部に積層する絶縁膜を薄膜化することができ、その結果トランジスタの駆動電圧を下げることが出来る薄膜トランジスタの製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタの製造方法は、基材表面に電極のパターンと同一形状の溝である凹部を形成する工程と、該凹部に対して電極材料を埋め込み、基板表面と同一の高さの埋め込み電極を形成する工程とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構成を有する薄膜トランジスタを提供する。またコンタクトホールの形成を、容易かつ確実に実施する方法を提供する。

【解決手段】断面がテーパー形状であるアルミニウムゲイト電極と、前記ゲイト電極上のゲイト絶縁膜と、前記ゲイト絶縁膜上のチャネル形成領域を構成するI型のアモルファスシリコン膜と、前記I型のアモルファスシリコン膜上の保護膜と、前記I型のアモルファスシリコン膜及び保護膜上のn型のアモルファスシリコン膜からなるソース領域及びドレイン領域と、前記ソース領域に電気的に接続されたアルミニウムソース電極と、前記ドレイン領域に電気的に接続されたアルミニウムドレイン電極と、前記ゲイト絶縁膜上の画素電極と、前記ゲイト電極に電気的に接続されたアルミニウムゲイト配線と、を有し、前記ドレイン領域と前記画素電極とはアルミニウムを介して電気的に接続されていることを特徴とする。

(もっと読む)

帯状のチャネルを有する半導体装置及びその製造方法

本発明は、基板(11)及び半導体本体(2)から成る半導体装置(10)であって、半導体本体(2)は、電界効果トランジスタが形成されるシリコンの帯状の半導体領域(3、3A、3B)を有し、第1導電型のソース領域(4)と、第1導電型と反対の第2導電型のチャネル領域(33)と、第1導電型のドレイン領域(5)とが連続して配置されており、続いて、帯状の半導体領域(3、3A、3B)の縦方向に示されるように、ゲート絶縁体(6)を具えたチャネル領域(33)が設けられ、第1接続領域(7A)を設けた第1ゲート電極(7)が、帯状の半導体領域(3、3A、3B)の第1垂直側部にあり、第2接続領域(8A)を設けた第2ゲート電極(8)が、帯状の半導体領域(3、3A、3B)の第1垂直側部とは反対の第2垂直側部にある半導体装置デバイスに関する。本発明によれば、第1及び第2ゲート電極(7、8)は、接続領域(7A、8A)の幅を超える帯状の半導体領域(3、3A、3B)の両側の空間を完全に満たす。好適な実施例において、ゲート電極(7、8)は、各々帯状の半導体領域(3、3A、3B)の横側に接している。本発明による半導体装置(10)は、非常にコンパクトで45nm未満の範囲に適しており、製造が容易である。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】好適な形状の配線を有する半導体装置を提供することを課題とする。

【解決手段】素子と接続される第1の導電層と、その上の第2の導電層とを形成し、第2の導電層上にレジストのマスクを形成し、マスクを用いたドライエッチングによって第2の導電層を加工し、マスクを残したままウエットエッチングによって第1の導電層を加工する配線の作製方法であって、ドライエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレートより大きく、ウエットエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレート以上とする。

(もっと読む)

薄膜半導体装置および液晶パネル

【課題】チャネル領域およびその近傍への迷光の入射を防ぐことが可能で光リーク電流の少ない薄膜トランジスタを有する薄膜半導体装置を提供する。

【解決手段】基板3上に設けられた配線パターン5と、配線パターン5を覆う層間絶縁膜7と、層間絶縁膜7上に設けられた半導体層9と、ゲート絶縁膜11を介して半導体層9上を横切る状態で設けられ層間絶縁膜7に形成された接続孔7aを介して配線パターン5に接続されたゲート電極13とを備えた薄膜半導体装置1において、ゲート電極13は、ゲート電極13が上部に重ねて配置された半導体層9のチャネル領域9aを挟んだ両側において、接続孔7aを介して配線パターン5に接続されている。

(もっと読む)

半導体装置およびその作製方法

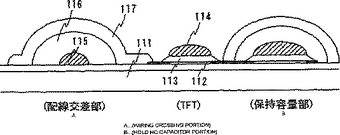

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

薄膜トランジスタ、その製造方法、これを有する表示装置、及び表示装置の製造方法

【課題】特性が向上した薄膜トランジスタの製造方法、これを有する表示装置、及び表示装置の製造方法を提供する。

【解決手段】薄膜トランジスタ100は、基板105上にゲート電極110、ゲート絶縁膜115、半導体パターン122及び半導体パターン上に相互離隔する第1及び第2導電性接合パターン127a,127b、第1バリヤーパターン131,141、ソース,ドレインパターン133,143、及び第1,第2キャッピングパターン135,145が形成されたソース,ドレイン電極130,140を含む。第1及び第2導電性接合パターン127a,127bが垂直なプロファイルを有するように形成する。

(もっと読む)

電界効果型トランジスタ

【課題】新規なトランジスタを提供する。

【解決手段】ソース電極708、ドレイン電極709、ゲート電極712、及び電子キャリア濃度が1018/cm3未満である非晶質酸化物を含む活性層を備え、且つ該ゲート電極と、該ソース及びドレイン電極が自己整合していることを特徴とする。

(もっと読む)

表面改質によるパターン化方法

(a)再配置可能なアパーチャマスクを基板の近くに配置する工程と、(b)基板の部分を表面改質処理に選択的に曝す工程であって、曝された部分が、アパーチャマスクの1つ以上のアパーチャによって画定される工程とによって表面改質をパターン化する方法。 (もっと読む)

電界効果型トランジスタ

【課題】 ソース、ドレイン、ゲート電極、有機半導体層などを形成する場合に印刷法、インクジェット法などの簡便な方法によって形成しても、ON/OFF比が良好な素子を実現する。また、短チャネルを実現することにより、動作電流が大きく、且つ素子間の特性のばらつきの少ない有機材料を用いた電界効果トランジスタを安価に提供する。

【解決手段】 少なくとも支持基板、ソース電極、ドレイン電極、活性層、絶縁層、ゲート電極からなり、ソース電極およびドレイン電極が同一平面内に形成され、前記ソース電極、ドレイン電極に隣接して隔壁が設けられてなる間の幅が少なくとも前記活性層にて電気的に接続されてなる活性層として有機物を用いた電界効果型トランジスタ素子において、前記の隔壁の高さがソース−ドレイン間とその他の箇所において、高さが異なる。

(もっと読む)

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

導電性パターンの形成方法

【課題】 より簡便に比較的厚さが大きく、インクの着弾径より小さな線幅でも着弾痕のない導電性パターンを得る形成方法を提供することにある。

【解決手段】 撥液剤80は、前述したようにバンク上面12eにおいて、水に対して110°以上の高い接触角を備えているため、導電性液状材料11に対しても接触角θは大きい。一方、バンク溝部20は前述したように親水性となっているために、基板10に到達した導電性液状材料11は、バンク上面12eに配設されている撥液剤80から圧縮力を受け、逆にバンク溝部20からは張力を受ける。このために、導電性液状材料11はバンク溝部20の溝に沿って、同図紙面の垂直方向の前後に広がっていくことができる。また、バンク溝幅Bが液滴の大きさDより大きい場合は、より安定して導電性液状材料11をバンク溝部20の中へ収容することができる。

(もっと読む)

トランジスタおよびその作製方法、並びに半導体装置

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

配線基板及び半導体装置の作製方法

【課題】少ない工程数で大面積基板に微細な形状を有する配線を形成する方法を提供する。また、少ない工程数及び原料の削減により、コスト削減及びスループットの向上が可能であり、かつ微細構造の半導体素子を有する半導体装置の作製方法を提供する。

【解決手段】金属粒子と有機樹脂とで形成される液状物質にレーザ光を照射し、金属粒子の一部を溶融した後、レーザ光が照射されない液状物質を除去して、配線、電極等に代表される導電層を基板上に形成することを特徴とする。また、本発明は、上記焼結された導電層を配線又は電極として有する半導体装置を形成することを特徴とする。

(もっと読む)

TFT基板

【課題】生産性を向上するTFT基板の提供。

【解決手段】ゲート電極上でゲートパッドを露出の絶縁膜パターン、ゲート電極及び絶縁膜パターン上に形成の半導体膜パターン、ゲート電極上の半導体膜パターンと接触の不純物注入半導体膜パターン、半導体膜パターン上に形成のソース及びドレイン電極とデータライン、ソース及びドレイン電極上且つゲートパッド領域で絶縁膜パターン上に形成の保護膜パターン、保護膜パターン上でドレイン電極に連結の第1画素電極パターンと、ゲートパッドに連結の第2画素電極パターンを備え、絶縁膜及び保護膜パターンはゲートパッド領域で重なり、ゲート電極、パッド及びラインは第1金属膜パターンと第1金属膜パターン上の第2金属膜パターンを含み、第2金属膜パターンの厚さは第1金属膜パターンに対し同じ又は薄く、第1金属膜パターンの幅は第1金属膜パターンの底から狭くなる。

(もっと読む)

701 - 720 / 766

[ Back to top ]