Fターム[4M104DD12]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | テーパ付け (105)

Fターム[4M104DD12]に分類される特許

81 - 100 / 105

半導体装置の製造方法

【課題】半導体基板の第2主面に導入された不純物を活性化でき、第2主面側を加工しながらも素子の特性劣化を防ぎ、第1主面側に精度良くコンタクトホールを形成することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板101の第1主面上に層間絶縁膜107を形成する工程と、コンタクトホール形成予定領域において、層間絶縁膜107を所定厚さ分残して除去する工程と、半導体基板101を第2主面側から所定厚さ除去して半導体基板101を薄くする工程と、薄くされた半導体基板101の第2主面の表層に不純物を導入する工程と、不純物の導入後、金属電極108を構成する材料の融点以上の温度で半導体基板101を熱処理する工程と、熱処理後、残された層間絶縁膜107を除去してコンタクトホール109を形成する工程と、コンタクトホール109内及び層間絶縁膜107上に金属電極108を形成する工程と、を備える。

(もっと読む)

電気光学装置用基板の製造方法及び電気光学装置の製造方法

【課題】簡易な装置により短時間で絶縁層を加工し開口部を形成することにより、電気光

学装置が高解像度化し画素数が増加しても容易に製造することができる電気光学装置用基

板の製造方法及び電気光学装置の製造方法を提供する。

【解決手段】電気光学装置用基板の製造方法は、基板12上に、ソース電極14とドレイ

ン電極16と有機半導体層18とを形成する。ソース電極14とドレイン電極16と有機

半導体層18とを被覆するゲート絶縁層20を形成する。ゲート絶縁層20上にゲート電

極22を形成する。ゲート絶縁層20とゲート電極22とを被覆する層間絶縁層24を形

成する。少なくとも層間絶縁層24とゲート絶縁層20とを貫通し、ドレイン電極16の

一部が露出する開口部を、機械的応力により形成する。層間絶縁層24上に、開口部を介

してドレイン電極16と電気的に接続する画素電極28を形成する。

(もっと読む)

半導体素子の製造方法

【課題】理想的なトレンチコンタクト形成によってコンタクトの低抵抗化と製造の低コスト化を実現する半導体素子の製造方法を提供する。

【解決手段】半導体装置の製造方法においては、半導体基板上に中間絶縁膜20を形成する工程と;前記中間絶縁膜上に第1の層22を形成する工程と;前記中間絶縁膜及び第1の層にコンタクトホールを形成する工程と;前記第1の層をハードマスクとして用いて、前記半導体基板に前記コンタクトホールと連通するトレンチ40を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孔の中や溝の中などに金属材料を埋め込んだ際のカバレッジ性を向上させること

ができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体装置91の製造方法は、まず、基板51上に低透過率のレジスト膜2

2を形成する。次に、ホログラフィック露光装置11を用いてレジスト膜22を露光及び

現像する。これにより、ホログラフィック露光装置11側が広いテーパ状の開口孔62a

を有する第1レジストパターン61aを形成することができる。この第1レジストパター

ン61aをマスクとしてシリコン酸化膜53を異方性にエッチングするとともに、第1レ

ジストパターン61aも異方性にエッチングする。これにより、第1レジストパターン6

1aの形状から第2レジストパターン61bの形状にすることができ、口元が広いテーパ

状のコンタクトホールを形成することが可能となる。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタは作製される。ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。  (もっと読む)

(もっと読む)

炭化珪素ディンプル基板

第1主表面と、第1主表面に対向した第2主表面とを有する、高熱伝導性の基板を含むディンプル基板およびその製造方法。活性エピタキシャル層が、基板の第1主表面の上に形成される。ディンプルが、第2主表面から基板中を第1主表面に向かって延びるように形成される。低抵抗材料からなる電気コンタクトが、第2主表面の上とディンプルの中に形成される。低抵抗で低損失のバックコンタクトがこのように、基板を効果的なヒートシンクとして維持しながら形成される。  (もっと読む)

(もっと読む)

ショットキーバリアダイオードおよびショットキーバリアダイオードの製造方法

【課題】レジスト直下部の突起形状の形成を抑制し、表面保護膜と金属膜の密着性を高めてメタルの段切れを防止することを目的とする。

【解決手段】表面保護膜3をエピタキシャル層2側から順にエッチングレートが速くなるような絶縁体の積層構造にすることにより、開口部4を形成する際に突起形状のできやすいレジスト膜直下領域の絶縁体のエッチングレートが最も速くなるため、レジスト直下部の突起形状の形成を抑制し、表面保護膜3と金属膜5の密着性を高めてメタルの段切れを防止することができる。

(もっと読む)

包囲条件を除去するためのプラグの拡大頭部を形成する構成体及び方法

【課題】 相互接続層を形成する場合に侵食されることのないコンタクト開口を形成する技術を提供する。

【解決手段】 絶縁層(34)を貫通するコンタクト開口が真直な側壁部分(42)とお椀形状側壁部分(40)とを有するように形成される。お椀形状側壁部分は絶縁層の上部近くであり底部と比較して上部においてコンタクト開口の拡大直径部分を与えている。導電性物質(46)をコンタクト開口内に形成し下部の導電層(32)と電気的接触を形成する。この導電性物質は拡大頭部(52)を有するプラグ(47)を形成する。この拡大頭部は、存在する場合に、コンタクト開口内のバリア層(45)が爾後の異方性エッチングによってエッチングされることを防止する。従って、例えばアルミニウム等の電気的相互接続層(48)がコンタクトプラグの上側に形成される場合に、そのプラグはエッチストップとして作用しコンタクト開口内のバリア層がエッチングされることを防止する。

(もっと読む)

半導体装置の製造方法

【課題】導電体と電気的に接続される配線パターンを備えた半導体装置の製造方法に関し、接続孔の形状ばらつきを抑制すると共に、製造コストを低減することのできる半導体装置の製造方法を提供する。

【解決手段】第1の開口部を有するレジスト膜24をマスクとする異方性ドライエッチングにより、絶縁膜13に凹部を形成し、その後、第1の開口部の側壁を形成するレジスト膜24を後退させて、第1の開口部よりも直径の大きい第2の開口部27を形成し、続いて、第2の開口部27が形成されたレジスト膜24をマスクとする異方性ドライエッチングにより、拡散層が露出するまで絶縁膜13をエッチングして、接続孔を形成する。

(もっと読む)

半導体装置

【課題】コンタクトホールを微細に形成する場合でも、絶縁膜の段差部分に目標通りの形状のテーパーを安定的に形成することが可能な半導体装置を提供することを目的とする。

【解決手段】絶縁膜48がストライプ状の各ゲート電極41を覆う主部分とゲート電極41のストライプ幅方向にのびる補強部分とを有するように、絶縁膜48にコンタクトホール43を形成する。

(もっと読む)

半導体素子の製造方法

【課題】高耐圧の半導体素子における複数の絶縁膜からなる厚い絶縁層にコンタクト部を形成するのに好適で、コンタクト部のステップカバレッジを向上することができる半導体素子の製造方法を提供する。

【解決手段】 本発明は、半導体基板11に複数の絶縁膜を堆積させ、絶縁膜にコンタクト部21を形成する半導体素子の製造方法であって、半導体基板11の上面に下地絶縁膜12を形成し、下地絶縁膜12における、コンタクト部に相当する位置にコンタクト孔12aを形成し、下地絶縁膜12を覆うように上側絶縁膜13をCVD法によって形成し、且つ、上側絶縁膜13におけるコンタクト孔12aの上方に位置する面13aを順テーパ化するため表面改質処理を施すことで、1つ又は複数の上側絶縁膜13を形成し、表面改質処理後に、コンタクト孔12aをウェットエッチングによって開口させることでコンタクト部21を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクト底寸法のばらつきを抑え、かつコンタクト上部はリソグラフィでの開口径を拡大させることなくテーパとなるコンタクトを得る。

【解決手段】 半導体基板11と、その上に形成された層間絶縁膜13と、層間絶縁膜13の中に形成されたコンタクトホール13Dとを有する半導体装置であって、コンタクトホール13Dは、層間絶縁膜13の表面から半導体基板11へ向かって次第に小さくなる径を有し且つ、コンタクトホール13Dの側壁は3つ以上のテーパ領域13A,13B,13Cからなり、半導体基板11に最も近接するテーパ領域13Aでの側壁と半導体基板11の表面との成す第1の角度θAは約90度であり、他のテーパ領域13B,13Cでの側壁と半導体基板11の主面との成す角度θB、θCは鋭角であり且つ第1の角度θAよりも小さい。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 層間絶縁膜としてシリコン窒化膜を用いた場合に、エッチング残りの無いコンタクトエッチング及び多結晶半導体層を消失させることのない安定したコンタクトエッチングを可能とする。

【解決手段】 多結晶半導体層3上にゲート絶縁膜4を介してゲート電極5が形成され、さらに層間絶縁膜6が形成されてなる薄膜トランジスタである。層間絶縁膜6及びゲート絶縁膜4にコンタクトホール7が形成され、信号線電極8がコンタクトホール7を介して多結晶半導体層3と接続されている。層間絶縁膜6は、シリコン酸化膜6aと、その上に形成されるシリコン窒化膜6bとを有する。コンタクトホールのエッチングに際しては、シリコン酸化膜に到達するまでコンタクトホールをエッチング形成する第1のエッチングを行い、この第1のエッチングと連続してシリコン酸化膜とゲート絶縁膜にコンタクトホールをエッチング形成する第2のエッチングを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体基板への電気的接触をとるコンタクトホールにおいて、接触抵抗の低減を図る。

【解決手段】 シリコン基板1にはSTI2により素子形成領域5が区画形成されている。STI2はシリコン基板1の表面より突出している。上面にシリコン窒化膜7、層間絶縁膜8が積層形成されている。STI2、2間にコンタクトホール9が形成されている。コンタクトホール9は、層間絶縁膜8部分のホール上部9aとシリコン基板1部分のホール下部9cを有する。ホール下部9cは、RIE法の加工の後CDE法の加工をすることで横方向に広がる形状に形成され、RIE法のみの場合よりもシリコン基板1との接触面積が増大している。

(もっと読む)

半導体装置の製造方法

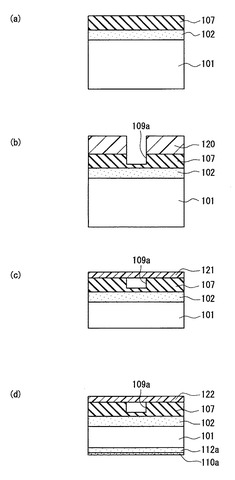

【課題】薄膜化された半導体層を貫通することなく、良好な形状のコンタクトホールを形成することができる半導体装置の製造方法を提供する。

【解決手段】絶縁層8の上に設けられた半導体層10に絶縁ゲート電界効果型トランジスタ20を形成すること、前記絶縁ゲート電界効果型トランジスタ20を覆う層間絶縁層30に、前記絶縁ゲート電界効果型トランジスタ20のソース領域またはドレイン領域となる不純物領域28と接続されるコンタクト層38を形成すること、を含み、前記層間絶縁層30はエッチング速度の異なる積層膜32,34で形成し、所定のパターンのマスク層50を用いて第1エッチングを行い、前記不純物領域28の表面が露出しないような凹部36aを形成した後、該不純物領域28の表面が露出するまで等方性エッチングである第2エッチングを行うことでコンタクトホール36を形成すること、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】0.20μm以下のホトリソグラフィー径でも合わせばらつきを含んだより狭いゲート電極間隔必要幅を確保したテーパー形状のコンタクトを形成できる。

【解決手段】上部にシリコン酸化膜4、その下にBPSG膜3、該BPSG膜中にゲート電極8を有し、ゲート電極の上面、側面及び上部にシリコン窒化膜を生成しない構造の半導体装置のゲート電極間に微細なコンタクトを形成する方法において、シリコン酸化膜をCF4/O2/Ar混合ガスで基板温度40℃以上にてエッチングし、さらにそのオーバーエッチングでBPSG膜を断面形状楔形(W形)に加工する工程と、引き続きBPSG膜をC4F8/CH2F2/Ar混合ガス(但しCOおよびO2を含有しない。)でゲート電極間に90度未満の順テーパーエッチングする工程とをこの順に行う。

(もっと読む)

リセスゲート及びそれを備えた半導体装置の製造方法

【課題】リセスに埋め込まれるゲート電極物質の蒸着時にボイドを発生させずに、リセスゲートの高さを低減できるリセスゲート及びそれを備えた半導体装置の製造方法を提供する。

【解決手段】シリコン基板と、前記シリコン基板の所定部分に所定深さを有して形成されたリセスパターンと、前記リセスパターンの表面に形成されたゲート絶縁膜と、前記ゲート絶縁膜の表面上に形成されたゲートポリシリコン膜と、前記ゲートポリシリコン膜の表面上に形成され、前記リセスパターンを埋め込むように形成されたゲートメタル膜と、前記ゲートメタル膜の上に形成されたゲートハードマスクとを含む。

(もっと読む)

配線パターン形成方法および配線パターン

【課題】液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】基板10Aの表面Sにヘキサメチルシラザンを基板10Aの表面Sに塗布し、HMDS層12を形成するヘキサメチルシラザン層形成工程と、HMDS層12上に、有機感光性材料層を形成する有機感光性材料層形成工程と、前記有機感光性材料層をパターニングしてバンクパターン18を形成する工程と、バンクパターン18によって縁取られた領域に、インクジェット法を用いて、導電性材料を付与する導電性材料付与工程と、を含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】 微細な薄膜トランジスタの製造工程において、大型基板面内で均一性良く信頼性が高いコンタクトコールおよびコンタクト配線を形成する。

【解決手段】 層間絶縁膜9に対する10:1 BHFによるウェットエッチングに続いて、同一レジストマスク10を用いたドライエッチングを行うことにより、層間絶縁膜9およびゲート絶縁膜4にコンタクトホール11,12を連続して形成する。コンタクトホール11,12は、層間絶縁膜9の深さ方向途中まで設けられて、表面側に広く開口するテーパ状開口部と、このテーパ状開口部に連通し、層間絶縁膜9の深さ方向途中からソース/ドレイン領域3cが露出するまで設けられた表面に垂直な壁面の筒状開口部とを有する。

(もっと読む)

コンタクトホールの形成方法及びドライエッチング装置

【課題】 微細なコンタクトホールを精度良く形成することができるようにしたコンタクトホールの形成方法及びドライエッチング装置を提供する。

【解決手段】 半導体基板20表面のS/D領域25上を覆う層間絶縁膜40にS/D領域25に至るコンタクトホールを形成する方法であって、層間絶縁膜40上にS/D領域25の上方を開口するレジストパターン50を形成する。次に、このレジスパターン50をマスクに層間絶縁膜40を半導体基板20表面に対して垂直にドライエッチングして、層間絶縁膜40にS/D領域25に至る開口部100´を形成する。そして、このレジストパターン50をマスクに、開口部100´が形成された層間絶縁膜40を半導体基板20表面に対して斜めにドライエッチングする。

(もっと読む)

81 - 100 / 105

[ Back to top ]