Fターム[4M104EE18]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 材質 (4,070) | 有機物 (303)

Fターム[4M104EE18]に分類される特許

181 - 200 / 303

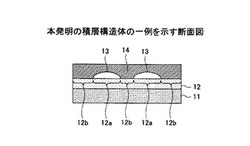

積層構造体及びその製造方法

【課題】本発明は、少ない紫外線照射量で表面自由エネルギーを変化させることが可能な積層構造体及び該積層構造体の製造方法を提供することを目的とする。また、本発明は、該積層構造体を有する電子素子、該電子素子を複数有する電子素子アレイ及び該電子素子アレイを有する表示装置を提供することを目的とする。

【解決手段】積層構造体は、基板11上に、エネルギーを付与することにより臨界表面張力が変化する材料を含有する濡れ性変化層12と、濡れ性変化層12にパターン形成された導電層13を有し、臨界表面張力が変化する材料は、主鎖と側鎖を有し、側鎖は、エネルギーを吸収すると結合が開裂する部位を2個以上有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の目的は、液体が浸透しにくい配線20をスパッタリングによって形成することにある。

【解決手段】金属膜24を配線20の形状にエッチングしてパターニングする。パターニングされた金属膜24をマスクとして下地膜22をウェットエッチングによってパターニングする。金属膜24を形成する工程は、第1のスパッタリングによって第1の膜26を形成することと、第1のスパッタリングと同一膜種の第2のスパッタリングによって第1の膜26の上に第2の膜28を形成する。第1及び第2のスパッタリングは、二次元核成長及び二次元核成長後の三次元核成長によって、それぞれ第1及び第2の膜28を形成する。第1のスパッタリングを止めて第1の膜26の三次元核成長を中断した後に、第2の膜28の成長が二次元核成長から始まるように第2のスパッタリングを開始する。

(もっと読む)

半導体装置及びその作製方法

【課題】動作特性及び信頼性の向上した新規な構造の半導体装置及びその作製方法を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領域及びゲート電極の間に設けられた第2絶縁層と、を有する。半導体層は局所的に薄膜化され、薄膜化された領域にチャネル形成領域が設けられており、第2絶縁層は、少なくともゲート電極が重畳する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

薄膜トランジスタアレイおよびその製造方法

【課題】 本発明は、クシ型電極を用いた薄膜トランジスタのフィードスルーを低減しつつ、電極の電気抵抗の増大や作製の難しさを改善した薄膜トランジスタアレイを提供することを課題とする。

【解決手段】 ソース・ドレイン電極をクシ型とし、ドレイン電極の幅をソース電極の幅より細くし、ドレイン電極あるいはソース・ドレイン電極の根元をテーパー状にすることにより、電気抵抗の増大を抑制し、かつ歩留まりを向上した薄膜トランジスタアレイ。

(もっと読む)

パターン形成方法および半導体装置の製造方法

【課題】スクリーン印刷法により、インクの滲みや裏周りが防止され、印刷形状が安定化されたパターン形成方法およびこれを用いた半導体装置の製造方法を提供する。

【解決手段】基板11上に、ソース・ドレイン電極12と、ゲート絶縁膜と、有機半導体層と、ゲート電極とをこの順に積層してなる半導体装置の製造方法において、基板11上に導電性膜12’を介して撥液層A1を形成した後、スクリーン印刷法により、レジストインクR1’を印刷することで、撥液層A1上にレジストパターンR1を形成し、このレジストパターンR1をマスクに用いて、導電性膜12’をエッチングすることで、ソース・ドレイン電極12を形成することを特徴とするパターン形成方法および半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】 ニッケルシリサイドのタングステン含有率を容易に調整可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板1の素子領域1A上にニッケル膜5を形成する工程S1と、シリコン基板1及びニッケル膜5を熱処理し、素子領域1Aの表面をシリサイド化する工程S3と、素子領域1Aの表面をシリサイド化する工程の後に、シリコン基板1上に残留するニッケル膜5を除去する工程S4と、シリコン基板1上に残留するニッケル膜5を除去する工程の後に、6フッ化タングステンガス(WF6)を含む雰囲気中において素子領域1Aの表面を熱処理する工程S6とを含む。

(もっと読む)

半導体装置の作製方法

【課題】また、従来のCADツールによる半導体装置の設計図を用いる場合、インクジェット装置で形成できるパターンが限られるため、半導体装置の回路の中には、そのまま転用することができない回路も生じる恐れがある。

【解決手段】インクジェット装置で吐出して描くことの可能な基本パターンを複数用意し、それらを組み合わせて所望の集積回路のレイアウトを行う。得られたレイアウトを基にして露光マスクを形成する。露光マスクを用いて露光を行った後、現像して液滴の径よりも幅の細い露光領域にレジスト膜を残存させる。そして、被処理表面の露呈部分に対して撥液処理を行った後、レジスト膜上に材料液滴を滴下する。液滴吐出法により選択的に吐出を行い、ドット径よりも幅の細い配線を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】高温のプロセスを要することなく高分子基材への素子作製が可能であり、かつ低コストで高性能、高信頼性を達成することができる薄膜トランジスタを得ることを目的とする。

【解決手段】ソース電極4、ドレン電極5及びゲート電極1の3電極、チャネル層3及びゲート絶縁膜2の各要素を具備してなる薄膜トランジスタにおいて、少なくともチャネル層3がインジウムを含む金属酸化物膜で形成されていることを特徴とする薄膜トランジスタを提供する。

(もっと読む)

有機デバイスとその製造方法

【課題】有機トランジスタの有機層とソース、ドレイン電極との密着性が悪く、接触抵抗が高いことを課題とする。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記ゲート電極上に形成された絶縁層と、前記絶縁層表面と片末端が共有結合した有機分子層と、前記分子層の他末端が共有結合した触媒層と、前記触媒層上に形成されたソース、ドレイン電極から構成されることを特徴とする有機トランジスタを提供することにより上記課題を解決する。

(もっと読む)

薄膜電極の製造方法

【課題】基板との密着性が良好で、しかも光透過性に優れかつ高度な平滑性や配向性を有する薄膜電極を、安価な製造装置を使用して簡単な工程で、低コストで製造する方法を提供する。

【解決手段】天然マイカのへき開面のような、へき開性を有する単結晶状態の(100)配向面に導電性薄膜を形成した後に、該導電性薄膜を高分子接着剤層を介して基板に接合し、前記(100)配向面を剥離することにより薄膜電極を製造する。導電性薄膜は、金属又は金属酸化物、特に貴金属又は貴金属酸化物により構成することが好ましい。

(もっと読む)

半導体装置及びその作製方法

【課題】SOI基板を用いて作製した半導体装置において、島状に設けられたシリコン層の端部に起因する不良を防止し、信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられたゲート電極と、を有する構造とする。このとき、ゲート絶縁層は、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率を小さくする。

(もっと読む)

半導体装置及びその作製方法

【課題】島状に設けられた半導体層の端部に起因する不良を防止し、信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】基板上に設けられた島状の半導体層と、島状の半導体層の一表面上及び側面に設けられた絶縁層と、絶縁層を介して島状の半導体層上に設けられたゲート電極と、を有する構造とする。このとき、島状の半導体層に接して設けた絶縁層において、島状の半導体層の一表面上と比較して、島状の半導体層の側面と接する領域の誘電率を小さくする。

(もっと読む)

電子素子、及びその製造方法

【課題】電子素子、及びその製造方法を提供する。

【解決手段】工程段階を減らし、インクジェットプリンティングのような経済的な方法を使用して、フッ素化有機高分子のような絶縁層を直接パターニングできる電子素子の製造方法、並びに該製造方法によって形成されるバンク構造を有する電子素子である。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上に、ゲート絶縁膜及びゲート電極を設け、それらの側面にダミー側壁を形成し、その周囲を層間絶縁膜で囲み、前記ゲート電極及びダミー側壁の上面が露出する構造を提供する工程と、

前記ダミー側壁を除去して空洞を形成する工程と、

前記空洞内を側壁材料で埋め、側壁を形成する工程と

を具備する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上にダミーゲート層を形成する工程と、前記ダミーゲート層の側面に、ダミーゲート層を構成する材料との間で、エッチング選択性を有する側壁絶縁膜を形成する工程と、全面に層間絶縁膜を堆積する工程と、前記層間絶縁膜を、前記ダミーゲート層の上面が露出するまで除去する工程と、前記ダミーゲート層を除去し、溝を形成する工程と、前記溝の底面にゲート絶縁膜を形成する工程と、底面にゲート絶縁膜が形成された前記溝内にゲート電極を形成する工程とを具備することを特徴とする。

(もっと読む)

薄膜トランジスタ及び有機薄膜トランジスタ

【課題】高移動度かつ高オン/オフ比を有する薄膜トランジスタ及び有機薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタであって、ソース電極と、ドレイン電極と、半導体層とを含み、前記ソース電極と前記ドレイン電極とはそれぞれ第1層と第2層とを含み、前記ソース電極の第1層の仕事関数と前記半導体層のエネルギレベルとの差は、最低0.5eVであり、前記ソース電極の第2層の仕事関数と前記半導体層のエネルギレベルとの差は、最大0.2eVであり、前記半導体層のチャネル長は20マイクロメートル以下である。

(もっと読む)

有機薄膜トランジスタ

【課題】

ソース/ドレイン電極と有機半導体層の電荷注入障壁を低減させ、かつ界面状態を均一化させることのできる有機薄膜トランジスタの提供。

【解決手段】

ソース/ドレイン電極と有機半導体層との界面に該電極を構成する金属とスルフィド結合した下記式(1)で表される縮合多環芳香族チオールが存在することを特徴とする有機薄膜トランジスタ。

【化1】

式(1)中、R1、R2、R3、R4、R5、R6、R7、R8は、各々独立に水素、アルキル基、アルケニル基、アルコキシル基、エーテル基、ハロゲン基、ケトン基、エステル基、アミノ基、アミド基、シアノ基、シリル基、およびこれらの基から構成される誘導基から選ばれる置換基であり、nは0〜5の整数、mは0〜12の整数である。尚、n、mが2以上の場合のR1、R2、R7、R8は各々が独立に上記置換基から選ばれる。

(もっと読む)

表示装置

【課題】MoあるいはMo合金から成る導電層上に塗布型絶縁膜を塗布したときに、導電層の表面に生じるMo酸化物層により発生するコンタクト不良や、膜はがれを防止する。

【解決手段】第1の基板を有し、前記第1の基板は、MoあるいはMo合金層で構成される第1導電層と、前記第1導電層よりも上層に形成される塗布型絶縁膜とを有する表示装置(例えば、液晶表示装置)であって、前記第1導電層上に形成され、AlあるいはAl合金層(または、TiあるいはTi合金層)で構成される第2導電層を有し、前記塗布型絶縁膜は、前記第2導電層上に形成される。

(もっと読む)

電子素子

【課題】製造コストが低く高速応答性の良好な電子素子を提供することを課題とする。

【解決手段】基板1の上にライン状の第1電極の上面2aに絶縁層3を形成する。この絶縁層3は、電極層2を形成するためのエッチング処理で用いるレジストを除去せずに残したものである。電極層2の側面2bから、絶縁層3の上面を経て、電極層2の側面2cにわたって、絶縁層4を形成する。絶縁層4の上には導電層5を形成する。電極層2の側面2bの側の絶縁部Bに平面視隣接して電極層6を形成し、同様に側面2cの側に電極層7を形成する。絶縁部Bを覆う領域に半導体層8を形成する。絶縁部Aの比誘電率及び膜厚は、この絶縁部Aを絶縁部Bと同一の膜厚及び同一の比誘電率を有する絶縁層で構成した場合よりも静電容量が小さくなるように設定する。

(もっと読む)

薄膜トランジスタ、電気光学装置および電子機器

【課題】信頼性に優れた薄膜トランジスタ、当該薄膜トランジスタを備える電気光学装置および電子機器を提供する。

【解決手段】本実施形態に係る薄膜トランジスタ1は、平面的に対向して配置されたソース電極3およびドレイン電極4と、少なくともソース電極3およびドレイン電極4の間に設けられた有機半導体層5と、ソース電極3、有機半導体層5およびドレイン電極4に跨って延在する複数本のゲート線7と、ソース電極3、ドレイン電極4および有機半導体層5と、各ゲート線7との間に介在するゲート絶縁層と、を有する。

(もっと読む)

181 - 200 / 303

[ Back to top ]