Fターム[4M104GG11]の内容

Fターム[4M104GG11]に分類される特許

121 - 132 / 132

半導体装置およびその製造方法

【課題】 第1導電型領域とよりも第2導電型領域とのほうが低いコンタクト抵抗率となる金属材料を用いて第1導電型領域の接点を形成することができる半導体装置およびその製造方法を提供する。

【解決手段】 周辺半導体領域5の不純物の濃度値よりも高い濃度値のp型不純物を含むp型領域5と、周辺半導体領域5の不純物の濃度値よりも高い濃度値のn型不純物を含み、p型領域1と重複するように位置するn型領域2と、少なくともn型領域2上に位置する金属層3とを備える。

(もっと読む)

窒化物系半導体デバイス

【課題】 動作特性の温度依存性が小さく、窒化物系半導体デバイスの高温動作が可能であるという特徴を生かすことのできる窒化物系半導体デバイスを実現する。

【解決手段】少なくとも一組の窒化物系半導体層のヘテロ接合5と少なくとも2つの電極Eからなり、前記一組の半導体層を構成する一の半導体層中に発生する2次元電子ガス層6を走行するキャリアが前記2つの電極の間を流れる電流となる窒化物系半導体デバイスにおいて、前記電極のコンタクト抵抗の温度依存性が負であることを特徴とする窒化物系半導体デバイス。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 黒鉛の析出を低減でき、かつ、SiC基板とオーミック電極との接触抵抗を充分に低減することができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】 SiC基板1と、SiC基板1にオーミック接触しているオーミック電極2とを有する半導体装置10であって、オーミック電極2が、SiC基板1上に配置されているシリサイド(NiSi)2eと、シリサイド2e上に配置されている第1のNi層2aと、第1のNi層2a上に配置されているTi層2bと、Ti層2b上に配置されておりNi2d1とSi2d2とを含んでなるNi/Si層2dと、Ni/Si層2d上に配置されている第2のNi層2cとを有してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 短絡不良の発生を抑え、信頼性に優れた半導体装置の構造を提供する。

【解決手段】 トレンチ15に充填する絶縁用酸化膜30を、n+ソース領域12よりも上まで形成し、この絶縁膜30の開口部においてのみ、金属またはシリサイド膜をn+ソース領域12とオーミック接触させソース電極221を形成する。また、ユニットの長手方向におけるソース配線22の端部とソース領域12の端部の距離dをソース配線22の厚さTswの2倍以上とする。

【効果】 ソース/ゲート間の短絡を防止し、歩留り向上によりコストを低減し、冷却系及びシステムサイズを小型化した。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲートバイアス下でソースとドレイン間の印加電圧(Vds)に対するドレイン電流(Ids)の特性で定義されるしきい値電圧(Vth)を実際に測定しながらゲート領域の追い込み拡散を行うことが可能で、これにより高精度に諸特性が制御された半導体装置を得ることが可能な半導体装置を提供する。

【解決手段】表面側に活性領域1acを備えた半導体基板1上に、活性領域1acに対してオーミック接続させた状態で高融点金属からなるソース電極7sおよびドレイン電極7dを形成する。ソース電極7s−ドレイン電極7d間における活性領域1acの表面層にp型不純物を拡散させてゲート領域9bを形成する。ソース電極7s、ドレイン電極7d、ゲート領域9bに連続して形成されたp型のパッド領域10bに端子を接続させ電気的特性を測定する。

(もっと読む)

半導体装置

【課題】基板強度を保持しつつオン抵抗を低減し得る半導体装置を提供する。

【解決手段】網目状の凸部により形成された複数の凹部を裏面に有し、第1の不純物濃度を有する半導体からなる支持体21と、前記支持体の前記裏面に対向する表面に形成され、前記第1の不純物濃度よりも低い第2の不純物濃度を有する半導体層3と、前記半導体層3に形成された半導体素子とを具備することを特徴とする。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスが、記述される。電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 低オン抵抗化を実現し、高速スイッチングが可能なJFETやSITなどの炭化珪素半導体装置を提供する。

【解決手段】 トレンチ溝110〜113に沿って形成したゲート領域13間のチャネルに拡がる空乏層により電流をオンオフするJFETやSITにおいて、半導体基体表面あるいはトレンチ溝113の底部に、外部より電圧が供給可能なゲートコンタクト層102とゲート電極103を設け、これとは独立し、トレンチ溝110〜112の底部で、ゲート領域13のp++コンタクト層14にオーミック接触するメタル導電部(仮想ゲート電極)101を設ける構造とした。この仮想ゲート電極101は、ゲート電極103や外部配線とは絶縁された形となる。

【効果】 ゲート抵抗を小さくし、高速スイッチング動作が可能な大電流容量の炭化珪素半導体装置を得ることができる。

(もっと読む)

窒化物系半導体装置

【課題】高耐圧/低オン抵抗の窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体装置は、窒化物系半導体から実質的になる第1半導体層1と、第1半導体層上に配設されたノンドープ若しくは第1導電型の窒化物系半導体から実質的になる第2半導体層2と、を有する。第1及び第2半導体層はヘテロ界面を形成する。第2半導体層上にゲート電極11が配設される。ゲート電極を間に挟むように第2半導体層の表面内に第1及び第2トレンチ3、4が形成される。第1及び第2トレンチの表面内に、第1及び第2半導体層よりも低抵抗の拡散層から実質的になる第1導電型の第3及び第4半導体層5、6が形成される。第3及び4半導体層にソース電極15及びドレイン電極16が電気的に接続される。

(もっと読む)

静電容量及びスイッチング損失が低減したショットキーダイオード構造及びその製造方法

基板及び2以上のエピタキシャル層を含んだSiCショットキーバリアダイオード(SBD)が提供され、該エピタキシャル層は少なくとも薄い低濃度にドーピングされたN型頂部エピタキシャル層、及び最高位のエピタキシャル層が配置されるN型エピタキシャル層を有している。多数のエピタキシャル層がダイオードの阻止電圧を支え、該多数のエピタキシャル層の各々が阻止電圧の大部分を支える。少なくとも頂部の2つのエピタキシャル層の厚さ及びドーパント濃度を最適化することによって、結果的に順方向電圧及びオン抵抗への影響を低く維持しつつ静電容量及びスイッチング損失が低減する。代替案として、SBDは連続的に濃淡がつけられたN型ドーピング領域を有し、かかるドーピングは領域の頂部における低ドーパント濃度から底部における高ドーパント濃度に向けて変化している。  (もっと読む)

(もっと読む)

有機機能素子、有機EL素子、有機半導体素子、有機TFT素子およびそれらの製造方法

【課題】 有機EL素子や有機TFT素子等の有機機能素子において、有機材料層への電極形成において蒸着を用いる必要が無く、また、折り曲げても断線しない信頼性の高い有機機能素子及びその製造方法を提供する。

【解決手段】 少なくとも複数の電極と有機材料層から構成される有機機能素子であって、該電極の少なくとも一つが液体金属で形成されている。

(もっと読む)

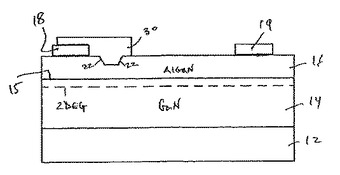

III族窒化物電流制御デバイスおよび製造方法

III族窒化物デバイスが、名目上オフ、すなわち、エンハンスメントモードのデバイスを作製するための凹部電極を含む。凹部電極を設けることによって、デバイス中の電流の流れを阻止するために、電極が非能動であるときに2つのIII族窒化物材料の境界面に形成された導電チャネルが中断される。電極はショットキー接点または絶縁金属接点であり得る。名目上オフの特性を有する整流器デバイスを形成するために、2つのオーム接点を設けることができる。電極が形成された凹部は傾斜側面を有することができる。電極は、デバイスの電流運搬電極と組み合わせて幾つもの幾何学配置で形成可能である。電極が凹部でないとき、名目上オンのデバイス、すなわち、ピンチ抵抗が形成される。ダイオードは、絶縁体を貫通してAlGaN層に達する非凹部のオーム接点およびショットキー接点を設けることによっても形成される。  (もっと読む)

(もっと読む)

121 - 132 / 132

[ Back to top ]