Fターム[4M104GG11]の内容

Fターム[4M104GG11]に分類される特許

41 - 60 / 132

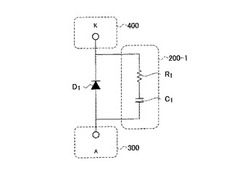

半導体装置及び電力変換装置

【課題】還流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタと抵抗を有する半導体スナバ回路200と、から構成され、半導体スナバ回路中200のキャパシタが、還流ダイオードDの遮断状態において、還流ダイオードDにより空乏層が形成される前記半導体基体中の領域とは異なる位置に形成されるので、還流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置

【課題】並列接続された還流ダイオードと半導体スナバ回路が隣接して配置されるので、小型化され且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置を提供する。

【解決手段】ユニポーラ動作する還流ダイオード100と、少なくともキャパシタ210及び抵抗220を有し、還流ダイオード100と並列接続されて還流ダイオード100に隣接して配置された半導体スナバ回路200とを備える。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200と還流ダイオード100とが積層されている。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に接続されたユニポーラ型の還流ダイオード150と、還流ダイオード100に並列接続され、少なくともキャパシタ210と抵抗220とを有する半導体スナバ200、及び、還流ダイオード150に並列接続され、少なくともキャパシタ260と抵抗270とを有する半導体スナバ250が形成された基板領域11を有する半導体チップ1000とを備えている。

(もっと読む)

半導体装置

【課題】、環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200は、キャパシタ210または抵抗220と接続される第1電極13と、第1電極13と絶縁されつつ、第1電極13と同一主面上に形成されて、キャパシタ210または抵抗220と接続される第2電極14とを有する。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

炭化珪素半導体装置

【課題】オーミック電極の接触抵抗を低減するとともに高い耐圧特性を実現することが可能な炭化珪素半導体装置を提供する。

【解決手段】半導体装置1は、基板2と不純物層としてのp+領域25とを備える。基板2は炭化珪素からなり、転位密度が5×103cm−2以下であって、導電型は第1導電型(n型)である。p+領域25は、基板上に形成され、前記第1導電型とは異なる第2導電型の導電性不純物濃度が1×1020cm−3以上5×1021cm−3以下である。

(もっと読む)

半導体デバイス用裏面電極、半導体デバイスおよび半導体デバイス用裏面電極の製造方法

【課題】剥離を十分に抑制することができ、さらには低抵抗でもあって特性に優れた半導体デバイス用裏面電極、その半導体デバイス用裏面電極を含む半導体デバイスおよびその半導体デバイス用裏面電極の製造方法を提供する。

【解決手段】半導体上のニッケルシリコン合金層またはニッケル層とシリコン層との積層体を加熱して形成されたニッケルシリサイド層と、ニッケルシリサイド層上に設置されたチタン層と、チタン層上に設置された金属層とを含み、金属層は、ニッケル層、白金層、銀層、金層、ニッケル層と銀層との積層体、およびニッケル層と金層との積層体からなる群から選択される少なくとも1種である、半導体デバイス用裏面電極、その半導体デバイス用裏面電極を含む半導体デバイスおよびその半導体デバイス用裏面電極の製造方法である。

(もっと読む)

ガードリング構造およびその製造方法

半導体素子用のガードリング構造。ガードリング構造は、第1層および第1層の上面に第2層を有する半導体積層体と、第1層内に形成されたゲート構造と、第1層内に形成されたガードリングとを有する。第2層は、第1層のドーパント濃度よりも高いドーパント濃度を有する。ゲートおよびガードリングは、単一のマスクを用いて同時に形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置の性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11と、このSiC基板11上に形成されたAlGaN層13と、このAlGaN層13上にそれぞれ離間して形成されたソース電極15及びドレイン電極14と、これらのソース電極15、ドレイン電極14間に形成され、ソース電極15及びドレイン電極14に対して平行な開口部16を有する絶縁膜17と、この絶縁膜17の開口部16に形成されたゲート電極18と、このゲート電極18のドレイン電極14側にゲート電極18と一体形成され、ドレイン電極14側端部191が絶縁膜17と離間したドレイン側フィールドプレート電極19とを具備する半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置の性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11と、このSiC基板11上に形成されたAlGaN層13と、このAlGaN層13上にそれぞれ離間して形成されたソース電極15及びドレイン電極14と、これらのソース電極15、ドレイン電極14間に形成され、ソース電極15及びドレイン電極14に対して平行な開口部16を有する第1の絶縁膜17と、この第1の絶縁膜17の開口部16に形成されたゲート電極18と、このゲート電極18が形成された第1の絶縁膜17上に形成された第2の絶縁膜19と、この第2の絶縁膜19及びソース電極15上に形成され、ドレイン電極14側の端部201が、第2の絶縁膜19と離間したソースフィールドプレート電極20と、を具備する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】高出力を得やすい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体装置は、基板100と、基板100上に形成された化合物半導体層110と、化合物半導体層110を用いて作製されたトランジスタ120と、基板100の裏面から化合物半導体層110の厚さ方向の途中まで除去された除去領域130と、除去領域130に埋め込まれ、前記基板より高い熱伝導度を有する高熱伝導性絶縁体131とを備えるものである。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】p型コンタクト抵抗を低減でき、素子のスイッチングスピードを下げないようにすることができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6のうち第1〜第3コンタクトホール12〜14から露出した部位に、炭化珪素とAlとNiとが反応してそれぞれ形成された合金層15が設けられている。この合金層15におけるAlとNiとの元素組成比は1:4.6〜1:10.6であり、合金層15の厚さは20nm以上100nm以下になっている。これにより、合金層15と半導体基板6とがオーミック接触となり、低いコンタクト抵抗率を得ることが可能となる。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたMIS構造HFETにおいて、ゲートリーク電流をより効果的に低減し、また、大きなゲート電圧の印加に際してのデバイス信頼性の向上も可能とする、MIS構造HFETを実現すること。

【解決手段】窒化物半導体1とゲート電極3との間にゲート絶縁膜を有するヘテロ構造電界効果トランジスタにおいて、前記ゲート絶縁膜は、窒化物半導体1に近い側の第1の絶縁膜6と、ゲート電極3に近い側の第2の絶縁膜7とを構成要素とし、第1の絶縁膜6が、HfO2、HfAlO、HfON、ZrO2を例とする、誘電率が20以上の絶縁物からなる厚さ4nm以上200nm以下の絶縁膜であり、第2の絶縁膜7が、SiO2またはAl2O3からなる厚さ2nm以上かつ第1の絶縁膜6の膜厚以下の絶縁膜であることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

半導体装置

【課題】コンパクトで製造コストの低い半導体装置を提供する。

【解決手段】半導体装置1は、基板5と、JFETと、裏面電極28と、整流素子構造(裏面コンタクト電極27とn型層12との接合部に形成されるSBD)とを備える。JFETは、基板5の表面側に形成され、ソースおよびドレイン領域9、10の間で基板5の表面に沿った方向に電流を流す。JFETは、ソースおよびドレイン領域9、10のいずれか一方と接続されたソース電極2またはドレイン電極4を含む。裏面電極28は基板5の表面と反対側の裏面側に形成される。SBDは、ソース電極2またはドレイン電極4と裏面電極28との間に形成される。

(もっと読む)

半導体装置

【課題】電界集中を緩和し耐圧を向上しつつ、電流コラプスを低減しかつリーク電流を減少することができる半導体装置を提供する。

【解決手段】半導体装置1において、窒化物系半導体2上に互いに離間して配設された制御電極5及び第2の主電極4と、窒化物系半導体2上の制御電極5と第2の主電極4との間に配設された第1の絶縁体6と、制御電極5に一端が電気的に接続され、他端が第1の絶縁体6上において制御電極5と第2の主電極4との間に配設された第1のフィールドプレート5FPと、第1の絶縁体6上において一端が第1のフィールドプレート5FPに接続され、他端が第2の主電極4に向かって延伸され、第1のフィールドプレート5FPに比べて高いシート抵抗を有する抵抗性フィールドプレート7とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】Alを含む窒化物半導体に対して、より低いコンタクト抵抗が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板と、前記基板の上に設けられた窒化物半導体からなる第1の半導体層と、前記第1の半導体層の上に設けられ、前記第1の半導体層よりもアルミニウムの濃度が高い窒化物半導体からなる第2の半導体層と、前記第2の半導体層の上に設けられた電極と、を備え、前記第2の半導体層に複数の孔が形成され、前記複数の孔のそれぞれは、前記電極と同種の材料により充填されてなることを特徴とする半導体装置を提供する。

(もっと読む)

41 - 60 / 132

[ Back to top ]