Fターム[4M104GG11]の内容

Fターム[4M104GG11]に分類される特許

101 - 120 / 132

半導体素子

【課題】III族窒化物を用いて構成される特性の優れた電界効果トランジスタ素子を提供する。

【解決手段】電界効果トランジスタ素子において、ゲート部の構造をショットキー接触型に代えて、n−GaNからなるn型導電層2bとBドープ多結晶Siにて形成したp型導電領域である第2半導体層3aとのP−N接合を有する接合ゲート型とする。これにより、逆方向ゲートリーク電流が十分に抑制された半導体素子を得ることができる。p型導電領域を有することで、ショットキー接触の場合に比してn型導電層内の空乏領域と、最大ゲート印加電圧を規定する拡散電位とが大きくなるので、オン特性の優れたノーマリーオフ型の半導体素子を得ることができる。半導体素子をHEMT構造とし同様のゲート部の構造を設けた場合も、同様の効果を得ることができる。

(もっと読む)

III族窒化物半導体装置

【課題】 p型のIII族窒化物半導体の表面に、n型またはi型のIII族窒化物半導体を結晶成長するとともに、n型またはi型のIII族窒化物半導体の一部をエッチングしないでp型のIII族窒化物半導体の表面を露出させる

【解決手段】 p型の不純物を含む第1のIII族窒化物半導体領域28の表面の一部に不純物拡散防止膜36を備えている。第1のIII族窒化物半導体領域28と不純物拡散防止膜36を介して向かい合う位置に、n型の不純物を含むかまたはi型の第2のIII族窒化物半導体領域44を備えている。また、第1のIII族窒化物半導体領域28と不純物拡散防止膜36を介さないで向かい合う位置に、p型の不純物を含む第3のIII族窒化物半導体領域30を備えている。

(もっと読む)

自己整合ゲートJFET構造及びその製造方法

少なくとも半導体層を有する基板に一体化されたJFETは、アクティブ領域上にあり且つ第1のポリシリコン(又は、高融点金属又はシリサイド等のその他の導電体)から成るソースコンタクト及びドレインコンタクトと、ソースコンタクト及びドレインコンタクトの頂部を覆う誘電体層の頂面と同一平面になるように研磨された第2のポリシリコンから成る自己整合ゲートコンタクトとを有する。上記誘電体層は好ましくは、研磨停止層として作用する窒化物キャップを有する。一部の実施形態においては、ソースコンタクト及びドレインコンタクトを覆う誘電体層と、当該JFETのアクティブ領域を画成するフィールド酸化物領域との全体が窒化物で覆われる。エピタキシャル成長されたチャネル領域が基板表面に形成される一実施形態も開示される。  (もっと読む)

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】トレンチ構造のJ−FETが形成されるセル領域の一部に、ダイオードを内蔵する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】炭化珪素半導体で構成されたN+型ドレイン層11、N−型ドリフト層12およびN+型ソース層13が下から順に配置されている半導体基板1と、ソース層13の表面からドリフト層12に到達する深さのトレンチ14の側面14aに沿って配置されたP型ゲート層15と、トレンチ14の内部でゲート層15を覆う絶縁膜17と、ソース層13と電気的に接続されたソース電極19とを備える炭化珪素半導体装置において、少なくともトレンチ14の内部もしくは真下に、ソース電極19と電気的に接続され、ドリフト層12と接合してダイオード6を構成するショットキー電極18もしくはP型層のダイオード構成部を設ける。

(もっと読む)

静電誘導型トランジスタおよびその製造方法

【課題】小コンタクト面積のn+型の低抵抗層への効率よい接触と、ソース、ゲートのコンタクト部のコンタクト抵抗の減少と、リセス部側面の引上配線の断線の補修とが可能な静電誘導型トランジスタの提供。

【解決手段】エピタキシャル成長層にリセス構造を形成し、ゲート電極を形成する工程とエピタキシャル成長層の絶縁膜の開口部にソース電極を形成する工程と半導体基板の反対側にドレイン電極を形成する工程とを含む静電誘導型トランジスタの製造方法において、前記ゲート領域に低抵抗化された多結晶シリコン層を減圧化学気相堆積法で形成する工程とゲート電極形成工程と減圧化学気相堆積法で堆積酸化膜を形成する工程とを介在させた後に、ゲート引出し金属電極を設ける工程を設け、前記ソースの領域に、低抵抗化された多結晶シリコン層を減圧化学気相堆積法で成膜する工程とソース電極形成工程とを介在させた後にソース引出し金属電極を設ける工程を設けた。

(もっと読む)

金属性の制御電極を有する半導体素子を製造する方法、および半導体素子

【課題】本発明の課題は、ゲート長が小さくても有利かつ長時間安定性の特性を有する、III‐V族化合物半導体基板をベースとする半導体素子の製造方法および半導体素子を提供することである。

【解決手段】前記課題は、半導体層上のゲート電極の第1の層をアルミニウムから形成し、第1の層上に、第2の金属から成る第2の層を堆積し、該第2の金属は、後続の該熱処理で該第1の層のアルミニウムの粒度の成長を制限するものであり、該第2の金属と異なる別の金属を、少なくとも1つの別の層で該第2の層に沈着する

ことを特徴とする方法によって解決される。

(もっと読む)

半導体装置およびその製造方法

【課題】低損失の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、ワイドギャップ半導体層1と、ワイドギャップ半導体層1に形成されたSBD(ショットキーバリアダイオード)60とを備えている。SBD60はワイドギャップ半導体層1の一方の主面に接するように形成されたショットキー電極4と、ワイドギャップ半導体層1の他方の主面に接するように形成されたカソード電極6とを有しており、かつショットキー電極4からカソード電極6へ流れる電流を制御可能である。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】十分に大きな電流密度を得ることができるノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】基板601上にAlNバッファ層602、アンドープGaN層603、アンドープAlGaN層604、第1のp型AlGaN層605、第2のp型AlGaN層607、高濃度p型GaN層608が順に形成され、ゲート電極611が高濃度p型GaN層608とオーミック接合する。アンドープAlGaN層604上にはソース電極609及びドレイン電極610が設けられる。アンドープAlGaN層604とアンドープGaN層603との界面で発生する2次元電子ガスと第1のp型AlGaN層605および第2のp型AlGaN層607とによって生じるpn接合がゲート領域に形成される。また、第2のp型AlGaN層607はSiN膜606の一部を覆う。

(もっと読む)

電界効果トランジスタ、及び、同電界効果トランジスタの製造方法、及び、半導体装置、及び、同半導体装置の製造方法

【課題】オン抵抗の増大を防止しつつ、ゲート−ドレイン間の寄生容量を低減することができる電界効果トランジスタ、及び、同電界効果トランジスタを備えた半導体装置、及び、これらを製造する方法を提供する。

【解決手段】基板上に設けた半導体層上に、ゲート電極とソース電極とドレイン電極とを備えた電界効果トランジスタを有する半導体装置の製造方法において、前記電界効果トランジスタを形成する際に、ゲート電極とドレイン電極との間における半導体層上に金属電極を形成することにより、金属電極と半導体層の界面にショットキー接合を形成することとした。

(もっと読む)

半導体装置

【課題】 生産コストの削減並びに接触抵抗及び寄生容量の低減を実現する半導体装置を作製する。

【解決手段】 第1領域、第2領域、及びそれらを分離する所定の高さの第3領域からなる主表面を有する第1半導体層50と、第1半導体層50上に形成され、それとは異なる格子定数を持つ第2半導体層52とを含み、第1半導体層50及び第2半導体層52の第3領域部分は、第1領域との境界に第1凹凸部及び第2領域との境界に第2凹凸部を有し、さらに、第1半導体層50上の第1領域と第3領域との境界部分に第1凹凸部と相補的な形状を持つ側部を有する第1電極56と、第1半導体層50上の第2領域と第3領域との境界部分に第2凹凸部と相補的な形状を持つ側部を有する第2電極58とを含む。

(もっと読む)

低電力接合型電界効果トランジスタの製造方法及び作動方法

小さい線幅を有する一対の相補型接合型電界効果トランジスタ(CJFET)を含むインバータを使用する方法が提供される。この方法は、CJFETインバータの入力キャパシタンスを、同等の線幅のCMOSインバータの対応する入力キャパシタンスより小さくさせることを含んでいる。CJFETは、順バイアスされたダイオードの電圧降下より低い値を有する電源電圧で動作し、CMOSインバータと比較して低減されたスイッチング電力を有する。CJFETインバータの伝搬遅延は、CMOSインバータの対応する遅延に対して少なくとも同等である。  (もっと読む)

(もっと読む)

窒化物半導体電界効果トランジスタ及びその製造方法

【課題】窒化物化合物半導体を用いた電界効果トランジスタにおいて、チップ面積が小さく高耐圧動作が可能とする。

【解決手段】n+型GaN基板上にn-型GaN層にn+型InAlGaN 4元コンタクト層が形成され、このn-型GaN層上及びn+型コンタクト層はその上に形成されたWSiソース電極に庇が形成される形で選択的にエッチングされており、このソース電極をマスクとしてゲート電極がセルフアライン工程にて形成されている。ここで寄生容量低減の低誘電率を有するベンゾシクロブテン(BCB)膜が前記電流が流れる領域の側部を埋める形で形成されていても、例えばa面などのいわゆる無極性面上にて窒化物半導体層が形成された形でも良い。

(もっと読む)

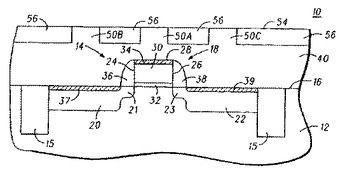

犠牲マスキング構造を用いた半導体装置の製造方法

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】実用化に適した高機能のMISFETやダイオードなどの炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】4H−SiC基板10の上にエピタキシャル成長層11を成長させた後、イオン注入を行なって、イオン注入層であるpウェル領域12,ソース領域13,p+コンタクト領域15を形成する。その後、pウェル領域12,ソース領域13,p+コンタクト領域15の上にカーボンキャップ17を形成した状態でイオン活性化アニールを行い、カーボンキャップ17を除去してから、CMPにより基板の最表面を、平均表面粗さ0.1nm〜0.5nm程度まで研磨する。

(もっと読む)

多孔薄膜堆積基板、その製造方法及びスイッチング素子

【課題】孔径、孔の密度が自由に制御でき、安価で簡便であり、有機化合物半導体にも適用が可能な低温で製造される、多孔薄膜堆積基板を提供する。さらには、この方法により得られた多孔薄膜堆積基板を利用して、均一で十分に小さいゲート孔を有し、動作電圧が低く、周波数特性にすぐれ、スイッチング特性が良好なスイッチング素子及びその製造方法を提供する。

【解決手段】表面に静電荷を有する基板表面上に、前記基板表面の静電荷と逆の表面静電荷を付与した微粒子を設置させ、該微粒子設置基板上に少なくとも1層の薄膜を堆積した後、該微粒子を除去し、前記基板上に微細多孔を形成することを特徴とする多孔薄膜堆積基板。

(もっと読む)

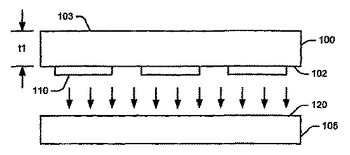

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

炭化ケイ素半導体デバイスを形成するいくつかの方法が開示される。これらの方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、炭化ケイ素基板の第1の表面にキャリア基板を取り付けるステップとを含む。キャリア基板は、炭化ケイ素基板に機械的支持を提供する。これらの方法はさらに、炭化ケイ素基板を、第1の厚さ未満の厚さまで薄くするステップ、炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、および炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面にオーミックコンタクトを形成するために、金属層を局所的にアニールするステップを含む。炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。  (もっと読む)

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

本発明は、半導体基材(100)を有する半導体素子に関し、さらに以下の各特徴として、上記半導体基材(100)内にて、第1の伝導型のドリフト領域(2;211)と、上記半導体基材(100)内にて、上記ドリフト領域(2)に対し、少なくとも部分的に隣り合って配置され、半導体材料からなるドリフト制御領域(3;241)と、上記ドリフト領域(2;211)と上記ドリフト制御領域(3;241)との間に配置された蓄積誘電体(4;251)とを含む。  (もっと読む)

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】 半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

101 - 120 / 132

[ Back to top ]