Fターム[4M104GG13]の内容

Fターム[4M104GG13]の下位に属するFターム

Fターム[4M104GG13]に分類される特許

41 - 60 / 87

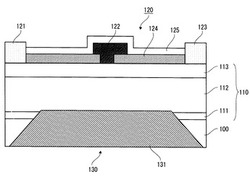

半導体装置及びその製造方法

【課題】高出力を得やすい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体装置は、基板100と、基板100上に形成された化合物半導体層110と、化合物半導体層110を用いて作製されたトランジスタ120と、基板100の裏面から化合物半導体層110の厚さ方向の途中まで除去された除去領域130と、除去領域130に埋め込まれ、前記基板より高い熱伝導度を有する高熱伝導性絶縁体131とを備えるものである。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することを可能にする。

【解決手段】配列された複数の素子形成領域AR1を含むp型半導体層103における隣り合う素子形成領域AR1間に平行な2つの溝TRを形成し、個片化時には2つの溝TRの間に形成された凸部120を切断する。この構成により、スクライブ領域SR全体に溝TRを形成する必要が無くなるため、溝TRの幅を例えばダイシングブレードの厚さやレーザスポットの径よりも小さくすることが可能となる。この結果、微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することが可能となる。

(もっと読む)

集積低漏洩ショットキーダイオード

MOSゲートの一方の側部に近接しているショットキーバリアを有し、当該ゲートの他方の側部にドリフト領域の一端を有する集積低漏洩ショットキーダイオードである。ショットキー金属及びゲート酸化膜の下は、P層とそれを覆うN層のリサーフ構造であり、当該リサーフ構造がドリフト領域を形成し、当該ドリフト領域は本発明の1つの実施例においてダイオードのカソードで終端する。当該N層及びP層は、当該ゲートの下に上向きに凸の凹形状を有する。ゲート電極及びショットキー金属は、ダイオードのアノードに接続されている。P層が当該リサーフ構造とNISO領域との間にあり、NISO領域が当該アノードとの電気的接続を有している。ショットキー金属の下のP+層は、Pウェルを通してP−層と接続されている。  (もっと読む)

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド化の工程をMOSトランジスタ及びHBTと別けることなく、抵抗値のばらつきが小さいヒューズ素子を形成する半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、MOSトランジスタ形成領域11Bにゲート電極22及びソースドレイン領域25を形成する工程と、MOSトランジスタ形成領域11Bを除いて、半導体基板11の上にシリコン及びシリコン以外のIV族元素を含む混晶膜と、シリコン膜とが順次積層された積層膜31A、31Bを形成する工程と、シリコン膜30Bの露出部分、ゲート電極22の上部及びソースドレイン領域25の上部をシリサイド化する工程とを備えている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】コンタクトホールを容易且つ確実に効率よく形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】水素バリア膜7に、配線層9と、MOSトランジスタTのゲート電極3、ソース電極及びドレイン電極とを接続する第一のコンタクトホールH1を通すための除去領域7Aを形成し、この除去領域7Aの内側に、第一のコンタクトホールH1を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーメタルが1種類でありながらも、使用用途に応じた順方向特性、逆方向特性を発現するショットキーバリアダイオードを提供する。

【解決手段】第1導電型の半導体層2を表面に備えた半導体基板1と、半導体層2の表面から層内に延びる第2導電型の半導体領域からなるガードリング6と、ガードリング6で囲まれた半導体層表面に形成された金属層4とでショットキー接合領域を形成した半導体装置であって、ショットキー接合領域は金属層4と半導体層2との間に共晶層が形成された共晶領域7と、共晶領域7で囲まれ、金属層4と半導体層2との間に絶縁膜パターン5が介在し、共晶領域よりも共晶厚さが薄い共晶領域とを含む。

(もっと読む)

高電子移動度トランジスタおよび電子デバイス

【課題】大きな振幅の入力信号に対して歪みの小さい出力信号が得られ、大きな絶対値の制御信号をゲート電極に印加した場合のゲートリーク電流の小さい、高電子移動度トランジスタを提供する。

【解決手段】基板と、基板の上層のバッファ層110と、バッファ層の上層のキャリア走行層130と、キャリア走行層との間にヘテロ接合を形成する第1キャリア供給層140と、第1キャリア供給層の上層に形成され第1キャリア供給層よりキャリア密度が低い第2キャリア供給層142と、を備える高電子移動度トランジスタを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】反りを低減し、ボンディング性能が高い外部接続(パッド)構造をもつ半導体装置を提供する。また、低コストで製造作業性が良好な外部接続構造をもつ半導体装置を提供する。

【解決手段】所望の素子領域の形成された半導体基板と、前記半導体基板表面に設けられた素子電極と前記素子電極の表面に形成されためっき層とを具備した外部接続用端子部と、前記外部接続用端子部の外部接続領域の周縁を覆うように形成された保護膜とを具備した半導体装置であって、前記外部接続領域において、前記めっき層が、分離領域を介して複数の領域に分離されたことを特徴とする。

(もっと読む)

有機トランジスタ及びアクティブマトリックス基板

【課題】寄生容量を均一にする。

【解決手段】本発明の有機トランジスタ100は、所定の長さLを有するゲート電極50と、ソース電極30及びドレイン電極60と、ソース電極30とドレイン電極60との間有機半導体部40と、有機半導体部40内のチャネル領域45と、を備えている。ドレイン電極60は、平面視した状態でその全体がゲート電極50に重ねられてなり、ドレイン電極60には、帯状の接続配線部61が一方の側Laに延びて接続されるとともに、幅が接続配線部61の2倍未満の帯状のダミー接続配線部62がゲート電極50の長さ方向における他方の側Lbに延びて接続されている。接続配線部61は、ゲート電極50の一方の側Laにおける端縁又は端縁よりも一方の側Laに延びてなり、かつダミー接続配線部62は、ゲート電極50の他方の側Lbにおける端縁又は端縁よりも他方の側Lbに延びてなる。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホールの形成に関連する歩留まりの低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】絶縁性基板1上にGaN層2及びn型AlGaN層3を形成し、その後、ゲート電極4g、ソース電極4s及びドレイン電極4dを形成する。次に、ソース電極4s、GaN層2及びn型AlGaN層3に、少なくとも絶縁性基板1の表面まで到達する開口部6を形成する。次いで、開口部6内にNi層8を形成する。その後、Ni層8をエッチングストッパとするドライエッチングを行うことにより、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを形成する。そして、ビアホール1s内から絶縁性基板1の裏面にわたってビア配線16を形成する。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

常時オフのVJFET集積電力スイッチを有するワイドバンドギャップ半導体デバイスが説明される。電力スイッチはモノリシック又はハイブリッドに実行され、シングル又はマルチチップワイドバンドギャップ電力半導体モジュール内に組み立てられた制御回路網と一体化される。デバイスは、高電力、耐高温および/または耐放射線性の電子工学の要素に用いられる。デバイスの作成方法もまた説明される。 (もっと読む)

改良された電力用スイッチングトランジスター

実施例によれば、半導体集積デバイスが、ソースとこのソースの各々の側部に配置されたゲートを有する第1の垂直接合電界効果トランジスター(Vertical Junction Field Effect Transistor: VJFET)と、ソースとこのソースの各々の側部に配置されたゲートを有する第2の垂直接合電界効果トランジスターを含む。第1の垂直接合電界効果トランジスター(VJFET)の少なくとも1つのゲートは、第2のVJFETの少なくとも1つのゲートから、チャンネルにより分離される。半導体集積デバイスは、更に、第1と第2のVJFETの間に配置された接合バリアーショトキー(Junction Barrier Schottky:JBS)ダイオードを含む。このJBSダイオードは、このチャンネルに対する整流コンタクトを構成し、かつ、第1と第2のVJFETの少なくとも1つのゲートに対する非整流コンタクトを構成する金属コンタクトを備え、この金属コンタクトが、このJBSダイオードのアノードである。第1の電気接続手段が、第1のVJFETのゲート、第2のVJFETのゲート、及び、JBSダイオードのアノードを、共通ゲート電極に連結し、及び、第2の電気接続手段が、第1のVJFETのソースと第2のVJFETのソースを、共通ソース電極に連結する。  (もっと読む)

(もっと読む)

薄膜トランジスタ素子およびその製造方法

【課題】薄膜トランジスタ素子を、フォトリソ工程の回数を少なくして製造することができるようにする。

【解決手段】薄膜トランジスタ素子は、基板の主表面1aに配置されたゲート電極層と、ゲート絶縁層と、第1の半導体層4と、これを覆うように配置される第2の半導体層と、上記ゲート絶縁層、第1の半導体層4および上記第2の半導体層を介して上記ゲート電極層の上側にそれぞれ配置されるソース電極層6aおよびドレイン電極層6bとを備える。ソース電極層6aおよびドレイン電極層6bは平面的に見てチャネル領域12を挟んで互いに対向している。ソース電極層6aとドレイン電極層6bとを結ぶ直線の方向71に垂直な方向をチャネル幅方向72としたとき、チャネル幅方向72に関するソース電極層6aとドレイン電極層6bとの対向する区間の幅は、チャネル領域12のチャネル幅方向の寸法Wchよりも長い。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】ソース/ドレイン電極と活性層が、少なくとも同じ種類のエッチャントによってエッチング可能な性質を有する材料である場合において、リフトオフ法を使用せず双方をそれぞれエッチングによってパターニングする方法を提供する。

【解決手段】ボトムゲート型トップコンタクト型の電界効果トランジスタの製造工程においては活性層パターン形成後に、またボトムゲート型ボトムコンタクト型の電界効果トランジスタの製造工程においてはソース/ドレイン電極パターン形成後に、耐酸性を有する遮光膜を一層設ける。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】高い拡散防止効果を備えながら応力の少ない電極を有する半導体素子及び、その半導体素子の製造方法を提供することを目的とする。

【解決手段】半導体素子51に形成する電極44を、熱処理を施してオーミック特性を付与する第1電極層30と、熱処理を施さない第2電極層36とに分けて形成することで、熱処理時に生じる応力を低減することができる。また、バリア層を第1バリア層26と第2バリア層28とに分けることで薄層化して、応力を低減するとともに、半田接合時には第1バリア層26と第2バリア層28との間に設けた中間層27を拡散消失させて、あたかも厚い1層のバリア層23として機能させることで、高い拡散防止効果を得ることができる。

(もっと読む)

ワイドバンドギャップデバイスのためのアバランシェ保護

本発明は、ワイドバンドギャップデバイスを電圧過渡の抑制の間の損傷から保護する方法及びデバイスである。アバランシェ耐量を向上させることは、ワイドバンドギャップデバイスのブロック接合部に1つ以上のダイオード又はPNPトランジスタを配置することにより達成される。  (もっと読む)

(もっと読む)

41 - 60 / 87

[ Back to top ]