Fターム[4M104GG13]の内容

Fターム[4M104GG13]の下位に属するFターム

Fターム[4M104GG13]に分類される特許

81 - 87 / 87

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

集積回路およびその製造方法

【課題】 ポリマー系有機半導体材料を用いたp型FETを用いて実用的集積回路を構成できるようにすること。

【解決手段】 集積回路を構成するトランジスタとしてp型FETのみを用いたものである。基本回路の例として(a)インバーター回路、(b)AND回路、(c)OR回路を示す。同図において、1〜12はp型FETである。p型FETだけで構成し、出力部にもp型FETのみを用いたソースフォロワ回路を用いたアナログアンプも可能である。

(もっと読む)

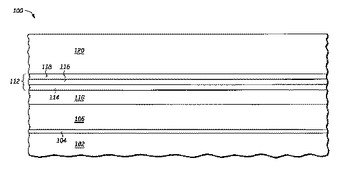

分離相補型マスクパターン転写方法

パターニング方法は、相補的なレチクルの組を個別に転写することを可能にする。一実施形態においては、例えば本方法では、位相シフトマスク(PSM)(112)をエッチングし、次にcPSMマスク(110)に対応するカットマスクをエッチングする。更に、分離相補型マスクパターン転写方法は2つの個別の、かつ分離されたマスクパターニング工程を含み、これらの工程では、像を最終ウェハパターニングの前に、複合パターンを、中間ハードマスク(112)に部分的に転写することにより形成する。中間ハードマスク材料(112)及び最終ハードマスク材料(110)は、像が最終エッチングプロセスの前に下層の基板(102)またはウェハに像が転写されることがないように選択される。  (もっと読む)

(もっと読む)

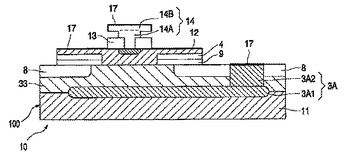

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

81 - 87 / 87

[ Back to top ]