Fターム[4M104GG13]の内容

Fターム[4M104GG13]の下位に属するFターム

Fターム[4M104GG13]に分類される特許

21 - 40 / 87

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】酸化物絶縁層上に膜厚が1nm以上10nm以下の第1の酸化物半導体層を形成し、加熱処理により結晶化させ、第1の結晶性酸化物半導体層を形成し、その上に第1の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を形成する。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセスの提供。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

トランジスタ基板及びトランジスタ基板の製造方法

【課題】ソース領域及びドレイン領域と、チャネル層との間で、良好な電気的接合を確保でき、かつオン電流の低下を防ぐことのできるトランジスタ素子及びその製造方法を提供する。

【解決手段】トランジスタ基板1は、基板100上に配置されたゲート電極200と、前ゲート電極200上に配置されたゲート絶縁膜310と、ゲート絶縁膜310上の、互いにゲート電極200を挟んで対向する位置に形成されたソース電極710及びドレイン電極720と、ソース電極710上に形成されたソース領域と、ドレイン電極720上に形成されたドレイン領域と、ソース領域上、ドレイン領域上、及びソース領域と前記ドレイン領域との間のゲート絶縁膜310上に配置され結晶性シリコンを含む半導体膜420と、を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域AA上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、窒化物系化合物半導体層12上に配置され、それぞれゲート電極24、ソース電極20およびドレイン電極22に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続された端面電極SC1〜SC4と、端面電極上に配置され、ダイボンディングで使用する半田層がソース端子電極SE1〜SE4に到達するのを防止する突起電極34とを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、ゲート電極、ソース電極およびドレイン電極が延伸する方向の窒化物系化合物半導体層上に配置され、それぞれゲート電極、ソース電極およびドレイン電極に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続され、最外層のエッジが下地金属層よりも後退する3層以上の異なる多層金属を有する端面電極SC1〜SC4とを備え、ダイボンディング半田層がソース端子電極に到達するのを防止する。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

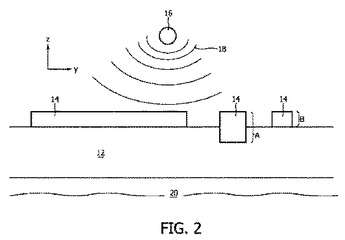

集積回路を製造する装置及び方法

本発明は、厚膜金属層14を有する集積回路10を製造する装置に関する。金属ペースト14の層は、熱伝導基板12上に適用手段24によって適用される。金属ペースト14は、予め決められたサイズの金属粒子を含む。RF生成器16は、金属ペースト14にRFエネルギー18を選択的に誘導結合させる。金属粒子を加熱するために、金属ペースト14の金属粒子の予め決められたサイズは、RFエネルギー18の結合周波数に対応する。このようにして、金属ペースト14の金属粒子は、従来のプロセスのパワーの何分の一かのパワーで、金属ペースト14を予備焼結する必要なく、加熱される。  (もっと読む)

(もっと読む)

半導体装置、電力変換装置及び半導体装置の製造方法

【課題】RCスナバ回路の抵抗Rの値を任意に設計可能な半導体スナバ回路を用いた半導体装置、電力変換装置、半導体装置の製造方法を提供する。

【解決手段】ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、キャパシタ210及び抵抗220をモノリシックに集積化した半導体スナバ回路200とを備える半導体装置において、抵抗220が、半導体スナバ回路200の基材となる半導体基体の一部に形成され、半導体基体の比抵抗よりも高い比抵抗を有する高抵抗層を含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置

【課題】ガードリングを越えて半導体チップ内に水分が浸入した場合でも、半導体チップ上の1つの電極と他の1つの電極との短絡を抑制すること。

【解決手段】半導体チップ10と、半導体チップ10上に配置された電極パッド14、16と半導体チップ10の外周との間に配置された導電性のガードリング18と、ガードリング18の一部領域を排することで、ガードリング18を互いに絶縁された複数の単位領域に分割するための、複数のガードリング絶縁部60と、を有する半導体装置。

(もっと読む)

無電解めっきによる有機薄膜トランジスタのソース及びドレイン電極の形成方法

溶液処理法を用いてソース及びドレイン電極を基板上に被着させるステップと、溶液処理法を用いて仕事関数改変層をソース及びドレイン電極上に形成するステップと、溶液処理法を用いて有機半導体材料をソース及びドレイン電極の間のチャネル領域に被着させるステップとを含む、有機薄膜トランジスタの製造方法。 (もっと読む)

半導体集積回路およびその製造方法

【課題】伝送線路の損失を低減することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路は、表面から裏面までを貫通するビアホール107が設けられたサファイア基板101と、サファイア基板101の表面に形成されたAlGaN/GaNエピタキシャル成長層102内の導電層をチャネルとするHFET106と、サファイア基板101の裏面に形成され、ビアホール107を介してHFET106と電気的に接続された入力側信号線109及び出力側信号線110と接地電極108とから構成されるコプレーナ型伝送線路とを備える。

(もっと読む)

半導体装置

【課題】高温の酸化性雰囲気中でのSOD膜の改質を促進する。ライナー膜下部の素子や半導体基板が酸化されてダメージを受けることを防止する。

【解決手段】凹部と、凹部の内壁側面上に順に形成した、第1のライナー膜と、酸素原子を含有する第2のライナー膜と、凹部内に充填された絶縁領域と、を有し、第1のライナー膜は第2のライナー膜よりも耐酸化性が優れるものとした半導体装置。

(もっと読む)

半導体装置

【課題】波形振動を抑制しスイッチング損失を低減した半導体装置を提供する。

【解決手段】第1半導体層と、前記第1半導体層の第1面の側に設けられた第1電極と、前記第1半導体層と前記第1電極との間に設けられ、前記第1半導体層と前記第1電極との間に流れる電流を狭窄する第1絶縁層と、前記第1絶縁層で狭窄された電流の経路上に少なくとも設けられ、前記第1半導体層に含有される不純物濃度よりも高い濃度で不純物を含有する第1導電型の第2半導体層と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

21 - 40 / 87

[ Back to top ]