Fターム[4M104HH04]の内容

Fターム[4M104HH04]に分類される特許

1 - 20 / 165

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

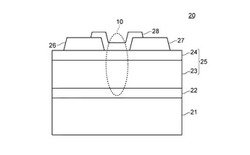

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】製造工程等で高温下に曝された場合であっても、半導体領域と電極との間での原子の相互拡散が抑制され、かつ界面抵抗の上昇が抑えられる半導体素子を提供すること、及びこのような半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、シリコンを含む半導体領域、アルミニウムを主成分として含む電極、及び上記半導体領域と電極との間に介在し、ゲルマニウムを含有する拡散防止層を備え、上記拡散防止層の少なくとも一部のゲルマニウム含有量が4原子%以上である半導体素子である。本発明の半導体素子の製造方法は、シリコンを含む半導体領域の表面に、ゲルマニウムを含むアルミニウム合金膜を形成する工程、及び上記アルミニウム合金膜が形成された半導体領域に熱処理を行う工程を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

1 - 20 / 165

[ Back to top ]