半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置においては、電界効果トランジスタの動作速度の遅延を抑えるために、ゲート電極を低抵抗化することがある。例えば、特許文献1には、プレーナ型の電界効果トランジスタにおける、導電性のシリコン膜を用いたゲート電極の形成方法が開示されている。特許文献1では、基板上にゲート絶縁膜を介して形成されたゲート電極となる非結晶シリコン膜に不純物イオン(例えば、nMISFETではPイオン、pMISFETではBイオン)を注入することで、ゲート電極を低抵抗化している。これにより、低抵抗化された導電性のシリコンをゲート電極に適用したプレーナ型の電界効果トランジスタを形成できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−7329号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

以下の分析は、本願発明者により与えられる。

【0005】

特許文献1のようにして不純物イオンを注入することで低抵抗化したシリコン膜をゲート電極に用いる技術を本願発明者らが検討したところ、以下のことが分かった。即ち、MISFETにおけるゲート電極直下にはキャリアがドリフトするチャネル領域が存在し、注入したイオンがこのチャネル領域に達すると、MISFETの電気特性に影響を与え、閾値電圧が変わってしまう。

【0006】

例えば、更なる微細化の技術動向にあってゲート電極自体を薄くする場合、注入される不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達し易くなる。

【0007】

また、例えば、ゲート電極の形成工程やその後の製造工程の条件によっては、成膜したシリコン膜(ゲート電極)の多結晶化によりシリコン膜(ゲート電極)の膜厚が局所的に薄くなる個所が生じ得、その個所では、注入される不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達し易くなる。

【0008】

さらに、例えば、注入された不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達した場合、熱処理を行うと、シリコン膜(ゲート電極)中の不純物イオンがゲート絶縁膜を透過してチャネル領域に拡散し易くなる。

【0009】

これらの点で、導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置には改善の余地がある。

【課題を解決するための手段】

【0010】

本発明の第1の視点においては、半導体装置において、半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有することを特徴とする。

【0011】

本発明の第2の視点においては、半導体装置の製造方法において、半導体基板の主面上に、絶縁膜を介してシリコンを主体とする第1シリコン膜を形成する工程と、前記第1シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層を形成する工程と、前記第1シリコン膜上に、前記介在層を介してシリコンを主体とする第2シリコン膜を形成する工程と、前記第1シリコン膜及び前記第2シリコン膜に対して、前記第2シリコン膜側から不純物イオンを注入する工程と、を含むことを特徴とする。

【発明の効果】

【0012】

本発明によれば、ゲート電極膜間(シリコン膜間)に配された介在層により、シリコン膜を導電化するために不純物イオンを注入する際、当該不純物イオンがシリコン膜下のチャネル領域にまで到達し難くなる。結果として、トランジスタの閾値電圧のばらつきを低減できる。

【図面の簡単な説明】

【0013】

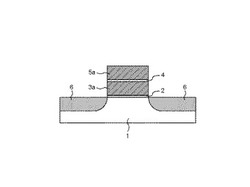

【図1】本発明の実施形態1に係る半導体装置の構成を模式的に示した断面図である。

【図2】本発明の実施形態1に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図3】本発明の実施形態1に係る半導体装置の製造方法を模式的に示した図2に続く工程断面図である。

【図4】本発明の実施形態2に係る半導体装置の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図5】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図6】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した図5に続く工程断面図である。

【図7】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した図6に続く工程断面図である。

【図8】本発明の実施形態3に係る半導体装置の構成を模式的に示した平面図である。

【図9】本発明の実施形態3に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図10】本発明の実施形態3に係る半導体装置におけるメモリセル領域の構成を模式的に示した(A)平面図、(B)Y−Y´間の断面図である。

【図11】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図12】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図11に続く工程断面図である。

【図13】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図12に続く工程断面図である。

【図14】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図13に続く工程断面図である。

【図15】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図14に続く工程断面図である。

【図16】本発明の実施形態4に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図17】本発明の実施形態4に係る半導体装置の製造方法を模式的に示した工程断面図である。

【発明を実施するための形態】

【0014】

[実施形態1]

本発明の実施形態1に係る半導体装置について図面を用いて説明する。図1は、本発明の実施形態1に係る半導体装置の構成を模式的に示した断面図である。

【0015】

図1を参照すると、半導体装置は、多結晶シリコンからなるゲート電極を有するプレーナ型の電界効果トランジスタを有する。

【0016】

電界効果トランジスタでは、半導体基板1(例えば、シリコン基板)の主面上にゲート絶縁膜2(例えば、シリコン酸化膜)を介して第1ゲート電極膜3aが形成されている。第1ゲート電極膜3aは、第1導電型となる不純物(例えば、Pイオン、Bイオン)を含んだシリコンを主体とする導電膜である。第1ゲート電極膜3a上には、介在層4が形成されている。介在層4は、第1ゲート電極膜3aと第2ゲート電極膜5aとの間に介在した層(例えば、絶縁層)であり、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層4上には、第2ゲート電極膜5aが形成されている。第2ゲート電極膜5aは、第1導電型となる不純物(第1ゲート電極膜3a中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。第1ゲート電極膜3a、介在層4、及び、第2ゲート電極膜5aは、第1導電型のゲート電極となる。

【0017】

電界効果トランジスタでは、ゲート絶縁膜2下のチャネル領域(半導体基板1の部分)の両側にソース/ドレイン領域6が形成されている。ソース/ドレイン領域6は、第1導電型となる不純物(例えば、Pイオン、Bイオン)を含んだシリコンを主体とする領域である。

【0018】

次に、本発明の実施形態1に係る半導体装置の製造方法について図面を用いて説明する。図2〜図3は、本発明の実施形態1に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0019】

まず、半導体基板1の主面上にゲート絶縁膜2を形成し、その後、ゲート絶縁膜2上にシリコンを主体とする第1シリコン膜3を成膜する(ステップA1;図2(A)参照)。

【0020】

ここで、ゲート絶縁膜2は、例えば、熱酸化、プラズマ酸窒化により形成することができる。また、第1シリコン膜3は、例えば、CVD(Chemical Vapor Deposition;化学気相成長)法により成膜することができる。第1シリコン膜3は、後に熱処理等により多結晶化するが、ステップA1の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップA1ではアモルファス状態で第1シリコン膜3を成膜する方が、より好ましい。また、第1シリコン膜3の厚さは30nm以下であることが好ましい。

【0021】

次に、第1シリコン膜3の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層4を形成する(ステップA2;図2(B)参照)。

【0022】

ここで、介在層4の厚さは、1分子層以上かつ3.0nm以下であり、より好ましくは2.0nm以下である。1分子層以上としているのは、2次元平面状に介在層4のない箇所がある(隙間がある)場合、B注入時の突き抜け要因となってしまう。あるいは、隙間は第2シリコン膜5形成後の熱処理時にグレインの核として、一部グレインの肥大化要因となる。よって、2次元平面上隙間なく介在層を形成する必要がある。2.0nmまたは3.0nm以下としているのは、第1、第2シリコン膜3、5は良好な導電性を保つ必要があるため、これより厚くすることは電気特性上好ましくない。

【0023】

また、介在層4の形成位置は、ゲート電極全体の膜厚(図2(C)の第1シリコン膜3の下面から第2シリコン膜5の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜2と第1シリコン膜3との界面から、30nm以下の位置(言い換えれば、ステップB2で形成する第1シリコン膜3の厚さは30nm以下)であると、より好ましい。つまり、第1シリコン膜3が後の熱処理により多結晶化する際に、結晶グレインの肥大を防ぐためには、厚みは30nm以下であることが好ましい。

【0024】

また、介在層4の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜3を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜3の表面に介在層4となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図2(C)の5)を成膜することになる。第2の形成方法として、第1シリコン膜3を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層4となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図2(C)の5)を成膜する。

【0025】

次に、介在層4上にシリコンを主体とする第2シリコン膜5を成膜する(ステップA3;図2(C)参照)。

【0026】

ここで、第2シリコン膜5は、例えば、CVD法により成膜することができる。また、第2シリコン膜5は、後に熱処理等により多結晶化するが、ステップA3の成膜時点では、多結晶であっても、アモルファスであっても良い。

【0027】

次に、第1シリコン膜(図2(C)の3)及び第2のシリコン膜(図2(C)の5)に対して、第2シリコン膜5の上方から不純物イオン(例えば、Pイオン、Bイオン)を注入(導入)する(ステップA4;図2(D)参照)。これにより、第1シリコン膜(図2(C)の3)及び第2のシリコン膜(図2(C)の5)は、不純物イオンを含む第1ゲート電極膜3a及び第2ゲート電極膜5aとなる。

【0028】

次に、基板を活性化アニールする(ステップA5;図3(A)参照)。つまり、基板を加熱処理することにより、導入された不純物イオンを第1ゲート電極膜3a及び第2ゲート電極膜5a全体に拡散させ、活性化させる。

【0029】

ここで、ステップA5では、熱処理によって不純物イオンが第1ゲート電極膜3aに拡散する一方で、介在層4がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタの閾値電圧のばらつきを更に低減できる。なおステップA5の活性化アニールは、ステップA4のイオン注入時に施すことができ、このタイミングに限定されない。また、後のソース/ドレイン領域形成後のアニールなどといった他の熱処理と併用しても良い。いずれの工程でも、本発明を適用して同様に効果的である。

【0030】

次に、ゲート電極として残す領域にレジスト7を形成し、その後、レジスト7をマスクとして第2ゲート電極膜5a、介在層4、第1ゲート電極膜3a、及び、ゲート絶縁膜2を、半導体基板1が表れるまでエッチングする(ステップA6;図3(B)参照)。

【0031】

最後に、レジスト7をマスクとして半導体基板1に不純物イオンを注入することによりソース/ドレイン領域6を形成し、その後、レジスト7を除去する(ステップA7;図3(C)参照)。これにより、図1と同様な半導体装置ができる。

【0032】

実施形態1によれば、シリコン膜3、5間に、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする介在層4を介在させることにより、シリコン膜3、5を導電化(低抵抗化)するために不純物イオンを注入する際、当該不純物イオンがシリコン膜3下のチャネル領域にまで到達し難くなる。その結果、トランジスタの閾値電圧のばらつきを低減できる。

【0033】

[実施形態2]

本発明の実施形態2に係る半導体装置について図面を用いて説明する。図4は、本発明の実施形態2に係る半導体装置の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【0034】

実施形態2は、実施形態1に係るゲート電極を、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor;金属酸化膜半導体電界効果トランジスタ)を相補形に配置したCMOS(Complementary Metal Oxide Semiconductor; 相補型金属酸化膜半導体)トランジスタのゲート電極に適用したものである。

【0035】

図4を参照すると、半導体装置は、半導体基板11(例えば、シリコン基板)上に素子(トランジスタ)間を電気的に分離するSTI(Shallow Trench Isolation;例えば、シリコン酸化膜)12が形成されている。半導体装置は、STI12で囲まれたPチャネルトランジスタ30が形成される領域において半導体基板11上にNウェル14が形成されており、STI12で囲まれたNチャネルトランジスタ31が形成される領域において半導体基板11上にPウェル13が形成されている。Pウェル13は、P型の不純物を含んだシリコンを主体とするウェルである。Nウェル14は、N型の不純物を含んだシリコンを主体とするウェルである。

【0036】

Pチャネルトランジスタ30が形成される領域では、Nウェル14の主面上にゲート絶縁膜15(例えば、シリコン酸化膜)を介してP型第1シリコン膜16aが形成されている。P型第1シリコン膜16aは、P型の不純物を含んだシリコンを主体とする導電膜である。P型第1シリコン膜16a上には、介在層17が形成されている。介在層17は、P型第1シリコン膜16aとP型第2シリコン膜18aとの間に介在した層(例えば、絶縁層)であり、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層17上には、P型第2シリコン膜18aが形成されている。P型第2シリコン膜18aは、P型の不純物(P型第1シリコン膜16a中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。P型第1シリコン膜16a、介在層17、及び、P型第2シリコン膜18aは、P型ゲート電極32となる。P型第2シリコン膜18a上には、保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁は、オフセットスペーサ20(例えば、シリコン窒化膜)を介してサイドウォール21(例えば、シリコン酸化膜)で覆われている。サイドウォール21下のNウェル14上には、P−型LDD(Lightly Doped Drain)領域23が形成されている。P−型LDD領域23とSTI12との間の領域におけるNウェル14上には、P+型ソース/ドレイン領域24が形成されている。P−型LDD領域23は、P型の不純物を含んだシリコンを主体とする領域であり、P+型ソース/ドレイン領域24よりも不純物濃度が薄くなっている。P+型ソース/ドレイン領域24は、P型の不純物を含んだシリコンを主体とする領域であり、P−型LDD領域23よりも不純物濃度が濃くなっている。

【0037】

Nチャネルトランジスタ31が形成される領域では、Pウェル13の主面上にゲート絶縁膜15(例えば、シリコン酸化膜)を介してN型第1シリコン膜16bが形成されている。N型第1シリコン膜16bは、N型の不純物を含んだシリコンを主体とする導電膜である。N型第1シリコン膜16b上には、介在層17が形成されている。介在層17は、N型第1シリコン膜16bとN型第2シリコン膜18bとの間に介在した層(例えば、絶縁層)であり、Pチャネルトランジスタ30における介在層17と同様に、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層17上には、N型第2シリコン膜18bが形成されている。N型第2シリコン膜18bは、N型の不純物(N型第1シリコン膜16b中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。N型第1シリコン膜16b、介在層17、及び、N型第2シリコン膜18bは、N型ゲート電極33となる。N型第2シリコン膜18b上には、保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁は、オフセットスペーサ20(例えば、シリコン窒化膜)を介してサイドウォール21(例えば、シリコン酸化膜)で覆われている。サイドウォール21下のPウェル13上には、N−型LDD領域25が形成されている。N−型LDD領域25とSTI12との間の領域におけるPウェル13上には、N+型ソース/ドレイン領域26が形成されている。N−型LDD領域25は、N型の不純物を含んだシリコンを主体とする領域であり、N+型ソース/ドレイン領域26よりも不純物濃度が薄くなっている。N+型ソース/ドレイン領域26は、N型の不純物を含んだシリコンを主体とする領域であり、N−型LDD領域25よりも不純物濃度が濃くなっている。

【0038】

Pチャネルトランジスタ30、Nチャネルトランジスタ31、及び、STI12を含む基板上には、ライナー膜22(例えば、シリコン窒化膜)を介して層間絶縁膜27(例えば、シリコン酸化膜)が形成されている。Pチャネルトランジスタ30が形成された領域では、層間絶縁膜27及びライナー膜22を貫通してP+型ソース/ドレイン領域24と接続されたコンタクトプラグ29(例えば、タングステン)が形成されている。Nチャネルトランジスタ31が形成された領域では、層間絶縁膜27及びライナー膜22を貫通してN+型ソース/ドレイン領域26と接続されたコンタクトプラグ28(例えば、タングステン)が形成されている。

【0039】

次に、本発明の実施形態2に係る半導体装置の製造方法について図面を用いて説明する。図5〜図7は、本発明の実施形態2に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0040】

まず、半導体基板1上の素子分離領域にSTI12を形成し、その後、半導体基板11にPウェル13、Nウェル14を形成し、その後、チャネルを形成する(ステップB1;図5(A)参照)。

【0041】

ここで、STI12、Pウェル13(イオン注入など)、Nウェル14(イオン注入など)、及び、チャネル(イオン注入など)は、周知の方法で形成することができる。なお、チャネルについては、以降、図示しない。

【0042】

次に、STI12、Pウェル13、及び、Nウェル14を含む基板の主面上にゲート絶縁膜15を形成し、その後、ゲート絶縁膜15上にシリコンを主体とする第1シリコン膜16を成膜する(ステップB2;図5(B)参照)。

【0043】

ここで、ゲート絶縁膜15は、例えば、熱酸化、プラズマ酸窒化により形成することができる。また、第1シリコン膜16は、例えば、CVD法により成膜することができる。第1シリコン膜16は、後に熱処理等により多結晶化するが、本工程の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップB2ではアモルファス状態で第1シリコン膜16を成膜する方が、より好ましい。また、第1シリコン膜16の厚さは30nm以下であることが好ましい。

【0044】

次に、第1シリコン膜16の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層17を形成する(ステップB3;図5(C)参照)。

【0045】

ここで、介在層17の厚さは、1分子層以上かつ3nm以下であり、より好ましくは2nm以下である。介在層17の形成位置は、ゲート電極全体の膜厚(図6(A)の第1シリコン膜16の下面から第2シリコン膜18の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜15と第1シリコン膜16との界面から、30nm以下の位置(言い換えれば、ステップB2で形成する第1シリコン膜16の厚さは30nm以下)であると、より好ましい。

【0046】

また、介在層17の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜16を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜16の表面に介在層17となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図6(A)の18)を成膜することになる。第2の形成方法として、第1シリコン膜16を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層17となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図6(A)の18)を成膜する。

【0047】

次に、介在層17上にシリコンを主体とする第2シリコン膜18を成膜する(ステップB4;図6(A)参照)。

【0048】

ここで、第2シリコン膜18は、例えば、CVD法により成膜することができる。また、第2シリコン膜18は、後に熱処理等により多結晶化するが、ステップB4の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップB4ではアモルファス状態で成膜する方が、より好ましい。

【0049】

次に、Nウェル14が形成された領域の第2シリコン膜18上にフォトレジスト34を形成し、その後、フォトレジスト34をマスクとして、Pウェル13が形成された領域のシリコン膜18b、16bにドナーイオン(As、Pなど)を注入する(ステップB5;図6(B)参照)。その後、フォトレジスト34を除去する。

【0050】

次に、Pウェル13が形成された領域のN型第2シリコン膜18b上にフォトレジスト35を形成し、その後、フォトレジスト35をマスクとして、Nウェル14が形成された領域のシリコン膜18a、16aにアクセプタイオン(Bなど)を注入する(ステップB6;図6(C)参照)。その後、フォトレジスト35を除去する。

【0051】

なお、ステップB5とステップB6とは順序を入れ替えても良い。ステップB5及びステップB6の際、介在層17がストッパとなり、注入されたイオンがチャネル領域に達するのを防ぐ。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0052】

また、B(ホウ素)は、比較的原子量が小さいため、イオン注入時にチャネル領域に達し易い。この観点から、本発明の構成は、アクセプタイオン(特に、B)をシリコン膜18a、16aに注入したP型ゲート電極(図4の32)を有するPチャネルトランジスタ(図4の30)に適用する場合により効果的である。

【0053】

さらに、シリコン膜形成工程(ステップB2〜ステップB4)の後、イオン注入工程(ステップB5〜ステップB6)の前に、基板の加熱を要する工程(例えば、別工程で形成するトランジスタのゲート絶縁膜を形成するための熱酸化工程など)が含まれることがある。このとき、シリコン膜が多結晶化され、グレインの肥大化に伴ってラフネスが増加することがある。ラフネスが増加すると、シリコン膜が局所的に薄くなる個所が発生し、その後、注入する不純物イオンがチャネル領域に抜け易くなる。この点、実施例2によれば、シリコン膜16、18間に介在層17を配置しているため、グレインの肥大化が抑制され、シリコン膜16、18が局所的に薄くなる個所を低減できる。従って、注入イオンがチャネル領域に達するのを防ぐことができる。

【0054】

次に、基板全体を加熱処理(活性化アニール)する(ステップB7;図7(A)参照)。

【0055】

ステップB7では、加熱処理によりシリコン膜16a、16b、18a、18bに注入された不純物イオンをシリコン膜16a、16b、18a、18b全体に拡散させ活性化させる。特に、加熱処理によって不純物イオンが第1シリコン膜16a、16bに拡散する一方で、介在層17がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタの閾値電圧のばらつきを更に低減できる。なお、不純物活性化のためのアニールは、イオン注入工程(ステップB5、ステップB6)に施せばよく、このタイミングに限定されない。

【0056】

なお、ステップB7は、後のLDD形成工程(ステップB8)やソース/ドレイン形成工程(ステップB8)後のアニールなどといった他の熱処理と併用しても良い。いずれの場合でも、同様に効果的である。

【0057】

次に、ゲート電極32、33として残す領域の第2シリコン膜18a、18b上に保護膜19(例えば、シリコン窒化膜)を形成し、その後、保護膜19をマスクとして第2シリコン膜18a、18b、介在層17、第1シリコン膜16a、16b、及び、ゲート絶縁膜15を、Pウェル13及びNウェル14が表れるまでエッチングし、その後、Nウェル14形成領域上の保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁、及び、Pウェル13形成領域上の保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁にサイドウォール状のオフセットスペーサ20(例えば、シリコン窒化膜)を形成し、その後、LDD領域(Pウェル13上にはN−型LDD領域25、Nウェル14上にはP−型LDD領域23)を形成し、その後、オフセットスペーサ20の側壁にサイドウォール21(例えば、シリコン酸化膜)を形成し、その後、ソース/ドレイン領域(Pウェル13上にはN+型ソース/ドレイン領域26、Nウェル14上にはP+型ソース/ドレイン領域24)を形成する(ステップB8;図7(B)参照)。これにより、トランジスタ30、31ができる。

【0058】

ここで、保護膜19は、例えば、第2シリコン膜18a、18b上にCVD法などによりシリコン窒化膜を成膜し、その後、ゲート電極32、33として残す領域のシリコン窒化膜上にフォトレジストを形成し、当該フォトレジストをマスクとしてシリコン窒化膜を、第2シリコン膜18a、18bが表れるまでエッチングすることにより形成することができる。

【0059】

また、オフセットスペーサ20は、ゲート電極32、33を含む基板全面にCVD法などによりシリコン窒化膜を成膜し、その後、Pウェル13及びNウェル14が表れるまでシリコン窒化膜をエッチバックすることにより形成することができる。

【0060】

また、LDD領域の形成について、Pウェル13上にN−型LDD領域25を形成するときは、P型ゲート電極32を含むNウェル14が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてPウェル13にドナーイオン(As、Pなど)を注入し、その後、フォトレジストを除去する。Nウェル14上にP−型LDD領域23を形成するときは、N型ゲート電極33を含むPウェル13が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてNウェル14にアクセプタイオン(Bなど)を注入し、その後、フォトレジストを除去する。

【0061】

また、サイドウォール21は、オフセットスペーサ20及びゲート電極32、33を含む基板全面にCVD法などによりシリコン酸化膜を成膜し、その後、N−型LDD領域25及びP−型LDD領域23が表れるまでシリコン酸化膜をエッチバックすることにより形成することができる。

【0062】

さらに、ソース/ドレイン領域の形成について、Pウェル13上にN+型ソース/ドレイン領域26を形成するときは、P型ゲート電極32を含むNウェル14が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてPウェル13にドナーイオン(As、Pなど)を注入し、その後、フォトレジストを除去する。Nウェル14上にP+型ソース/ドレイン領域24を形成するときは、N型ゲート電極33を含むPウェル13が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてNウェル14にアクセプタイオン(Bなど)を注入し、その後、フォトレジストを除去する。

【0063】

最後に、Pチャネルトランジスタ30及びNチャネルトランジスタ31を含む基板全面にライナー膜22(例えば、シリコン窒化膜)を成膜し、その後、ライナー膜22上に層間絶縁膜27を形成し、その後、層間絶縁膜27及びライナー膜22にソース/ドレイン領域24、26に通ずる下穴を形成し、その後、当該下穴にコンタクトプラグ28、29を形成する(ステップB9;図7(C)参照)。なお、ステップB9の後は、配線、層間絶縁膜、ビアプラグ、上層配線の形成といった周知の工程が続くことになる。

【0064】

ここで、ライナー膜22は、例えば、CVD法などによりシリコン窒化膜を成膜することにより形成することができる。層間絶縁膜27は、SOD(Spin on Dielectric;スピンオン層間絶縁膜)を用いることができる。下穴は、層間絶縁膜27上に下孔を形成する部分で開口したフォトレジストを形成し、その後、当該フォトレジストをマスクとして、層間絶縁膜27及びライナー膜22を、ソース/ドレイン領域24、26が表れるまでエッチングし、その後、フォトレジストを除去することにより形成することができる。コンタクトプラグ28、29は、例えば、下穴を含む層間絶縁膜27上に導電体膜(例えば、タングステン)を成膜し、CMP(Chemical Mechanical Polishing;化学機械研磨)により層間絶縁膜27が表れるまで研磨することにより形成することができる。

【0065】

実施形態2によれば、イオン注入工程(ステップB5、ステップB6;図6(B)、(C)参照)の際に、介在層17がストッパとなり、注入イオンがチャネル領域に達するのを防ぐことができる。これにより、トランジスタ30、31の閾値電圧のばらつきを低減できる。

【0066】

また、シリコン膜形成工程(ステップB2〜ステップB4;図5(B)〜図6(A)参照)の後、イオン注入工程(ステップB5、ステップB6;図6(B)、(C)参照)の前に、基板の加熱を要する工程が含まれる場合がある(例えば、別工程で形成するトランジスタのゲート絶縁膜を形成するための熱酸化工程など)。そのような場合に、シリコン膜が多結晶化され、グレインの肥大化に伴ってラフネスが増加することがある。このとき、シリコン膜が局所的に薄くなる個所が発生し、その後、注入する不純物イオンがチャネル領域に抜け易くなる。この点、実施形態2によれば、シリコン膜16、18間に介在層17を配置しているため、グレインの肥大化が抑制され、シリコン膜16、18が局所的に薄くなる個所を低減できる。従って、注入イオンがチャネル領域に達するのを防ぐことができる。

【0067】

さらに、実施形態2によれば、加熱処理(ステップB7;図7(A)参照)によって不純物イオンが第1シリコン膜16に拡散する一方で、介在層17がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタ30、31の閾値電圧のばらつきを更に低減できる。

【0068】

[実施形態3]

本発明の実施形態3に係る半導体装置について図面を用いて説明する。図8は、本発明の実施形態3に係る半導体装置の構成を模式的に示した平面図である。図9は、本発明の実施形態3に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。図10は、本発明の実施形態3に係る半導体装置におけるメモリセル領域の構成を模式的に示した(A)平面図、(B)Y−Y´間の断面図である。

【0069】

実施形態3は、実施形態2のゲート電極(図4の32、33)の構造を6F2/bWL型DRAM(Dynamic Random Access Memory)チップ36における周辺回路領域38のゲート電極32、33に応用したものである。

【0070】

図8を参照すると、DRAMチップ36は、メモリセルアレイが形成された複数のメモリセル領域37が行方向及び列方向に配置されており、各メモリセル領域37の周囲には、IOバッファなどの周辺回路が形成された周辺回路領域38が配置されている。

【0071】

図9を参照すると、周辺回路領域38では、実施形態2(図4参照)と同様なCMOSトランジスタが形成されている。ただし、P型ゲート電極32においては、P型第2シリコン膜18aと保護膜19との間にて、下側から順にP型第3シリコン膜43a及び導電膜44が介在している。同様に、N型ゲート電極33においても、N型第2シリコン膜18bと保護膜19との間にて、下側から順にN型第3シリコン膜43b及び導電膜44が介在している。また、コンタクトプラグ28、29(保護膜19を含めても可)を含む層間絶縁膜27上の一部には、Nチャネルトランジスタ31のN+型ソース/ドレイン領域26とコンタクトプラグ28を介して電気的に接続された配線46aと、Pチャネルトランジスタ30のP+型ソース/ドレイン領域24とコンタクトプラグ29を介して電気的に接続された配線46bと、が形成されている。配線46a、46bを含む基板全面には、エッチングストッパ膜47が形成されている。エッチングストッパ膜47上には層間絶縁膜48が形成されている。

【0072】

図10を参照すると、メモリセル領域37においては、6F2(設計ルール上のセル面積)/bWL(buried Word Line;埋込ワード線)型のメモリセルが形成されている。メモリセル領域37では、半導体基板11(例えば、シリコン基板)上に素子(トランジスタ)間を電気的に分離するSTI(Shallow Trench Isolation;例えば、シリコン酸化膜)12が形成されている。STI12で囲まれた領域において半導体基板11に2つのトレンチ(図13(A)の11a)が形成されており、当該トレンチの表面(底面、側壁面)にゲート絶縁膜39(例えば、シリコン酸化膜)が形成されており、当該トレンチにおいて完全に満たされない状態でゲート絶縁膜39を介して埋込ワード線40(例えば、金属膜など)が埋め込まれている。埋込ワード線40は、ゲート電極となる。埋込ワード線40とSTI12との間の領域の半導体基板11及びSTI12上には、周辺回路領域(図9の38)のPチャネルトランジスタ(図9の30)及びNチャネルトランジスタ(図9の31)において用いられているゲート絶縁膜(図9の15)と同層のゲート絶縁膜15が形成されている。埋込ワード線40間の領域の半導体基板11上には、ゲート絶縁膜15及びゲート絶縁膜39が形成されていない。ゲート絶縁膜15、39及び埋込ワード線40上にはビットコンタクト層間絶縁膜42(例えば、シリコン酸化膜)が形成されている。ビットコンタクト層間絶縁膜42は、埋込ワード線40間の領域の半導体基板11上に形成されていない。埋込ワード線40間の領域の半導体基板11を含むビットコンタクト層間絶縁膜42上の一部には、半導体基板11(ソース領域となる部分)に接続されたN型第3シリコン膜43c(BL;ビット線)が形成されており、N型第3シリコン膜43c上に導電膜44(例えば、金属膜、シリサイド膜など)を介して保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、導電膜44、及び埋込ワード線40の側壁面ないしビットコンタクト層間絶縁膜42の表面には、ライナー膜22(例えば、シリコン窒化膜)が形成されている。ライナー膜22上には、層間絶縁膜27(例えば、シリコン酸化膜)が形成されている。層間絶縁膜27は、保護膜19上を覆っていない(覆っていても可)。層間絶縁膜27、ライナー膜22、ビットコンタクト層間絶縁膜42、及びゲート絶縁膜15には、埋込ワード線40とSTI12との間の領域の半導体基板11(ドレイン領域となる部分)に通ずる下穴が形成されており、当該下穴に容量コンタクトプラグ45(例えば、タングステン)が埋め込まれている。

【0073】

メモリセル領域37では、容量コンタクトプラグ45(保護膜19を含めても可)を含む層間絶縁膜27上の一部には、容量コンタクトプラグ45と接続された容量コンタクトパッド46c(例えば、金属膜)が形成されている。容量コンタクトパッド46c及び保護膜19を含む層間絶縁膜27上には、エッチングストッパ膜47(例えば、シリコン窒化膜)が形成されている。エッチングストッパ膜47には、容量コンタクトパッド46cに通ずる開口部が形成されている。容量コンタクトパッド46c上にはクラウン状のキャパシタ50が形成されている。キャパシタ50は、下側から順に、導電膜51(下部電極)、誘電膜52(容量膜)、導電膜53(上部電極)が形成されている。導電膜51は、容量コンタクトパッド46cと接続されている。誘電膜52及び導電膜53は、エッチングストッパ膜47上にも形成されている。導電膜53上には、プレート電極54(例えば、金属膜)が形成されている。

【0074】

次に、本発明の実施形態3に係る半導体装置の製造方法について図面を用いて説明する。図11〜図15は、本発明の実施形態3に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0075】

まず、半導体基板1上の素子分離領域にSTI12を形成し、その後、メモリセル領域37の半導体基板11中にディープNウェル(図示せず)を形成し、その後、周辺回路領域38の半導体基板11にPウェル13、Nウェル14を形成し、その後、チャネル(図示せず)を形成し、その後、STI12、Pウェル13、及び、Nウェル14を含む基板の主面上にゲート絶縁膜15を形成する(ステップC1;図11(A)参照)。

【0076】

ここで、STI12、ディープNウェル(図示せず;イオン注入など)、Pウェル13(イオン注入など)、Nウェル14(イオン注入など)、チャネル(図示せず;イオン注入など)、及び、ゲート絶縁膜15(例えば、熱酸化、プラズマ酸窒化)は、周知の方法で形成することができる。

【0077】

次に、ゲート絶縁膜15上にシリコンを主体とする第1シリコン膜16を成膜する(ステップC2;図11(B)参照)。

【0078】

ここで、第1シリコン膜16は、周辺回路領域38のゲート電極(図9の32、33)となるものであるが、この段階ではメモリセル領域37にも形成される。第1シリコン膜16は、例えば、CVD法により成膜することができる。第1シリコン膜16は、後に熱処理等により多結晶化するが、本工程の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップC2ではアモルファス状態で第1シリコン膜16を成膜する方が、より好ましい。また、第1シリコン膜16の厚さは30nm以下であることが好ましい。

【0079】

次に、第1シリコン膜16の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層17を形成する(ステップC3;図12(A)参照)。

【0080】

ここで、介在層17の厚さは、1分子層以上かつ3nm以下であり、より好ましくは2nm以下である。介在層17の形成位置は、ゲート電極全体の膜厚(図12(B)の第1シリコン膜16の下面から第2シリコン膜18の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜15と第1シリコン膜16との界面から、30nm以下の位置(言い換えれば、ステップC2で形成する第1シリコン膜16の厚さは30nm以下)であると、より好ましい。

【0081】

また、介在層17の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜16を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜16の表面に介在層17となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図12(B)の18)を成膜することになる。第2の形成方法として、第1シリコン膜16を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層17となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図12(B)の18)を成膜する。

【0082】

次に、介在層17上にシリコンを主体とする第2シリコン膜18を成膜する(ステップC4;図12(B)参照)。

【0083】

ここで、第2シリコン膜18は、例えば、CVD法により成膜することができる。また、第2シリコン膜18は、後に熱処理等により多結晶化するが、ステップC4の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップC4ではアモルファス状態で成膜する方が、より好ましい。

【0084】

次に、メモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16を除去し、その後、基板上に埋込ワード線(図10の40)形成用のハードマスク49を形成し、その後、ハードマスク49をマスクとしてゲート絶縁膜15及び半導体基板11をエッチングすることによりトレンチ11aを形成する(ステップC5;図13(A)参照)。

【0085】

ここで、メモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16の除去では、例えば、周辺回路領域38の第2シリコン膜18上にフォトレジストを形成し、その後、当該フォトレジストをマスクとしてメモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16をエッチングすることによりトレンチ11aを形成し、その後、フォトレジストを除去する。

【0086】

また、ハードマスク49には、例えば、シリコン酸化膜、シリコン窒化膜、その他半導体基板11のドライエッチングに対して選択性の高い膜を用いることができる。また、ハードマスク49は、例えば、基板全面にハードマスク49を成膜(例えば、CVD法)し、その後、ハードマスク49上に、埋込ワード線(図10の40)形成用の開口部を有するフォトレジストを形成し、その後、当該フォトレジストをマスクとしてハードマスク49をエッチングし、その後、フォトレジストを除去することにより形成することができる。

【0087】

さらに、トレンチ11aの形成では、例えば、STI12の底面よりも深くならない程度の深さまで、ゲート絶縁膜15の半導体基板11をドライエッチングすることにより形成することができる。

【0088】

次に、基板全面に、メモリセル領域37のトランジスタ用のゲート絶縁膜39(例えば、シリコン酸化膜)を形成する(ステップC6;図13(B)参照)。

【0089】

ここで、ゲート絶縁膜39は、例えば、熱酸化又はプラズマ酸窒化により形成することができる。この熱処理により、先に形成した周辺回路領域38のシリコン膜16、18が多結晶化されるが、本発明ではシリコン膜16、18間に介在層17を介在させたことにより、多結晶化の際のグレインの肥大化が抑制される。従って、当該シリコン膜16、18が局所的に薄くなる個所が発生し難い。これにより、後のステップC8及びステップC9における当該シリコン膜16a、16b、18a、18bへの不純物イオン注入の際、局所的に薄い個所を介したチャネル領域へのイオン抜けが低減される。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0090】

なお、シリコン膜16、18の多結晶化によるグレインの肥大化をもたらす熱処理は、ステップC6のメモリセル領域37のトランジスタ用のゲート絶縁膜39の形成に限定されない。即ち、周辺回路領域38のゲート電極となるシリコン膜16、18を形成した後に熱処理を施す工程およびイオン注入を施す工程を有していれば、本発明の介在層17を適用することにより、同様に効果的である。ただし、メモリセル領域37のトランジスタのゲート絶縁膜39はより高い温度での熱処理を要することから、先に形成した周辺回路領域38のシリコン膜16、18のグレインサイズがより肥大化することが懸念される。従って、ステップC6のように、周辺回路領域38にシリコン膜16、18を形成した後に、メモリセル領域37のトランジスタのゲート絶縁膜39を形成するための熱処理を施す工程を有する半導体装置の製造方法に、本発明の介在層17を適用すれば、より効果的である。

【0091】

次に、トレンチ(図13(A)の11a)内のゲート絶縁膜39上に埋込ワード線40(例えば、導電膜)を形成し、その後、ゲート絶縁膜39(ハードマスク49上にある部分)及びハードマスク49を除去し、その後、基板全面にビットコンタクト層間絶縁膜42(例えば、シリコン酸化膜)を成膜し、その後、ビットコンタクト層間絶縁膜42において埋込ワード線40間の領域の半導体基板11(ソース領域となる部分)に通ずる開口部を形成し、その後、基板全面に第3シリコン膜43を成膜する(ステップC7;図14(A)参照)。

【0092】

ここで、埋込ワード線40は、例えば、基板全面に導電膜を堆積し、その後、エッチバックにより不要な導電膜を除去することにより、トレンチ(図13(A)の11a)内のゲート絶縁膜39上に埋込ワード線40を形成することができる。

【0093】

また、ビットコンタクト層間絶縁膜42における開口部の形成は、例えば、ビットコンタクト層間絶縁膜42上に、開口部形成用のフォトレジストを形成し、その後、当該フォトレジストをマスクとしてビットコンタクト層間絶縁膜42をエッチングすることにより開口部を形成することができる。

【0094】

さらに、第3シリコン膜43は、例えば、CVD法によって成膜することができる。第3シリコン膜43は、周辺回路領域38ではゲート電極(図9の32、33)の一部になり、メモリセル領域37ではビット線の一部になる。

【0095】

次に、周辺回路領域38のNウェル14が形成された領域の第3シリコン膜43上にフォトレジスト34を形成し、その後、フォトレジスト34をマスクとして、周辺回路領域38のPウェル13が形成された領域、及び、メモリセル領域37のシリコン膜18b、16b、43b及び43cにドナーイオン(As、Pなど)を注入する(ステップC8;図14(B)参照)。その後、フォトレジスト34を除去する。

【0096】

次に、周辺回路領域38のPウェル13が形成された領域、及び、メモリセル領域37のN型第3シリコン膜43b及び43c上にフォトレジスト35を形成し、その後、フォトレジスト35をマスクとして、周辺回路領域38のNウェル14が形成された領域のシリコン膜43a、18a、16aにアクセプタイオン(Bなど)を注入する(ステップC9;図15(A)参照)。その後、フォトレジスト35を除去する。

【0097】

なお、ステップC8とステップC9とは順序を入れ替えても良い。ステップC8及びステップC9の際、介在層17がストッパとなり、注入されたイオンがチャネル領域に達するのを防ぐ。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0098】

また、実施形態3では、シリコン膜16a、18a間及び16b、18b間に介在層17を導入したことで、ステップC6などの熱処理(ゲート絶縁膜39の形成)においてシリコン膜16a、16b、18a、18b、43a、43bのグレインの肥大化によるラフネスの増大が抑制される。これにより、シリコン膜16a、16b、18a、18b、43a、43bが局所的に薄くなる個所が発生し難い。従って、ステップC8及びステップC9で当該シリコン膜16a、16b、18a、18bにイオン注入を施す際、不純物イオンがシリコン膜16a、16b、18a、18b、43a、43bの局所的に薄い個所を介してチャネル領域に注入されるのを防ぐことができる。結果として、トランジスタの閾値電圧のばらつきを低減できる。

【0099】

さらに、シリコン膜16a、18a間及び16b、18b間に介在層17を導入したことで、チャネル領域にまで達する注入イオンの量を低減できる。そして、注入された不純物イオンの拡散および活性化のためのアニールにおいても、チャネル領域にまで達するイオンを低減できる。結果として、トランジスタの閾値電圧のばらつきを更に低減できる。この作用効果は、B(ホウ素)を注入するPチャネルトランジスタのP型ゲート電極(図9の32)に対してより効果的である。

【0100】

次に、基板全体を加熱処理(活性化アニール)し、その後、基板全面に導電膜44(例えば、金属膜、シリサイド膜)を成膜し、その後、ゲート電極32、33及びビット線(N型第3シリコン膜43c)として残す領域の導電膜44上に保護膜19(例えば、シリコン窒化膜)を形成し、その後、保護膜19をマスクとして導電膜44、第3シリコン膜43a、43b、43c、第2シリコン膜18a、18b、介在層17、第1シリコン膜16a、16b、及び、ゲート絶縁膜15を、Pウェル13及びNウェル14が表れるまでエッチングし、その後、周辺回路領域38でのみ、Nウェル14形成領域上の保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁、及び、Pウェル13形成領域上の保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁にサイドウォール状のオフセットスペーサ20(例えば、シリコン窒化膜)を形成し、その後、LDD領域(Pウェル13上にはN−型LDD領域25、Nウェル14上にはP−型LDD領域23)を形成し、その後、周辺回路領域38でのみ、オフセットスペーサ20の側壁にサイドウォール21(例えば、シリコン酸化膜)を形成し、その後、ソース/ドレイン領域(Pウェル13上にはN+型ソース/ドレイン領域26、Nウェル14上にはP+型ソース/ドレイン領域24)を形成する(ステップC10;図15(B)参照)。これにより、メモリセル領域37のビット線、及び、周辺回路領域38のトランジスタが完成する。

【0101】

なお、導電膜44は、周辺回路領域38ではゲート電極32、33の一部になり、メモリセル領域37ではビット線(BL)の一部になる。また、加熱処理、保護膜19の形成、オフセットスペーサ20の形成、LDD領域23、25の形成、サイドウォール21の形成、及び、ソース/ドレイン領域24、26の形成については、実施形態2のステップB7、ステップB8と同様である。

【0102】

最後に、Pチャネルトランジスタ30及びNチャネルトランジスタ31並びにビット線(N型第3シリコン膜43c)を含む基板全面にライナー膜22(例えば、シリコン窒化膜)を成膜し、その後、ライナー膜22上に層間絶縁膜27を形成し、その後、基板の表面を平坦化(例えば、CMP)し、その後、周辺回路領域38において層間絶縁膜27及びライナー膜22にソース/ドレイン領域24、26に通ずる下穴を形成し、メモリセル領域37において埋込ワード線40とSTI12との間の領域の半導体基板11(ドレイン領域となる部分)に通ずる下穴を形成し、その後、当該下穴にコンタクトプラグ28、29及び容量コンタクトプラグ45(例えば、タングステン)を形成し、その後、コンタクトプラグ28、29及び容量コンタクトプラグ45を含む層間絶縁膜27上の一部に、コンタクトプラグ28に接続される配線46a、コンタクトプラグ29に接続される配線46b、及び、容量コンタクトプラグ45に接続される容量コンタクトパッド46c(例えば、導電膜)を形成し、その後、配線46a、46b及び容量コンタクトパッド46cを含む層間絶縁膜27上にエッチングストッパ膜47(例えば、シリコン窒化膜)を形成し、その後、クラウンキャパシタ50を形成する(ステップC11;図9、図10参照)。なお、ステップC11の後は、配線、層間絶縁膜、ビアプラグ、上層配線の形成といった周知の工程が続くことになる。

【0103】

ここで、配線46a、46b及び容量コンタクトパッド46cは、例えば、基板全面にCVD法などにより導電膜を成膜し、その後、配線46a、46b及び容量コンタクトパッド46cとして残す領域の導電膜上にフォトレジストを形成し、当該フォトレジストをマスクとして導電膜を、層間絶縁膜27が表れるまでエッチングすることにより形成することができる。

【0104】

また、クラウンキャパシタ50は、例えば、エッチングストッパ膜47上に層間絶縁膜48(例えば、シリコン酸化膜)を形成し、その後、メモリセル領域37における層間絶縁膜48及びエッチングストッパ47に容量コンタクトパッド46cに通ずる下穴を形成し、その後、当該下穴の表面(底面、側壁面)に導電膜51(下部電極)を形成し、その後、メモリセル領域37における層間絶縁膜48をエッチングにより除去し、その後、メモリセル領域37の全面に誘電膜52(容量膜)を形成し、その後、誘電膜52上に導電膜53(上部電極)を形成し、その後、メモリセル領域37において導電膜53上にプレート電極54を形成することにより形成することができる。

【0105】

なお、ライナー膜22の形成、層間絶縁膜27の形成、下穴の形成、コンタクトプラグ28、29及び容量コンタクトプラグ45の形成は、実施形態2のステップB9と同様である。

【0106】

実施形態3によれば、メモリセル領域37のトランジスタ用のゲート絶縁膜39の形成の際の熱処理により、先に形成した周辺回路領域38のシリコン膜16、18が多結晶化されるが、本発明ではシリコン膜16、18間に介在層17を導入したことにより、多結晶化の際のグレインの肥大化が抑制される。従って、当該シリコン膜16、18が局所的に薄くなる個所が発生し難い。これにより、後のステップC8およびステップC9における当該シリコン膜16a、16b、18a、18b、43a、43bへの不純物イオン注入の際、局所的に薄い個所を介したチャネル領域へのイオン抜けが低減される。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0107】

また、実施形態3によれば、シリコン膜16、18間に介在層17を導入したことで、チャネル領域にまで達する注入イオンの量を低減できる。そして、注入不純物の拡散および活性化のためのアニールにおいても、チャネル領域にまで達するイオンを低減できる。結果として、トランジスタの閾値電圧のばらつきを更に低減できる。この効果は、B(ホウ素)を注入するPチャネルトランジスタ30に対してより効果的である。

【0108】

[実施形態4]

本発明の実施形態4に係る半導体装置について図面を用いて説明する。図16は、本発明の実施形態4に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【0109】

実施形態4は、実施形態3の変形例であり、周辺回路領域38のゲート電極32、33において2層の介在層17、41を設けたものである。介在層17は、実施形態2と同様に、シリコン膜16a、18a間及びシリコン膜16b、18b間に導入された酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする層である。介在層41は、シリコン膜18a、43a間及びシリコン膜18b、43b間に導入された酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする層である。なお、周辺回路領域38におけるその他の構成、及び、メモリセル領域(図示せず)の構成は、実施形態3と同様である。

【0110】

次に、本発明の実施形態4に係る半導体装置の製造方法について図面を用いて説明する。図17は、本発明の実施形態4に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0111】

まず、実施形態3のステップC1〜ステップC4と同様に、半導体基板11上にSTI12、Pウェル13、Nウェル14、ゲート絶縁膜15、第1シリコン膜16、介在層17、及び第2シリコン膜18を形成する(ステップD1;図17(A)参照)。

【0112】

次に、第2シリコン膜18上に介在層41を形成する(ステップD2;図17(B)参照)。なお、介在層41は、介在層17と同様な方法により形成することができる。

【0113】

その後、実施形態3のステップC5〜ステップC11と同様な工程を行う(ステップD3)。

【0114】

実施形態4によれば、実施形態2、3と同様な効果を奏するとともに、2層の介在層17、41を設けることで、例えば、イオン注入のバリア効果(実施形態2)とグレイン肥大化抑制効果(実施形態3)とで、要求される膜厚や形成位置が異なる場合などにも対応できる。

【0115】

なお、本出願において図面参照符号を付している場合は、それらは、専ら理解を助けるためのものであり、図示の態様に限定することを意図するものではない。

【0116】

また、本発明の全開示(請求の範囲及び図面を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲及び図面を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0117】

1 半導体基板

2 ゲート絶縁膜

3 第1シリコン膜

3a 第1ゲート電極膜

4 介在層

5 第2シリコン膜

5a 第2ゲート電極膜

6 ソース/ドレイン領域

7 レジスト

11 半導体基板

11a トレンチ

12 STI

13 Pウェル

14 Nウェル

15 ゲート絶縁膜

16 第1シリコン膜

16a P型第1シリコン膜(第1ゲート電極膜)

16b N型第1シリコン膜(第1ゲート電極膜)

17 介在層

18 第2シリコン膜

18a P型第2シリコン膜(第2ゲート電極膜)

18b N型第2シリコン膜(第2ゲート電極膜)

19 保護膜

20 オフセットスペーサ

21 サイドウォール

22 ライナー膜

23 P−型LDD領域

24 P+型ソース/ドレイン領域

25 N−型LDD領域

26 N+型ソース/ドレイン領域

27 層間絶縁膜

28、29 コンタクトプラグ

30 Pチャネルトランジスタ

31 Nチャネルトランジスタ

32 P型ゲート電極

33 N型ゲート電極

34、35 フォトレジスト

36 DRAMチップ

37 メモリセル領域

38 周辺回路領域

39 ゲート絶縁膜(第2ゲート絶縁膜)

40 埋込ワード線(bWL)

41 介在層(第2介在層)

42 ビットコンタクト層間絶縁膜

43 第3シリコン膜

43a P型第3シリコン膜(第3ゲート電極膜)

43b N型第3シリコン膜(第3ゲート電極膜)

43c N型第3シリコン膜(BL、ビット線)

44 導電膜

45 容量コンタクトプラグ

46a、46b 配線

46c 容量コンタクトパッド

47 エッチングストッパ膜

48 層間絶縁膜

49 ハードマスク

50 キャパシタ

51 導電膜(下部電極)

52 誘電膜(容量膜)

53 導電膜(上部電極)

54 プレート電極

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置においては、電界効果トランジスタの動作速度の遅延を抑えるために、ゲート電極を低抵抗化することがある。例えば、特許文献1には、プレーナ型の電界効果トランジスタにおける、導電性のシリコン膜を用いたゲート電極の形成方法が開示されている。特許文献1では、基板上にゲート絶縁膜を介して形成されたゲート電極となる非結晶シリコン膜に不純物イオン(例えば、nMISFETではPイオン、pMISFETではBイオン)を注入することで、ゲート電極を低抵抗化している。これにより、低抵抗化された導電性のシリコンをゲート電極に適用したプレーナ型の電界効果トランジスタを形成できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−7329号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

以下の分析は、本願発明者により与えられる。

【0005】

特許文献1のようにして不純物イオンを注入することで低抵抗化したシリコン膜をゲート電極に用いる技術を本願発明者らが検討したところ、以下のことが分かった。即ち、MISFETにおけるゲート電極直下にはキャリアがドリフトするチャネル領域が存在し、注入したイオンがこのチャネル領域に達すると、MISFETの電気特性に影響を与え、閾値電圧が変わってしまう。

【0006】

例えば、更なる微細化の技術動向にあってゲート電極自体を薄くする場合、注入される不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達し易くなる。

【0007】

また、例えば、ゲート電極の形成工程やその後の製造工程の条件によっては、成膜したシリコン膜(ゲート電極)の多結晶化によりシリコン膜(ゲート電極)の膜厚が局所的に薄くなる個所が生じ得、その個所では、注入される不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達し易くなる。

【0008】

さらに、例えば、注入された不純物イオンがシリコン膜(ゲート電極)及びゲート絶縁膜を透過してチャネル領域に達した場合、熱処理を行うと、シリコン膜(ゲート電極)中の不純物イオンがゲート絶縁膜を透過してチャネル領域に拡散し易くなる。

【0009】

これらの点で、導電性のシリコン膜をゲート電極に適用した電界効果トランジスタを有する半導体装置には改善の余地がある。

【課題を解決するための手段】

【0010】

本発明の第1の視点においては、半導体装置において、半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有することを特徴とする。

【0011】

本発明の第2の視点においては、半導体装置の製造方法において、半導体基板の主面上に、絶縁膜を介してシリコンを主体とする第1シリコン膜を形成する工程と、前記第1シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層を形成する工程と、前記第1シリコン膜上に、前記介在層を介してシリコンを主体とする第2シリコン膜を形成する工程と、前記第1シリコン膜及び前記第2シリコン膜に対して、前記第2シリコン膜側から不純物イオンを注入する工程と、を含むことを特徴とする。

【発明の効果】

【0012】

本発明によれば、ゲート電極膜間(シリコン膜間)に配された介在層により、シリコン膜を導電化するために不純物イオンを注入する際、当該不純物イオンがシリコン膜下のチャネル領域にまで到達し難くなる。結果として、トランジスタの閾値電圧のばらつきを低減できる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態1に係る半導体装置の構成を模式的に示した断面図である。

【図2】本発明の実施形態1に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図3】本発明の実施形態1に係る半導体装置の製造方法を模式的に示した図2に続く工程断面図である。

【図4】本発明の実施形態2に係る半導体装置の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図5】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図6】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した図5に続く工程断面図である。

【図7】本発明の実施形態2に係る半導体装置の製造方法を模式的に示した図6に続く工程断面図である。

【図8】本発明の実施形態3に係る半導体装置の構成を模式的に示した平面図である。

【図9】本発明の実施形態3に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図10】本発明の実施形態3に係る半導体装置におけるメモリセル領域の構成を模式的に示した(A)平面図、(B)Y−Y´間の断面図である。

【図11】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した工程断面図である。

【図12】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図11に続く工程断面図である。

【図13】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図12に続く工程断面図である。

【図14】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図13に続く工程断面図である。

【図15】本発明の実施形態3に係る半導体装置の製造方法を模式的に示した図14に続く工程断面図である。

【図16】本発明の実施形態4に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【図17】本発明の実施形態4に係る半導体装置の製造方法を模式的に示した工程断面図である。

【発明を実施するための形態】

【0014】

[実施形態1]

本発明の実施形態1に係る半導体装置について図面を用いて説明する。図1は、本発明の実施形態1に係る半導体装置の構成を模式的に示した断面図である。

【0015】

図1を参照すると、半導体装置は、多結晶シリコンからなるゲート電極を有するプレーナ型の電界効果トランジスタを有する。

【0016】

電界効果トランジスタでは、半導体基板1(例えば、シリコン基板)の主面上にゲート絶縁膜2(例えば、シリコン酸化膜)を介して第1ゲート電極膜3aが形成されている。第1ゲート電極膜3aは、第1導電型となる不純物(例えば、Pイオン、Bイオン)を含んだシリコンを主体とする導電膜である。第1ゲート電極膜3a上には、介在層4が形成されている。介在層4は、第1ゲート電極膜3aと第2ゲート電極膜5aとの間に介在した層(例えば、絶縁層)であり、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層4上には、第2ゲート電極膜5aが形成されている。第2ゲート電極膜5aは、第1導電型となる不純物(第1ゲート電極膜3a中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。第1ゲート電極膜3a、介在層4、及び、第2ゲート電極膜5aは、第1導電型のゲート電極となる。

【0017】

電界効果トランジスタでは、ゲート絶縁膜2下のチャネル領域(半導体基板1の部分)の両側にソース/ドレイン領域6が形成されている。ソース/ドレイン領域6は、第1導電型となる不純物(例えば、Pイオン、Bイオン)を含んだシリコンを主体とする領域である。

【0018】

次に、本発明の実施形態1に係る半導体装置の製造方法について図面を用いて説明する。図2〜図3は、本発明の実施形態1に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0019】

まず、半導体基板1の主面上にゲート絶縁膜2を形成し、その後、ゲート絶縁膜2上にシリコンを主体とする第1シリコン膜3を成膜する(ステップA1;図2(A)参照)。

【0020】

ここで、ゲート絶縁膜2は、例えば、熱酸化、プラズマ酸窒化により形成することができる。また、第1シリコン膜3は、例えば、CVD(Chemical Vapor Deposition;化学気相成長)法により成膜することができる。第1シリコン膜3は、後に熱処理等により多結晶化するが、ステップA1の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップA1ではアモルファス状態で第1シリコン膜3を成膜する方が、より好ましい。また、第1シリコン膜3の厚さは30nm以下であることが好ましい。

【0021】

次に、第1シリコン膜3の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層4を形成する(ステップA2;図2(B)参照)。

【0022】

ここで、介在層4の厚さは、1分子層以上かつ3.0nm以下であり、より好ましくは2.0nm以下である。1分子層以上としているのは、2次元平面状に介在層4のない箇所がある(隙間がある)場合、B注入時の突き抜け要因となってしまう。あるいは、隙間は第2シリコン膜5形成後の熱処理時にグレインの核として、一部グレインの肥大化要因となる。よって、2次元平面上隙間なく介在層を形成する必要がある。2.0nmまたは3.0nm以下としているのは、第1、第2シリコン膜3、5は良好な導電性を保つ必要があるため、これより厚くすることは電気特性上好ましくない。

【0023】

また、介在層4の形成位置は、ゲート電極全体の膜厚(図2(C)の第1シリコン膜3の下面から第2シリコン膜5の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜2と第1シリコン膜3との界面から、30nm以下の位置(言い換えれば、ステップB2で形成する第1シリコン膜3の厚さは30nm以下)であると、より好ましい。つまり、第1シリコン膜3が後の熱処理により多結晶化する際に、結晶グレインの肥大を防ぐためには、厚みは30nm以下であることが好ましい。

【0024】

また、介在層4の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜3を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜3の表面に介在層4となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図2(C)の5)を成膜することになる。第2の形成方法として、第1シリコン膜3を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層4となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図2(C)の5)を成膜する。

【0025】

次に、介在層4上にシリコンを主体とする第2シリコン膜5を成膜する(ステップA3;図2(C)参照)。

【0026】

ここで、第2シリコン膜5は、例えば、CVD法により成膜することができる。また、第2シリコン膜5は、後に熱処理等により多結晶化するが、ステップA3の成膜時点では、多結晶であっても、アモルファスであっても良い。

【0027】

次に、第1シリコン膜(図2(C)の3)及び第2のシリコン膜(図2(C)の5)に対して、第2シリコン膜5の上方から不純物イオン(例えば、Pイオン、Bイオン)を注入(導入)する(ステップA4;図2(D)参照)。これにより、第1シリコン膜(図2(C)の3)及び第2のシリコン膜(図2(C)の5)は、不純物イオンを含む第1ゲート電極膜3a及び第2ゲート電極膜5aとなる。

【0028】

次に、基板を活性化アニールする(ステップA5;図3(A)参照)。つまり、基板を加熱処理することにより、導入された不純物イオンを第1ゲート電極膜3a及び第2ゲート電極膜5a全体に拡散させ、活性化させる。

【0029】

ここで、ステップA5では、熱処理によって不純物イオンが第1ゲート電極膜3aに拡散する一方で、介在層4がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタの閾値電圧のばらつきを更に低減できる。なおステップA5の活性化アニールは、ステップA4のイオン注入時に施すことができ、このタイミングに限定されない。また、後のソース/ドレイン領域形成後のアニールなどといった他の熱処理と併用しても良い。いずれの工程でも、本発明を適用して同様に効果的である。

【0030】

次に、ゲート電極として残す領域にレジスト7を形成し、その後、レジスト7をマスクとして第2ゲート電極膜5a、介在層4、第1ゲート電極膜3a、及び、ゲート絶縁膜2を、半導体基板1が表れるまでエッチングする(ステップA6;図3(B)参照)。

【0031】

最後に、レジスト7をマスクとして半導体基板1に不純物イオンを注入することによりソース/ドレイン領域6を形成し、その後、レジスト7を除去する(ステップA7;図3(C)参照)。これにより、図1と同様な半導体装置ができる。

【0032】

実施形態1によれば、シリコン膜3、5間に、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする介在層4を介在させることにより、シリコン膜3、5を導電化(低抵抗化)するために不純物イオンを注入する際、当該不純物イオンがシリコン膜3下のチャネル領域にまで到達し難くなる。その結果、トランジスタの閾値電圧のばらつきを低減できる。

【0033】

[実施形態2]

本発明の実施形態2に係る半導体装置について図面を用いて説明する。図4は、本発明の実施形態2に係る半導体装置の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【0034】

実施形態2は、実施形態1に係るゲート電極を、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor;金属酸化膜半導体電界効果トランジスタ)を相補形に配置したCMOS(Complementary Metal Oxide Semiconductor; 相補型金属酸化膜半導体)トランジスタのゲート電極に適用したものである。

【0035】

図4を参照すると、半導体装置は、半導体基板11(例えば、シリコン基板)上に素子(トランジスタ)間を電気的に分離するSTI(Shallow Trench Isolation;例えば、シリコン酸化膜)12が形成されている。半導体装置は、STI12で囲まれたPチャネルトランジスタ30が形成される領域において半導体基板11上にNウェル14が形成されており、STI12で囲まれたNチャネルトランジスタ31が形成される領域において半導体基板11上にPウェル13が形成されている。Pウェル13は、P型の不純物を含んだシリコンを主体とするウェルである。Nウェル14は、N型の不純物を含んだシリコンを主体とするウェルである。

【0036】

Pチャネルトランジスタ30が形成される領域では、Nウェル14の主面上にゲート絶縁膜15(例えば、シリコン酸化膜)を介してP型第1シリコン膜16aが形成されている。P型第1シリコン膜16aは、P型の不純物を含んだシリコンを主体とする導電膜である。P型第1シリコン膜16a上には、介在層17が形成されている。介在層17は、P型第1シリコン膜16aとP型第2シリコン膜18aとの間に介在した層(例えば、絶縁層)であり、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層17上には、P型第2シリコン膜18aが形成されている。P型第2シリコン膜18aは、P型の不純物(P型第1シリコン膜16a中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。P型第1シリコン膜16a、介在層17、及び、P型第2シリコン膜18aは、P型ゲート電極32となる。P型第2シリコン膜18a上には、保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁は、オフセットスペーサ20(例えば、シリコン窒化膜)を介してサイドウォール21(例えば、シリコン酸化膜)で覆われている。サイドウォール21下のNウェル14上には、P−型LDD(Lightly Doped Drain)領域23が形成されている。P−型LDD領域23とSTI12との間の領域におけるNウェル14上には、P+型ソース/ドレイン領域24が形成されている。P−型LDD領域23は、P型の不純物を含んだシリコンを主体とする領域であり、P+型ソース/ドレイン領域24よりも不純物濃度が薄くなっている。P+型ソース/ドレイン領域24は、P型の不純物を含んだシリコンを主体とする領域であり、P−型LDD領域23よりも不純物濃度が濃くなっている。

【0037】

Nチャネルトランジスタ31が形成される領域では、Pウェル13の主面上にゲート絶縁膜15(例えば、シリコン酸化膜)を介してN型第1シリコン膜16bが形成されている。N型第1シリコン膜16bは、N型の不純物を含んだシリコンを主体とする導電膜である。N型第1シリコン膜16b上には、介在層17が形成されている。介在層17は、N型第1シリコン膜16bとN型第2シリコン膜18bとの間に介在した層(例えば、絶縁層)であり、Pチャネルトランジスタ30における介在層17と同様に、酸素又は窒素のうち一方又は両方を含んだシリコンを主体とする。介在層17上には、N型第2シリコン膜18bが形成されている。N型第2シリコン膜18bは、N型の不純物(N型第1シリコン膜16b中の不純物と同じもの)を含んだシリコンを主体とする導電膜である。N型第1シリコン膜16b、介在層17、及び、N型第2シリコン膜18bは、N型ゲート電極33となる。N型第2シリコン膜18b上には、保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁は、オフセットスペーサ20(例えば、シリコン窒化膜)を介してサイドウォール21(例えば、シリコン酸化膜)で覆われている。サイドウォール21下のPウェル13上には、N−型LDD領域25が形成されている。N−型LDD領域25とSTI12との間の領域におけるPウェル13上には、N+型ソース/ドレイン領域26が形成されている。N−型LDD領域25は、N型の不純物を含んだシリコンを主体とする領域であり、N+型ソース/ドレイン領域26よりも不純物濃度が薄くなっている。N+型ソース/ドレイン領域26は、N型の不純物を含んだシリコンを主体とする領域であり、N−型LDD領域25よりも不純物濃度が濃くなっている。

【0038】

Pチャネルトランジスタ30、Nチャネルトランジスタ31、及び、STI12を含む基板上には、ライナー膜22(例えば、シリコン窒化膜)を介して層間絶縁膜27(例えば、シリコン酸化膜)が形成されている。Pチャネルトランジスタ30が形成された領域では、層間絶縁膜27及びライナー膜22を貫通してP+型ソース/ドレイン領域24と接続されたコンタクトプラグ29(例えば、タングステン)が形成されている。Nチャネルトランジスタ31が形成された領域では、層間絶縁膜27及びライナー膜22を貫通してN+型ソース/ドレイン領域26と接続されたコンタクトプラグ28(例えば、タングステン)が形成されている。

【0039】

次に、本発明の実施形態2に係る半導体装置の製造方法について図面を用いて説明する。図5〜図7は、本発明の実施形態2に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0040】

まず、半導体基板1上の素子分離領域にSTI12を形成し、その後、半導体基板11にPウェル13、Nウェル14を形成し、その後、チャネルを形成する(ステップB1;図5(A)参照)。

【0041】

ここで、STI12、Pウェル13(イオン注入など)、Nウェル14(イオン注入など)、及び、チャネル(イオン注入など)は、周知の方法で形成することができる。なお、チャネルについては、以降、図示しない。

【0042】

次に、STI12、Pウェル13、及び、Nウェル14を含む基板の主面上にゲート絶縁膜15を形成し、その後、ゲート絶縁膜15上にシリコンを主体とする第1シリコン膜16を成膜する(ステップB2;図5(B)参照)。

【0043】

ここで、ゲート絶縁膜15は、例えば、熱酸化、プラズマ酸窒化により形成することができる。また、第1シリコン膜16は、例えば、CVD法により成膜することができる。第1シリコン膜16は、後に熱処理等により多結晶化するが、本工程の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップB2ではアモルファス状態で第1シリコン膜16を成膜する方が、より好ましい。また、第1シリコン膜16の厚さは30nm以下であることが好ましい。

【0044】

次に、第1シリコン膜16の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層17を形成する(ステップB3;図5(C)参照)。

【0045】

ここで、介在層17の厚さは、1分子層以上かつ3nm以下であり、より好ましくは2nm以下である。介在層17の形成位置は、ゲート電極全体の膜厚(図6(A)の第1シリコン膜16の下面から第2シリコン膜18の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜15と第1シリコン膜16との界面から、30nm以下の位置(言い換えれば、ステップB2で形成する第1シリコン膜16の厚さは30nm以下)であると、より好ましい。

【0046】

また、介在層17の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜16を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜16の表面に介在層17となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図6(A)の18)を成膜することになる。第2の形成方法として、第1シリコン膜16を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層17となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図6(A)の18)を成膜する。

【0047】

次に、介在層17上にシリコンを主体とする第2シリコン膜18を成膜する(ステップB4;図6(A)参照)。

【0048】

ここで、第2シリコン膜18は、例えば、CVD法により成膜することができる。また、第2シリコン膜18は、後に熱処理等により多結晶化するが、ステップB4の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップB4ではアモルファス状態で成膜する方が、より好ましい。

【0049】

次に、Nウェル14が形成された領域の第2シリコン膜18上にフォトレジスト34を形成し、その後、フォトレジスト34をマスクとして、Pウェル13が形成された領域のシリコン膜18b、16bにドナーイオン(As、Pなど)を注入する(ステップB5;図6(B)参照)。その後、フォトレジスト34を除去する。

【0050】

次に、Pウェル13が形成された領域のN型第2シリコン膜18b上にフォトレジスト35を形成し、その後、フォトレジスト35をマスクとして、Nウェル14が形成された領域のシリコン膜18a、16aにアクセプタイオン(Bなど)を注入する(ステップB6;図6(C)参照)。その後、フォトレジスト35を除去する。

【0051】

なお、ステップB5とステップB6とは順序を入れ替えても良い。ステップB5及びステップB6の際、介在層17がストッパとなり、注入されたイオンがチャネル領域に達するのを防ぐ。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0052】

また、B(ホウ素)は、比較的原子量が小さいため、イオン注入時にチャネル領域に達し易い。この観点から、本発明の構成は、アクセプタイオン(特に、B)をシリコン膜18a、16aに注入したP型ゲート電極(図4の32)を有するPチャネルトランジスタ(図4の30)に適用する場合により効果的である。

【0053】

さらに、シリコン膜形成工程(ステップB2〜ステップB4)の後、イオン注入工程(ステップB5〜ステップB6)の前に、基板の加熱を要する工程(例えば、別工程で形成するトランジスタのゲート絶縁膜を形成するための熱酸化工程など)が含まれることがある。このとき、シリコン膜が多結晶化され、グレインの肥大化に伴ってラフネスが増加することがある。ラフネスが増加すると、シリコン膜が局所的に薄くなる個所が発生し、その後、注入する不純物イオンがチャネル領域に抜け易くなる。この点、実施例2によれば、シリコン膜16、18間に介在層17を配置しているため、グレインの肥大化が抑制され、シリコン膜16、18が局所的に薄くなる個所を低減できる。従って、注入イオンがチャネル領域に達するのを防ぐことができる。

【0054】

次に、基板全体を加熱処理(活性化アニール)する(ステップB7;図7(A)参照)。

【0055】

ステップB7では、加熱処理によりシリコン膜16a、16b、18a、18bに注入された不純物イオンをシリコン膜16a、16b、18a、18b全体に拡散させ活性化させる。特に、加熱処理によって不純物イオンが第1シリコン膜16a、16bに拡散する一方で、介在層17がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタの閾値電圧のばらつきを更に低減できる。なお、不純物活性化のためのアニールは、イオン注入工程(ステップB5、ステップB6)に施せばよく、このタイミングに限定されない。

【0056】

なお、ステップB7は、後のLDD形成工程(ステップB8)やソース/ドレイン形成工程(ステップB8)後のアニールなどといった他の熱処理と併用しても良い。いずれの場合でも、同様に効果的である。

【0057】

次に、ゲート電極32、33として残す領域の第2シリコン膜18a、18b上に保護膜19(例えば、シリコン窒化膜)を形成し、その後、保護膜19をマスクとして第2シリコン膜18a、18b、介在層17、第1シリコン膜16a、16b、及び、ゲート絶縁膜15を、Pウェル13及びNウェル14が表れるまでエッチングし、その後、Nウェル14形成領域上の保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁、及び、Pウェル13形成領域上の保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁にサイドウォール状のオフセットスペーサ20(例えば、シリコン窒化膜)を形成し、その後、LDD領域(Pウェル13上にはN−型LDD領域25、Nウェル14上にはP−型LDD領域23)を形成し、その後、オフセットスペーサ20の側壁にサイドウォール21(例えば、シリコン酸化膜)を形成し、その後、ソース/ドレイン領域(Pウェル13上にはN+型ソース/ドレイン領域26、Nウェル14上にはP+型ソース/ドレイン領域24)を形成する(ステップB8;図7(B)参照)。これにより、トランジスタ30、31ができる。

【0058】

ここで、保護膜19は、例えば、第2シリコン膜18a、18b上にCVD法などによりシリコン窒化膜を成膜し、その後、ゲート電極32、33として残す領域のシリコン窒化膜上にフォトレジストを形成し、当該フォトレジストをマスクとしてシリコン窒化膜を、第2シリコン膜18a、18bが表れるまでエッチングすることにより形成することができる。

【0059】

また、オフセットスペーサ20は、ゲート電極32、33を含む基板全面にCVD法などによりシリコン窒化膜を成膜し、その後、Pウェル13及びNウェル14が表れるまでシリコン窒化膜をエッチバックすることにより形成することができる。

【0060】

また、LDD領域の形成について、Pウェル13上にN−型LDD領域25を形成するときは、P型ゲート電極32を含むNウェル14が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてPウェル13にドナーイオン(As、Pなど)を注入し、その後、フォトレジストを除去する。Nウェル14上にP−型LDD領域23を形成するときは、N型ゲート電極33を含むPウェル13が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてNウェル14にアクセプタイオン(Bなど)を注入し、その後、フォトレジストを除去する。

【0061】

また、サイドウォール21は、オフセットスペーサ20及びゲート電極32、33を含む基板全面にCVD法などによりシリコン酸化膜を成膜し、その後、N−型LDD領域25及びP−型LDD領域23が表れるまでシリコン酸化膜をエッチバックすることにより形成することができる。

【0062】

さらに、ソース/ドレイン領域の形成について、Pウェル13上にN+型ソース/ドレイン領域26を形成するときは、P型ゲート電極32を含むNウェル14が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてPウェル13にドナーイオン(As、Pなど)を注入し、その後、フォトレジストを除去する。Nウェル14上にP+型ソース/ドレイン領域24を形成するときは、N型ゲート電極33を含むPウェル13が形成された領域上にフォトレジストを形成し、当該フォトレジストをマスクとしてNウェル14にアクセプタイオン(Bなど)を注入し、その後、フォトレジストを除去する。

【0063】

最後に、Pチャネルトランジスタ30及びNチャネルトランジスタ31を含む基板全面にライナー膜22(例えば、シリコン窒化膜)を成膜し、その後、ライナー膜22上に層間絶縁膜27を形成し、その後、層間絶縁膜27及びライナー膜22にソース/ドレイン領域24、26に通ずる下穴を形成し、その後、当該下穴にコンタクトプラグ28、29を形成する(ステップB9;図7(C)参照)。なお、ステップB9の後は、配線、層間絶縁膜、ビアプラグ、上層配線の形成といった周知の工程が続くことになる。

【0064】

ここで、ライナー膜22は、例えば、CVD法などによりシリコン窒化膜を成膜することにより形成することができる。層間絶縁膜27は、SOD(Spin on Dielectric;スピンオン層間絶縁膜)を用いることができる。下穴は、層間絶縁膜27上に下孔を形成する部分で開口したフォトレジストを形成し、その後、当該フォトレジストをマスクとして、層間絶縁膜27及びライナー膜22を、ソース/ドレイン領域24、26が表れるまでエッチングし、その後、フォトレジストを除去することにより形成することができる。コンタクトプラグ28、29は、例えば、下穴を含む層間絶縁膜27上に導電体膜(例えば、タングステン)を成膜し、CMP(Chemical Mechanical Polishing;化学機械研磨)により層間絶縁膜27が表れるまで研磨することにより形成することができる。

【0065】

実施形態2によれば、イオン注入工程(ステップB5、ステップB6;図6(B)、(C)参照)の際に、介在層17がストッパとなり、注入イオンがチャネル領域に達するのを防ぐことができる。これにより、トランジスタ30、31の閾値電圧のばらつきを低減できる。

【0066】

また、シリコン膜形成工程(ステップB2〜ステップB4;図5(B)〜図6(A)参照)の後、イオン注入工程(ステップB5、ステップB6;図6(B)、(C)参照)の前に、基板の加熱を要する工程が含まれる場合がある(例えば、別工程で形成するトランジスタのゲート絶縁膜を形成するための熱酸化工程など)。そのような場合に、シリコン膜が多結晶化され、グレインの肥大化に伴ってラフネスが増加することがある。このとき、シリコン膜が局所的に薄くなる個所が発生し、その後、注入する不純物イオンがチャネル領域に抜け易くなる。この点、実施形態2によれば、シリコン膜16、18間に介在層17を配置しているため、グレインの肥大化が抑制され、シリコン膜16、18が局所的に薄くなる個所を低減できる。従って、注入イオンがチャネル領域に達するのを防ぐことができる。

【0067】

さらに、実施形態2によれば、加熱処理(ステップB7;図7(A)参照)によって不純物イオンが第1シリコン膜16に拡散する一方で、介在層17がストッパとなり、チャネル領域にまで達する不純物イオンの量が低減する。これにより、トランジスタ30、31の閾値電圧のばらつきを更に低減できる。

【0068】

[実施形態3]

本発明の実施形態3に係る半導体装置について図面を用いて説明する。図8は、本発明の実施形態3に係る半導体装置の構成を模式的に示した平面図である。図9は、本発明の実施形態3に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。図10は、本発明の実施形態3に係る半導体装置におけるメモリセル領域の構成を模式的に示した(A)平面図、(B)Y−Y´間の断面図である。

【0069】

実施形態3は、実施形態2のゲート電極(図4の32、33)の構造を6F2/bWL型DRAM(Dynamic Random Access Memory)チップ36における周辺回路領域38のゲート電極32、33に応用したものである。

【0070】

図8を参照すると、DRAMチップ36は、メモリセルアレイが形成された複数のメモリセル領域37が行方向及び列方向に配置されており、各メモリセル領域37の周囲には、IOバッファなどの周辺回路が形成された周辺回路領域38が配置されている。

【0071】

図9を参照すると、周辺回路領域38では、実施形態2(図4参照)と同様なCMOSトランジスタが形成されている。ただし、P型ゲート電極32においては、P型第2シリコン膜18aと保護膜19との間にて、下側から順にP型第3シリコン膜43a及び導電膜44が介在している。同様に、N型ゲート電極33においても、N型第2シリコン膜18bと保護膜19との間にて、下側から順にN型第3シリコン膜43b及び導電膜44が介在している。また、コンタクトプラグ28、29(保護膜19を含めても可)を含む層間絶縁膜27上の一部には、Nチャネルトランジスタ31のN+型ソース/ドレイン領域26とコンタクトプラグ28を介して電気的に接続された配線46aと、Pチャネルトランジスタ30のP+型ソース/ドレイン領域24とコンタクトプラグ29を介して電気的に接続された配線46bと、が形成されている。配線46a、46bを含む基板全面には、エッチングストッパ膜47が形成されている。エッチングストッパ膜47上には層間絶縁膜48が形成されている。

【0072】

図10を参照すると、メモリセル領域37においては、6F2(設計ルール上のセル面積)/bWL(buried Word Line;埋込ワード線)型のメモリセルが形成されている。メモリセル領域37では、半導体基板11(例えば、シリコン基板)上に素子(トランジスタ)間を電気的に分離するSTI(Shallow Trench Isolation;例えば、シリコン酸化膜)12が形成されている。STI12で囲まれた領域において半導体基板11に2つのトレンチ(図13(A)の11a)が形成されており、当該トレンチの表面(底面、側壁面)にゲート絶縁膜39(例えば、シリコン酸化膜)が形成されており、当該トレンチにおいて完全に満たされない状態でゲート絶縁膜39を介して埋込ワード線40(例えば、金属膜など)が埋め込まれている。埋込ワード線40は、ゲート電極となる。埋込ワード線40とSTI12との間の領域の半導体基板11及びSTI12上には、周辺回路領域(図9の38)のPチャネルトランジスタ(図9の30)及びNチャネルトランジスタ(図9の31)において用いられているゲート絶縁膜(図9の15)と同層のゲート絶縁膜15が形成されている。埋込ワード線40間の領域の半導体基板11上には、ゲート絶縁膜15及びゲート絶縁膜39が形成されていない。ゲート絶縁膜15、39及び埋込ワード線40上にはビットコンタクト層間絶縁膜42(例えば、シリコン酸化膜)が形成されている。ビットコンタクト層間絶縁膜42は、埋込ワード線40間の領域の半導体基板11上に形成されていない。埋込ワード線40間の領域の半導体基板11を含むビットコンタクト層間絶縁膜42上の一部には、半導体基板11(ソース領域となる部分)に接続されたN型第3シリコン膜43c(BL;ビット線)が形成されており、N型第3シリコン膜43c上に導電膜44(例えば、金属膜、シリサイド膜など)を介して保護膜19(例えば、シリコン窒化膜)が形成されている。保護膜19、導電膜44、及び埋込ワード線40の側壁面ないしビットコンタクト層間絶縁膜42の表面には、ライナー膜22(例えば、シリコン窒化膜)が形成されている。ライナー膜22上には、層間絶縁膜27(例えば、シリコン酸化膜)が形成されている。層間絶縁膜27は、保護膜19上を覆っていない(覆っていても可)。層間絶縁膜27、ライナー膜22、ビットコンタクト層間絶縁膜42、及びゲート絶縁膜15には、埋込ワード線40とSTI12との間の領域の半導体基板11(ドレイン領域となる部分)に通ずる下穴が形成されており、当該下穴に容量コンタクトプラグ45(例えば、タングステン)が埋め込まれている。

【0073】

メモリセル領域37では、容量コンタクトプラグ45(保護膜19を含めても可)を含む層間絶縁膜27上の一部には、容量コンタクトプラグ45と接続された容量コンタクトパッド46c(例えば、金属膜)が形成されている。容量コンタクトパッド46c及び保護膜19を含む層間絶縁膜27上には、エッチングストッパ膜47(例えば、シリコン窒化膜)が形成されている。エッチングストッパ膜47には、容量コンタクトパッド46cに通ずる開口部が形成されている。容量コンタクトパッド46c上にはクラウン状のキャパシタ50が形成されている。キャパシタ50は、下側から順に、導電膜51(下部電極)、誘電膜52(容量膜)、導電膜53(上部電極)が形成されている。導電膜51は、容量コンタクトパッド46cと接続されている。誘電膜52及び導電膜53は、エッチングストッパ膜47上にも形成されている。導電膜53上には、プレート電極54(例えば、金属膜)が形成されている。

【0074】

次に、本発明の実施形態3に係る半導体装置の製造方法について図面を用いて説明する。図11〜図15は、本発明の実施形態3に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0075】

まず、半導体基板1上の素子分離領域にSTI12を形成し、その後、メモリセル領域37の半導体基板11中にディープNウェル(図示せず)を形成し、その後、周辺回路領域38の半導体基板11にPウェル13、Nウェル14を形成し、その後、チャネル(図示せず)を形成し、その後、STI12、Pウェル13、及び、Nウェル14を含む基板の主面上にゲート絶縁膜15を形成する(ステップC1;図11(A)参照)。

【0076】

ここで、STI12、ディープNウェル(図示せず;イオン注入など)、Pウェル13(イオン注入など)、Nウェル14(イオン注入など)、チャネル(図示せず;イオン注入など)、及び、ゲート絶縁膜15(例えば、熱酸化、プラズマ酸窒化)は、周知の方法で形成することができる。

【0077】

次に、ゲート絶縁膜15上にシリコンを主体とする第1シリコン膜16を成膜する(ステップC2;図11(B)参照)。

【0078】

ここで、第1シリコン膜16は、周辺回路領域38のゲート電極(図9の32、33)となるものであるが、この段階ではメモリセル領域37にも形成される。第1シリコン膜16は、例えば、CVD法により成膜することができる。第1シリコン膜16は、後に熱処理等により多結晶化するが、本工程の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップC2ではアモルファス状態で第1シリコン膜16を成膜する方が、より好ましい。また、第1シリコン膜16の厚さは30nm以下であることが好ましい。

【0079】

次に、第1シリコン膜16の表面に酸素及び窒素のうち一方又は両方を供給して、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層17を形成する(ステップC3;図12(A)参照)。

【0080】

ここで、介在層17の厚さは、1分子層以上かつ3nm以下であり、より好ましくは2nm以下である。介在層17の形成位置は、ゲート電極全体の膜厚(図12(B)の第1シリコン膜16の下面から第2シリコン膜18の上面までの膜厚)の半分より下に形成することが好ましい。特に、ゲート絶縁膜15と第1シリコン膜16との界面から、30nm以下の位置(言い換えれば、ステップC2で形成する第1シリコン膜16の厚さは30nm以下)であると、より好ましい。

【0081】

また、介在層17の形成方法として、以下の2種類の方法が挙げられる。第1の形成方法として、第1シリコン膜16を成膜した後、同一チャンバ内に酸素及び窒素のうち一方又は両方のガスを供給する。これにより、第1シリコン膜16の表面に介在層17となる薄いシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜が形成される。その後、同一チャンバ内で、第2シリコン膜(図12(B)の18)を成膜することになる。第2の形成方法として、第1シリコン膜16を成膜した後、他のチャンバ移して酸化又は窒化若しくは酸窒化処理するか、或いは、他のチャンバに移して介在層17となるシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成する。その後、元のチャンバ内で第2シリコン膜(図12(B)の18)を成膜する。

【0082】

次に、介在層17上にシリコンを主体とする第2シリコン膜18を成膜する(ステップC4;図12(B)参照)。

【0083】

ここで、第2シリコン膜18は、例えば、CVD法により成膜することができる。また、第2シリコン膜18は、後に熱処理等により多結晶化するが、ステップC4の成膜時点では、多結晶であっても、アモルファスであっても良い。ただし、加熱による多結晶化の際のグレインサイズ拡大による表面ラフネス増加を抑えるために、ステップC4ではアモルファス状態で成膜する方が、より好ましい。

【0084】

次に、メモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16を除去し、その後、基板上に埋込ワード線(図10の40)形成用のハードマスク49を形成し、その後、ハードマスク49をマスクとしてゲート絶縁膜15及び半導体基板11をエッチングすることによりトレンチ11aを形成する(ステップC5;図13(A)参照)。

【0085】

ここで、メモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16の除去では、例えば、周辺回路領域38の第2シリコン膜18上にフォトレジストを形成し、その後、当該フォトレジストをマスクとしてメモリセル領域37の第2シリコン膜18、介在層17、及び第1シリコン膜16をエッチングすることによりトレンチ11aを形成し、その後、フォトレジストを除去する。

【0086】

また、ハードマスク49には、例えば、シリコン酸化膜、シリコン窒化膜、その他半導体基板11のドライエッチングに対して選択性の高い膜を用いることができる。また、ハードマスク49は、例えば、基板全面にハードマスク49を成膜(例えば、CVD法)し、その後、ハードマスク49上に、埋込ワード線(図10の40)形成用の開口部を有するフォトレジストを形成し、その後、当該フォトレジストをマスクとしてハードマスク49をエッチングし、その後、フォトレジストを除去することにより形成することができる。

【0087】

さらに、トレンチ11aの形成では、例えば、STI12の底面よりも深くならない程度の深さまで、ゲート絶縁膜15の半導体基板11をドライエッチングすることにより形成することができる。

【0088】

次に、基板全面に、メモリセル領域37のトランジスタ用のゲート絶縁膜39(例えば、シリコン酸化膜)を形成する(ステップC6;図13(B)参照)。

【0089】

ここで、ゲート絶縁膜39は、例えば、熱酸化又はプラズマ酸窒化により形成することができる。この熱処理により、先に形成した周辺回路領域38のシリコン膜16、18が多結晶化されるが、本発明ではシリコン膜16、18間に介在層17を介在させたことにより、多結晶化の際のグレインの肥大化が抑制される。従って、当該シリコン膜16、18が局所的に薄くなる個所が発生し難い。これにより、後のステップC8及びステップC9における当該シリコン膜16a、16b、18a、18bへの不純物イオン注入の際、局所的に薄い個所を介したチャネル領域へのイオン抜けが低減される。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0090】

なお、シリコン膜16、18の多結晶化によるグレインの肥大化をもたらす熱処理は、ステップC6のメモリセル領域37のトランジスタ用のゲート絶縁膜39の形成に限定されない。即ち、周辺回路領域38のゲート電極となるシリコン膜16、18を形成した後に熱処理を施す工程およびイオン注入を施す工程を有していれば、本発明の介在層17を適用することにより、同様に効果的である。ただし、メモリセル領域37のトランジスタのゲート絶縁膜39はより高い温度での熱処理を要することから、先に形成した周辺回路領域38のシリコン膜16、18のグレインサイズがより肥大化することが懸念される。従って、ステップC6のように、周辺回路領域38にシリコン膜16、18を形成した後に、メモリセル領域37のトランジスタのゲート絶縁膜39を形成するための熱処理を施す工程を有する半導体装置の製造方法に、本発明の介在層17を適用すれば、より効果的である。

【0091】

次に、トレンチ(図13(A)の11a)内のゲート絶縁膜39上に埋込ワード線40(例えば、導電膜)を形成し、その後、ゲート絶縁膜39(ハードマスク49上にある部分)及びハードマスク49を除去し、その後、基板全面にビットコンタクト層間絶縁膜42(例えば、シリコン酸化膜)を成膜し、その後、ビットコンタクト層間絶縁膜42において埋込ワード線40間の領域の半導体基板11(ソース領域となる部分)に通ずる開口部を形成し、その後、基板全面に第3シリコン膜43を成膜する(ステップC7;図14(A)参照)。

【0092】

ここで、埋込ワード線40は、例えば、基板全面に導電膜を堆積し、その後、エッチバックにより不要な導電膜を除去することにより、トレンチ(図13(A)の11a)内のゲート絶縁膜39上に埋込ワード線40を形成することができる。

【0093】

また、ビットコンタクト層間絶縁膜42における開口部の形成は、例えば、ビットコンタクト層間絶縁膜42上に、開口部形成用のフォトレジストを形成し、その後、当該フォトレジストをマスクとしてビットコンタクト層間絶縁膜42をエッチングすることにより開口部を形成することができる。

【0094】

さらに、第3シリコン膜43は、例えば、CVD法によって成膜することができる。第3シリコン膜43は、周辺回路領域38ではゲート電極(図9の32、33)の一部になり、メモリセル領域37ではビット線の一部になる。

【0095】

次に、周辺回路領域38のNウェル14が形成された領域の第3シリコン膜43上にフォトレジスト34を形成し、その後、フォトレジスト34をマスクとして、周辺回路領域38のPウェル13が形成された領域、及び、メモリセル領域37のシリコン膜18b、16b、43b及び43cにドナーイオン(As、Pなど)を注入する(ステップC8;図14(B)参照)。その後、フォトレジスト34を除去する。

【0096】

次に、周辺回路領域38のPウェル13が形成された領域、及び、メモリセル領域37のN型第3シリコン膜43b及び43c上にフォトレジスト35を形成し、その後、フォトレジスト35をマスクとして、周辺回路領域38のNウェル14が形成された領域のシリコン膜43a、18a、16aにアクセプタイオン(Bなど)を注入する(ステップC9;図15(A)参照)。その後、フォトレジスト35を除去する。

【0097】

なお、ステップC8とステップC9とは順序を入れ替えても良い。ステップC8及びステップC9の際、介在層17がストッパとなり、注入されたイオンがチャネル領域に達するのを防ぐ。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0098】

また、実施形態3では、シリコン膜16a、18a間及び16b、18b間に介在層17を導入したことで、ステップC6などの熱処理(ゲート絶縁膜39の形成)においてシリコン膜16a、16b、18a、18b、43a、43bのグレインの肥大化によるラフネスの増大が抑制される。これにより、シリコン膜16a、16b、18a、18b、43a、43bが局所的に薄くなる個所が発生し難い。従って、ステップC8及びステップC9で当該シリコン膜16a、16b、18a、18bにイオン注入を施す際、不純物イオンがシリコン膜16a、16b、18a、18b、43a、43bの局所的に薄い個所を介してチャネル領域に注入されるのを防ぐことができる。結果として、トランジスタの閾値電圧のばらつきを低減できる。

【0099】

さらに、シリコン膜16a、18a間及び16b、18b間に介在層17を導入したことで、チャネル領域にまで達する注入イオンの量を低減できる。そして、注入された不純物イオンの拡散および活性化のためのアニールにおいても、チャネル領域にまで達するイオンを低減できる。結果として、トランジスタの閾値電圧のばらつきを更に低減できる。この作用効果は、B(ホウ素)を注入するPチャネルトランジスタのP型ゲート電極(図9の32)に対してより効果的である。

【0100】

次に、基板全体を加熱処理(活性化アニール)し、その後、基板全面に導電膜44(例えば、金属膜、シリサイド膜)を成膜し、その後、ゲート電極32、33及びビット線(N型第3シリコン膜43c)として残す領域の導電膜44上に保護膜19(例えば、シリコン窒化膜)を形成し、その後、保護膜19をマスクとして導電膜44、第3シリコン膜43a、43b、43c、第2シリコン膜18a、18b、介在層17、第1シリコン膜16a、16b、及び、ゲート絶縁膜15を、Pウェル13及びNウェル14が表れるまでエッチングし、その後、周辺回路領域38でのみ、Nウェル14形成領域上の保護膜19、P型第2シリコン膜18a、介在層17、P型第1シリコン膜16a、及び、ゲート絶縁膜15の側壁、及び、Pウェル13形成領域上の保護膜19、N型第2シリコン膜18b、介在層17、N型第1シリコン膜16b、及び、ゲート絶縁膜15の側壁にサイドウォール状のオフセットスペーサ20(例えば、シリコン窒化膜)を形成し、その後、LDD領域(Pウェル13上にはN−型LDD領域25、Nウェル14上にはP−型LDD領域23)を形成し、その後、周辺回路領域38でのみ、オフセットスペーサ20の側壁にサイドウォール21(例えば、シリコン酸化膜)を形成し、その後、ソース/ドレイン領域(Pウェル13上にはN+型ソース/ドレイン領域26、Nウェル14上にはP+型ソース/ドレイン領域24)を形成する(ステップC10;図15(B)参照)。これにより、メモリセル領域37のビット線、及び、周辺回路領域38のトランジスタが完成する。

【0101】

なお、導電膜44は、周辺回路領域38ではゲート電極32、33の一部になり、メモリセル領域37ではビット線(BL)の一部になる。また、加熱処理、保護膜19の形成、オフセットスペーサ20の形成、LDD領域23、25の形成、サイドウォール21の形成、及び、ソース/ドレイン領域24、26の形成については、実施形態2のステップB7、ステップB8と同様である。

【0102】

最後に、Pチャネルトランジスタ30及びNチャネルトランジスタ31並びにビット線(N型第3シリコン膜43c)を含む基板全面にライナー膜22(例えば、シリコン窒化膜)を成膜し、その後、ライナー膜22上に層間絶縁膜27を形成し、その後、基板の表面を平坦化(例えば、CMP)し、その後、周辺回路領域38において層間絶縁膜27及びライナー膜22にソース/ドレイン領域24、26に通ずる下穴を形成し、メモリセル領域37において埋込ワード線40とSTI12との間の領域の半導体基板11(ドレイン領域となる部分)に通ずる下穴を形成し、その後、当該下穴にコンタクトプラグ28、29及び容量コンタクトプラグ45(例えば、タングステン)を形成し、その後、コンタクトプラグ28、29及び容量コンタクトプラグ45を含む層間絶縁膜27上の一部に、コンタクトプラグ28に接続される配線46a、コンタクトプラグ29に接続される配線46b、及び、容量コンタクトプラグ45に接続される容量コンタクトパッド46c(例えば、導電膜)を形成し、その後、配線46a、46b及び容量コンタクトパッド46cを含む層間絶縁膜27上にエッチングストッパ膜47(例えば、シリコン窒化膜)を形成し、その後、クラウンキャパシタ50を形成する(ステップC11;図9、図10参照)。なお、ステップC11の後は、配線、層間絶縁膜、ビアプラグ、上層配線の形成といった周知の工程が続くことになる。

【0103】

ここで、配線46a、46b及び容量コンタクトパッド46cは、例えば、基板全面にCVD法などにより導電膜を成膜し、その後、配線46a、46b及び容量コンタクトパッド46cとして残す領域の導電膜上にフォトレジストを形成し、当該フォトレジストをマスクとして導電膜を、層間絶縁膜27が表れるまでエッチングすることにより形成することができる。

【0104】

また、クラウンキャパシタ50は、例えば、エッチングストッパ膜47上に層間絶縁膜48(例えば、シリコン酸化膜)を形成し、その後、メモリセル領域37における層間絶縁膜48及びエッチングストッパ47に容量コンタクトパッド46cに通ずる下穴を形成し、その後、当該下穴の表面(底面、側壁面)に導電膜51(下部電極)を形成し、その後、メモリセル領域37における層間絶縁膜48をエッチングにより除去し、その後、メモリセル領域37の全面に誘電膜52(容量膜)を形成し、その後、誘電膜52上に導電膜53(上部電極)を形成し、その後、メモリセル領域37において導電膜53上にプレート電極54を形成することにより形成することができる。

【0105】

なお、ライナー膜22の形成、層間絶縁膜27の形成、下穴の形成、コンタクトプラグ28、29及び容量コンタクトプラグ45の形成は、実施形態2のステップB9と同様である。

【0106】

実施形態3によれば、メモリセル領域37のトランジスタ用のゲート絶縁膜39の形成の際の熱処理により、先に形成した周辺回路領域38のシリコン膜16、18が多結晶化されるが、本発明ではシリコン膜16、18間に介在層17を導入したことにより、多結晶化の際のグレインの肥大化が抑制される。従って、当該シリコン膜16、18が局所的に薄くなる個所が発生し難い。これにより、後のステップC8およびステップC9における当該シリコン膜16a、16b、18a、18b、43a、43bへの不純物イオン注入の際、局所的に薄い個所を介したチャネル領域へのイオン抜けが低減される。これにより、トランジスタの閾値電圧のばらつきを低減できる。

【0107】

また、実施形態3によれば、シリコン膜16、18間に介在層17を導入したことで、チャネル領域にまで達する注入イオンの量を低減できる。そして、注入不純物の拡散および活性化のためのアニールにおいても、チャネル領域にまで達するイオンを低減できる。結果として、トランジスタの閾値電圧のばらつきを更に低減できる。この効果は、B(ホウ素)を注入するPチャネルトランジスタ30に対してより効果的である。

【0108】

[実施形態4]

本発明の実施形態4に係る半導体装置について図面を用いて説明する。図16は、本発明の実施形態4に係る半導体装置における周辺回路領域の構成を模式的に示した(A)平面図、(B)X−X´間の断面図である。

【0109】

実施形態4は、実施形態3の変形例であり、周辺回路領域38のゲート電極32、33において2層の介在層17、41を設けたものである。介在層17は、実施形態2と同様に、シリコン膜16a、18a間及びシリコン膜16b、18b間に導入された酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする層である。介在層41は、シリコン膜18a、43a間及びシリコン膜18b、43b間に導入された酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする層である。なお、周辺回路領域38におけるその他の構成、及び、メモリセル領域(図示せず)の構成は、実施形態3と同様である。

【0110】

次に、本発明の実施形態4に係る半導体装置の製造方法について図面を用いて説明する。図17は、本発明の実施形態4に係る半導体装置の製造方法を模式的に示した工程断面図である。

【0111】

まず、実施形態3のステップC1〜ステップC4と同様に、半導体基板11上にSTI12、Pウェル13、Nウェル14、ゲート絶縁膜15、第1シリコン膜16、介在層17、及び第2シリコン膜18を形成する(ステップD1;図17(A)参照)。

【0112】

次に、第2シリコン膜18上に介在層41を形成する(ステップD2;図17(B)参照)。なお、介在層41は、介在層17と同様な方法により形成することができる。

【0113】

その後、実施形態3のステップC5〜ステップC11と同様な工程を行う(ステップD3)。

【0114】

実施形態4によれば、実施形態2、3と同様な効果を奏するとともに、2層の介在層17、41を設けることで、例えば、イオン注入のバリア効果(実施形態2)とグレイン肥大化抑制効果(実施形態3)とで、要求される膜厚や形成位置が異なる場合などにも対応できる。

【0115】

なお、本出願において図面参照符号を付している場合は、それらは、専ら理解を助けるためのものであり、図示の態様に限定することを意図するものではない。

【0116】

また、本発明の全開示(請求の範囲及び図面を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲及び図面を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0117】

1 半導体基板

2 ゲート絶縁膜

3 第1シリコン膜

3a 第1ゲート電極膜

4 介在層

5 第2シリコン膜

5a 第2ゲート電極膜

6 ソース/ドレイン領域

7 レジスト

11 半導体基板

11a トレンチ

12 STI

13 Pウェル

14 Nウェル

15 ゲート絶縁膜

16 第1シリコン膜

16a P型第1シリコン膜(第1ゲート電極膜)

16b N型第1シリコン膜(第1ゲート電極膜)

17 介在層

18 第2シリコン膜

18a P型第2シリコン膜(第2ゲート電極膜)

18b N型第2シリコン膜(第2ゲート電極膜)

19 保護膜

20 オフセットスペーサ

21 サイドウォール

22 ライナー膜

23 P−型LDD領域

24 P+型ソース/ドレイン領域

25 N−型LDD領域

26 N+型ソース/ドレイン領域

27 層間絶縁膜

28、29 コンタクトプラグ

30 Pチャネルトランジスタ

31 Nチャネルトランジスタ

32 P型ゲート電極

33 N型ゲート電極

34、35 フォトレジスト

36 DRAMチップ

37 メモリセル領域

38 周辺回路領域

39 ゲート絶縁膜(第2ゲート絶縁膜)

40 埋込ワード線(bWL)

41 介在層(第2介在層)

42 ビットコンタクト層間絶縁膜

43 第3シリコン膜

43a P型第3シリコン膜(第3ゲート電極膜)

43b N型第3シリコン膜(第3ゲート電極膜)

43c N型第3シリコン膜(BL、ビット線)

44 導電膜

45 容量コンタクトプラグ

46a、46b 配線

46c 容量コンタクトパッド

47 エッチングストッパ膜

48 層間絶縁膜

49 ハードマスク

50 キャパシタ

51 導電膜(下部電極)

52 誘電膜(容量膜)

53 導電膜(上部電極)

54 プレート電極

【特許請求の範囲】

【請求項1】

半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、

前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、

前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、

を含む電界効果トランジスタを有することを特徴とする半導体装置。

【請求項2】

前記介在層の厚さは、1分子層以上かつ3nm以下であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記介在層の厚さは、2nm以下であることを特徴とする請求項2記載の半導体装置。

【請求項4】

前記介在層の形成位置は、前記第1ゲート電極膜、前記介在層、及び前記第2ゲート電極膜を含むゲート電極全体の膜厚の半分より下であることを特徴とする請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

前記第1ゲート電極膜の厚さは、30nm以下であることを特徴とする請求項4記載の半導体装置。

【請求項6】

前記第1導電型となる不純物は、ホウ素であることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項7】

前記電界効果トランジスタが形成される領域以外の領域において、

前記半導体基板の主面上に他のゲート絶縁膜を介して形成されるとともに、前記第1ゲート電極膜と同層に形成され、かつ、前記第1導電型とは反対導電型の第2導電型となる不純物を含んだシリコンを主体とする他の第1ゲート電極膜と、

前記他の第1ゲート電極膜上に形成されるとともに、前記介在層と同層に形成され、かつ、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする他の介在層と、

前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第2ゲート電極膜と同層に形成され、かつ、前記第2導電型となる不純物を含んだシリコンを主体とする他の第2ゲート電極膜と、

を含む他の電界効果トランジスタを有することを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項8】

前記電界効果トランジスタは、前記第2ゲート電極膜上に形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第3ゲート電極膜を含むことを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項9】

前記電界効果トランジスタは、

前記第2ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする第2介在層と、

前記第1ゲート電極膜上に前記第2介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第3ゲート電極膜と、

を含むことを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項10】

前記半導体装置は、メモリセルが形成されたメモリセル領域と、前記メモリセル領域の周辺にて回路が形成された周辺回路領域と、を有し、

前記電界効果トランジスタは、前記周辺回路領域に形成され、

前記メモリセル領域では、

前記半導体基板に形成されたトレンチと、

前記トレンチ内に前記ゲート絶縁膜とは異なる第2ゲート絶縁膜を介して形成された埋込ワード線と、

を含む埋込ワード線型のメモリセルを有することを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項11】

半導体基板の主面上に、絶縁膜を介してシリコンを主体とする第1シリコン膜を形成する工程と、

前記第1シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層を形成する工程と、

前記第1シリコン膜上に、前記介在層を介してシリコンを主体とする第2シリコン膜を形成する工程と、

前記第1シリコン膜及び前記第2シリコン膜に対して、前記第2シリコン膜側から不純物イオンを注入する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項12】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと同一のチャンバ内で前記第1シリコン膜の表面に酸素及び窒素のうち一方又は両方を供給することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと異なるチャンバ内で前記第1シリコン膜の表面に酸素及び窒素のうち一方又は両方を供給することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項14】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと異なるチャンバ内でシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項15】

前記第1シリコン膜を形成する工程では、前記第1シリコン膜をアモルファス状態で成膜することを特徴とする請求項11乃至14のいずれか一に記載の半導体装置の製造方法。

【請求項16】

前記第2シリコン膜を形成する工程では、前記第2シリコン膜をアモルファス状態で成膜することを特徴とする請求項11乃至15のいずれか一に記載の半導体装置の製造方法。

【請求項17】

前記不純物イオンを注入する工程では、アクセプタイオンを注入することを特徴とする請求項11乃至16のいずれか一に記載の半導体装置の製造方法。

【請求項18】

前記不純物イオンを注入する工程では、ホウ素イオンを注入することを特徴とする請求項17記載の半導体装置の製造方法。

【請求項19】

前記不純物イオンを注入する工程では、前記半導体装置におけるPチャネルトランジスタを形成する領域でアクセプタイオンを注入し、かつ、前記半導体装置におけるNチャネルトランジスタを形成する領域でドナーイオンを注入することを特徴とする請求項11乃至16のいずれか一に記載の半導体装置の製造方法。

【請求項20】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、前記第2シリコン膜上に、シリコンを主体とする第3シリコン膜を形成する工程を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【請求項21】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、

前記第2シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする第2介在層を形成する工程と、

前記第2シリコン膜上に、前記第2介在層を介してシリコンを主体とする第3シリコン膜を形成する工程と、

を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【請求項22】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、

メモリセルが形成されたメモリセル領域と、前記メモリセル領域の周辺にて回路が形成された周辺回路領域と、を有する前記半導体装置における前記メモリセル領域に形成された前記第2シリコン膜、前記介在層、及び前記第1シリコン膜を除去する工程と、

前記メモリセル領域の前記半導体基板にトレンチを形成する工程と、

前記トレンチの表面にゲート絶縁膜を形成するための熱処理を施す工程と、

を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【請求項1】

半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、

前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、

前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、

を含む電界効果トランジスタを有することを特徴とする半導体装置。

【請求項2】

前記介在層の厚さは、1分子層以上かつ3nm以下であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記介在層の厚さは、2nm以下であることを特徴とする請求項2記載の半導体装置。

【請求項4】

前記介在層の形成位置は、前記第1ゲート電極膜、前記介在層、及び前記第2ゲート電極膜を含むゲート電極全体の膜厚の半分より下であることを特徴とする請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

前記第1ゲート電極膜の厚さは、30nm以下であることを特徴とする請求項4記載の半導体装置。

【請求項6】

前記第1導電型となる不純物は、ホウ素であることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項7】

前記電界効果トランジスタが形成される領域以外の領域において、

前記半導体基板の主面上に他のゲート絶縁膜を介して形成されるとともに、前記第1ゲート電極膜と同層に形成され、かつ、前記第1導電型とは反対導電型の第2導電型となる不純物を含んだシリコンを主体とする他の第1ゲート電極膜と、

前記他の第1ゲート電極膜上に形成されるとともに、前記介在層と同層に形成され、かつ、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする他の介在層と、

前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第2ゲート電極膜と同層に形成され、かつ、前記第2導電型となる不純物を含んだシリコンを主体とする他の第2ゲート電極膜と、

を含む他の電界効果トランジスタを有することを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項8】

前記電界効果トランジスタは、前記第2ゲート電極膜上に形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第3ゲート電極膜を含むことを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項9】

前記電界効果トランジスタは、

前記第2ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする第2介在層と、

前記第1ゲート電極膜上に前記第2介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第3ゲート電極膜と、

を含むことを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項10】

前記半導体装置は、メモリセルが形成されたメモリセル領域と、前記メモリセル領域の周辺にて回路が形成された周辺回路領域と、を有し、

前記電界効果トランジスタは、前記周辺回路領域に形成され、

前記メモリセル領域では、

前記半導体基板に形成されたトレンチと、

前記トレンチ内に前記ゲート絶縁膜とは異なる第2ゲート絶縁膜を介して形成された埋込ワード線と、

を含む埋込ワード線型のメモリセルを有することを特徴とする請求項1乃至6のいずれか一に記載の半導体装置。

【請求項11】

半導体基板の主面上に、絶縁膜を介してシリコンを主体とする第1シリコン膜を形成する工程と、

前記第1シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層を形成する工程と、

前記第1シリコン膜上に、前記介在層を介してシリコンを主体とする第2シリコン膜を形成する工程と、

前記第1シリコン膜及び前記第2シリコン膜に対して、前記第2シリコン膜側から不純物イオンを注入する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項12】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと同一のチャンバ内で前記第1シリコン膜の表面に酸素及び窒素のうち一方又は両方を供給することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと異なるチャンバ内で前記第1シリコン膜の表面に酸素及び窒素のうち一方又は両方を供給することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項14】

前記介在層を形成する工程では、前記第1シリコン膜を形成する工程で使用したチャンバと異なるチャンバ内でシリコン酸化膜又はシリコン窒化膜若しくはシリコン酸窒化膜を形成することで前記介在層を形成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項15】

前記第1シリコン膜を形成する工程では、前記第1シリコン膜をアモルファス状態で成膜することを特徴とする請求項11乃至14のいずれか一に記載の半導体装置の製造方法。

【請求項16】

前記第2シリコン膜を形成する工程では、前記第2シリコン膜をアモルファス状態で成膜することを特徴とする請求項11乃至15のいずれか一に記載の半導体装置の製造方法。

【請求項17】

前記不純物イオンを注入する工程では、アクセプタイオンを注入することを特徴とする請求項11乃至16のいずれか一に記載の半導体装置の製造方法。

【請求項18】

前記不純物イオンを注入する工程では、ホウ素イオンを注入することを特徴とする請求項17記載の半導体装置の製造方法。

【請求項19】

前記不純物イオンを注入する工程では、前記半導体装置におけるPチャネルトランジスタを形成する領域でアクセプタイオンを注入し、かつ、前記半導体装置におけるNチャネルトランジスタを形成する領域でドナーイオンを注入することを特徴とする請求項11乃至16のいずれか一に記載の半導体装置の製造方法。

【請求項20】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、前記第2シリコン膜上に、シリコンを主体とする第3シリコン膜を形成する工程を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【請求項21】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、

前記第2シリコン膜上に、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする第2介在層を形成する工程と、

前記第2シリコン膜上に、前記第2介在層を介してシリコンを主体とする第3シリコン膜を形成する工程と、

を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【請求項22】

前記第2シリコン膜を形成する工程の後、かつ、前記不純物イオンを注入する工程の前において、

メモリセルが形成されたメモリセル領域と、前記メモリセル領域の周辺にて回路が形成された周辺回路領域と、を有する前記半導体装置における前記メモリセル領域に形成された前記第2シリコン膜、前記介在層、及び前記第1シリコン膜を除去する工程と、

前記メモリセル領域の前記半導体基板にトレンチを形成する工程と、

前記トレンチの表面にゲート絶縁膜を形成するための熱処理を施す工程と、

を含むことを特徴とする請求項11乃至19のいずれか一に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−74189(P2013−74189A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−213120(P2011−213120)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]