Fターム[5F140AA28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 突き抜け、チャネリング防止 (127)

Fターム[5F140AA28]に分類される特許

1 - 20 / 127

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

絶縁膜の改質方法

【課題】 プラズマ窒化処理によって形成した酸化窒化珪素膜からのN抜けによる膜中窒素濃度の低下を抑制し、被処理体間・ロット間での窒素濃度のばらつきを最小限にする。

【解決手段】 絶縁膜の改質方法は、被処理体の表面に露出した酸化珪素膜をプラズマ窒化処理し、酸化窒化珪素膜を形成する窒化処理工程と、前記酸化窒化珪素膜の表面を酸化処理する改質工程とを行い、窒化処理工程の終了から前記改質工程の開始までの間、真空雰囲気を維持する。また、プラズマ窒化処理は、窒化処理工程直後の酸化窒化珪素膜の膜中窒素濃度をNC0とし、改質工程後の酸化窒化珪素膜の膜中窒素濃度の目標値をNCTとしたとき、NC0>NCTとなるように行う。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

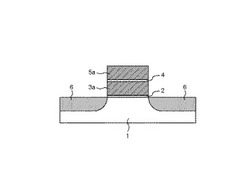

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

半導体装置及びその製造方法

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の空乏化と、ゲート電極内の不純物量の減少ないしはバラつきと、イオンがゲート絶縁膜を突き抜けてしまうことに起因したゲート絶縁膜の信頼性低下及び閾値変動を抑制する。

【解決手段】第1注入工程(図1(b)、図1(c))と第2注入工程(図1(d)、図1(e))を備える。第1注入工程ではゲート絶縁膜5と、ゲート電極9、10となる膜6と、が形成された半導体基板1のゲート電極9、10となる部分に、n型又はp型の導電型のイオンを注入する。第2注入工程では、ゲート電極9、10に同じ導電型のイオンを注入する。第1注入工程で注入するイオンの質量は、第2注入工程で注入するイオンよりも大きくする。これにより第1注入工程による不純物の濃度分布の縦方向におけるピーク位置を、第2注入工程による不純物のピーク位置よりもゲート絶縁膜5寄りにする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁膜のプラズマ処理方法を提供する。

【解決手段】本発明に係るプラズマ処理方法の一形態は、絶縁膜が形成された基板を真空容器内に搬入する工程と、上記真空容器内に供給された処理ガスに300MHz以上2500MHz以下の周波数を有する高周波電力を供給することによりプラズマを生成し、上記プラズマにより、上記絶縁膜を改質する工程と、を含むプラズマ処理方法であって、上記処理ガスは、希ガスと酸素を含む混合ガス、または希ガスと窒素を含む混合ガスであり、上記プラズマは、上記処理ガスが希ガスと酸素を含む混合ガスの場合、上記酸素ガスの流量を1〜1000sccm、上記希ガスの流量を200〜3000sccmとして、上記処理ガスが希ガスと窒素を含むガスの場合、窒素ガスの流量を10〜500sccm、上記希ガスの流量を200〜3000sccmとして生成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】

半導体基板1の主面にゲート絶縁膜用の絶縁膜を形成する。それから、プラズマ処理装置51の処理室51a内で、半導体基板1の主面のゲート絶縁膜用の絶縁膜をプラズマ窒化する。その後、プラズマ処理装置51から半導体基板1をフープ31内に移送し、フープ31をベイステーションBSに移動させてそこで待機させて半導体基板1を保管する。ベイステーションBSに待機している間、半導体基板1を保管しているフープ31内に、フープ31に設けられた第1の呼吸口から窒素ガスを供給し、フープ31に設けられた第2の呼吸口からフープ31内の窒素ガスを排出する。その後、フープ31を熱処理装置52に移動させて、半導体基板1を熱処理装置52の処理室内に搬入して熱処理する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】high−k膜を含むFETにおいて、低抵抗金属として高融点金属を用いた場合のイオン注入時のゲートにおけるドーパント突き抜けの問題と、低抵抗金属のグレインサイズの下地依存に起因したPMISトランジスタとNMISトランジスタとのゲート抵抗の差を解決する。

【解決手段】high−k膜4上に形成されるゲート電極を、仕事関数金属膜5とその上部の第一の低抵抗膜6、第二の低抵抗膜7で構成したMISトランジスタにおいて、仕事関数金属膜5上の、タングステンからなる第一の低抵抗膜6のグレインサイズを前記第一の低抵抗膜6上の第二の低抵抗膜7のグレインサイズより小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜上にポリシリコン膜3を形成する工程と、前記ポリシリコン膜の下層側に重元素の不純物イオン4をイオン注入する工程と、前記ポリシリコン膜の上層側に、前記重元素より質量の小さい軽元素の不純物イオン6をイオン注入する工程と、前記ポリシリコン膜を加工することにより、前記ゲート絶縁膜上にゲート電極3aを形成する工程と、前記半導体基板に不純物イオンをイオン注入し、熱処理を施すことによりソース・ドレイン領域の拡散層9を形成する工程と、を具備することを特徴とする。

(もっと読む)

1 - 20 / 127

[ Back to top ]