Fターム[4M104DD56]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 電極への不純物導入(析出時又は後) (529) | 限定領域への導入 (73)

Fターム[4M104DD56]に分類される特許

1 - 20 / 73

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ソース領域とドレイン領域間のリーク電流の発生が抑制された、LOCOS分離構造の半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板の上部の一部に互いに離間して形成された第1導電型のソース領域及びドレイン領域と、ソース領域とドレイン領域に挟まれた領域を含んで半導体基板上に配置されたゲート絶縁膜と、半導体基板上にゲート絶縁膜と連続して配置された、ゲート絶縁膜よりも膜厚の厚いLOCOS絶縁膜と、ゲート絶縁膜上及びゲート絶縁膜周囲のLOCOS絶縁膜上に渡り連続的に配置された多結晶シリコン膜からなるゲート電極とを備え、ゲート電極のチャネル幅方向の端部である周辺領域におけるゲート閾値電圧がゲート電極の中央領域におけるゲート閾値電圧よりも高い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、上記基板上に位置するバッファ層と、上記バッファ層上に位置する半導体層と、上記半導体層上に直接接触して位置するソース/ドレイン電極と、上記基板全面にわたって位置するゲート絶縁膜と、上記ゲート絶縁膜上に位置し、上記半導体層に対応するように位置するゲート電極と、を含み、上記ソース/ドレイン電極は1つまたは多数のホールを有する。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

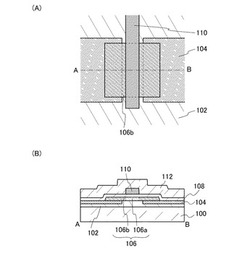

デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法

【課題】デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法を提供する。

【解決手段】デュアルゲート不純物ドーピング方法は、第1領域及び第2領域を有する半導体基板上のゲート導電膜に第1導電型の不純物イオンをドープする段階であって、ゲート導電膜の下部よりも上部における不純物ドーピング濃度がより高い濃度勾配でドープする段階と、第2領域のゲート導電膜をオープンさせるマスクを用いて第2領域のゲート導電膜に第2導電型の不純物イオンをドープする段階と、熱処理を行い、第1導電型及び第2導電型の不純物イオンを拡散させる段階と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の閾値を有し、ダストや不純物の局所的なばらつきによる歩留りの低下や、信頼性の低下を抑えることが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板(Sub.)に形成された第1導電型のMOSFETと第2導電型のMOSFETを有し、前記第1導電型のMOSFETは、第1導電型の不純物を含む第1のゲート電極15aと、第2導電型の不純物を含む第2のゲート電極15bとを備え、前記第2導電型のMOSFETは、第1導電型の不純物を含む第3のゲート電極15cと、第2導電型の不純物を含む第4のゲート電極15dとを備える。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

1 - 20 / 73

[ Back to top ]