Fターム[4M104DD88]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 限定部分の物質、物性の変換 (333)

Fターム[4M104DD88]の下位に属するFターム

電極表面のみ(電極層間界面を含む) (197)

Fターム[4M104DD88]に分類される特許

1 - 20 / 136

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法および表示装置

【課題】ソースおよびドレインと半導体層との間において良好なコンタクトを確保することが可能な有機薄膜トランジスタを提供する。

【解決手段】有機薄膜トランジスタは、有機材料よりなる半導体層上のソース電極およびドレイン電極に対向する第1および第2の領域のそれぞれに導電層を有し、この導電層が、還元反応によって導電性が変化する酸化物を含むものである。導電層が、半導体層とソース電極およびドレイン電極とのコンタクト層として機能すると共に、トップコンタクト構造では、製造プロセスにおいて半導体層上に、上記導電層を含むエッチングストッパ層を形成可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

電極およびそれを含む電子素子

【課題】優秀な導電性及び大きい仕事関数を有する電極及びそれを含んだ電子素子を提供する。

【解決手段】グラフェン含有層と、前記グラフェン含有層上に形成される仕事関数傾斜層と、を含み、前記仕事関数傾斜層は、前記グラフェン含有層と接触する第1面、及び前記第1面に対向する第2面を有する単一層であり、前記仕事関数傾斜層の仕事関数は、前記第1面から前記第2面に向かう方向に沿って漸進的に増大する電極。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

基板処理方法

【課題】被処理基板上のニッケル膜の凝集を抑制するための処理(例えばキャップ膜成膜)を行う際に,その凝集抑制処理後のみならず,その処理過程(例えば昇温工程)においても,ニッケル膜の凝集を抑制するニッケル膜の熱による凝集を抑制する。

【解決手段】処理室内に配置したウエハ300上にニッケル膜を成膜した後,処理室内にH2ガスを導入しながら水素雰囲気中でウエハを所定の温度(例えば300℃以上)まで加熱した上で(昇温工程),WF6ガスを導入してニッケル膜の表面を覆うキャップ膜として例えばタングステン膜を成膜する(W成膜工程)。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

Cu−Mn合金スパッタリングターゲット及び半導体配線

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜20wt%を含有し、Be,B,Mg,Al,Si,Ca,Ba,La,Ceの総計が500wtppm以下、残部がCu及び不可避的不純物であることを特徴とするCu−Mn合金スパッタリングターゲット。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板

【課題】パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板を提供する。

【解決手段】本発明によるパターン転写方法は、基板上にパターン物質を形成する第1段階と、パターン物質を固相状態に硬化させる第2段階と、硬化された固相状態のパターン物質にレーザー光を照射して、パターン物質をパターニングする第3段階と、パターニングされた固相状態のパターン物質と柔軟基板をお互いに突き合わせて加圧して、パターン物質から柔軟基板方向に、または柔軟基板からパターン物質方向にレーザー光を照射して、パターン物質と柔軟基板を突き合わせた部位で発生する柔軟基板の粘性力によって、パターン物質を柔軟基板に転写する第4段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

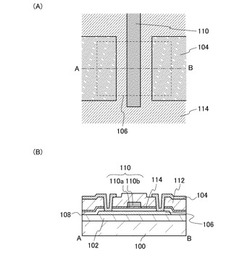

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体素子

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極への水素の拡散を防止することにより、ゲート絶縁膜の劣化を抑制し、信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置は、ポリシリコンを含むゲート電極と、ゲート電極の少なくとも上面を覆い、水素を貯蔵する機能を有する水素貯蔵層と、を備える。好ましくは、バリア層は、組成式SixNyOZの酸窒化膜を含有し、x:y:z=1:1:0.1〜0.7である。

(もっと読む)

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順に3価Cr濃化域、Cr欠乏部、金属Cr濃化域を形成して母材とオーミック接合で一体化しているダイオード用n型半導体担持電極材料。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

1 - 20 / 136

[ Back to top ]