Fターム[5F140CC16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | 塗布 (86)

Fターム[5F140CC16]に分類される特許

1 - 20 / 86

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】 ファセット起因による短チャネル効果を回避すること。

【解決手段】 半導体基板(1)に設けられたMISトランジスタ(4,5,13)からなる半導体デバイス(200)は、半導体基板(1)に設けられた素子分離領域(2)と、素子分離領域(2)によって区画された活性領域(3)と、活性領域(3)に設けられたMISトランジスタのチャネル領域よりも上方へ突出したMISトランジスタのソース/ドレイン領域(13)と、ソース/ドレイン領域(13)の下方に設けられた拡散層(12)と、を備える。ソース/ドレイン領域(13)の導電型に対する拡散層(12)の導電型が逆の極性となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

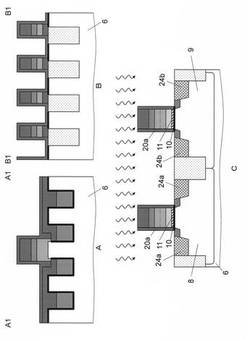

半導体装置およびその製造方法

【課題】SOGで平坦化した半導体装置であっても水分による閾値変動を抑制した半導体装置を提供する。

【解決手段】SOG平坦化後にSOGを除去したMOSトランジスタ領域を単層配線とし、SOGを残した非MOSトランジスタ領域を多層配線とすることで、SOGを介したMOSトランジスタへの水分の影響が無くなり、MOSトランジスタの閾値変動を抑制できる。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

1 - 20 / 86

[ Back to top ]