Fターム[5F083JA32]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | Si (497)

Fターム[5F083JA32]の下位に属するFターム

Fターム[5F083JA32]に分類される特許

1 - 20 / 96

メタルブリッジ型記憶装置

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

不揮発性記憶装置

【課題】抵抗値の変化によって高い信頼性で情報を記憶する積層型の不揮発性記録装置を実現する。

【解決手段】基板の主面に沿うように延在する第1配線と、前記第1配線の上方に設けられる積層体と、前記積層体の上方に形成される第2配線と、前記第1配線と前記第2配線との交点に設けられ、電流を前記基板の主面に対して垂直方向に流す選択素子と、前記積層体の側面に沿って設けられる第2絶縁膜と、前記第2絶縁膜に沿って設けられるチャネル層と、前記チャネル層に沿って設けられる接着層と、前記接着層に沿って設けられる抵抗変化材料層とを有し、前記第1配線および前記第2配線は、前記選択素子および前記チャネル層を介して電気的に接続されており、前記チャネル層と前記抵抗変化材料層との間の前記接着層を介した接触抵抗は低く、前記チャネル層の延在方向について前記接着層の抵抗が高く形成された不揮発性記録装置。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

キャパシタ構造の形成方法及びこれに用いられるシリコンエッチング液

【課題】半導体基板に凹凸形状をなすよう、アモルファスシリコン又は多結晶シリコンを的確かつ効率よく除去することができ、しかもそのエッチングが行われる条件下において長時間活性が維持されるシリコンエッチング液及びこれを用いたキャパシタ構造の形成方法を提供する。

【解決手段】アンモニアと、ヒドロキシルアミン化合物、塩基性有機化合物、及び金属含有塩基性化合物からなる群から選ばれる少なくとも1つの特定塩基性化合物とを組み合わせて含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜6に適用して、該多結晶シリコン膜またはアモルファスシリコン膜の少なくとも一部を除去することにより、キャパシタとなる凹凸形状を形成するキャパシタ構造10の形成方法。

(もっと読む)

半導体記憶装置

【課題】相変化メモリの構造の簡素化と低コスト化を実現する。

【解決手段】相変化材料からなる記録層18とn+型ポリシリコン膜15との間に、相変化材料を構成する元素の少なくとも一種とシリコンとを含有する中間層20を配置し、記録層18とn+型ポリシリコン膜15との接触抵抗を低減することにより、相変化メモリの構造の簡素化と低コスト化を実現する。例えば相変化材料がGe、SbおよびTeを含む場合、中間層20は、Si−Sb、Si−Te、Si−Geの少なくとも一種を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

半導体デバイス

【課題】軽量であり、かつ強固な信頼性を備えた半導体デバイスを提供する。

【解決手段】集積回路チップは、プラスチックの基板101と、基板101上に配されたポリマー誘電体103と、電極同士の間に形成された有機半導体材料112および受動層114の少なくとも1つのを含むアクティブデバイス104と、少なくとも1つのアクティブデバイス104に隣接する導電性ポリマー106および/または108とを備えている。

(もっと読む)

交差した導電あるいは半導電アクセス・ラインのクロスバー・アレイの実現方法

【課題】サブストレート上に交差した導電あるいは半導電アクセス・ラインのクロスバー・アレイを実現する。

【解決手段】絶縁体4上の、サブストレート2に平行な平面に、導電あるいは半導電材料で実現された相互に平行な複数の第一のライン11からなる第一のレベル20のライン11と、ライン11上に、第一のライン11に対して実質的に直角な、導電あるいは半導電材料で実現された相互に平行な複数の第二のライン17からなる第二のレベル21のライン17とで構成され、サブストレート2上に、実質的に長方形の第一のキャビティを形成するステージと第一および第二のキャビティが相互に直角に交差して、その結果としてキャビティが形成されるよう、第一のキャビティに重ねて実質的に長方形の第二のキャビティを形成するステージを含む。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】垂直壁の貫通ホールが形成でき、また、貫通ホールがテーパ状となった場合においても上部と下部とでしきい値電圧特性が均一化でき、安定して動作する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板11と、基板の主面11a上に設けられ、主面に対して垂直な第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体を前記第1方向に貫通する半導体ピラーSPと、電極膜のそれぞれと半導体ピラーとの交差部に設けられた記憶部(記憶層48)と、を備える不揮発性半導体記憶装置が提供される。電極膜は、アモルファスシリコン及びポリシリコンの少なくともいずれかを含む。基板からの距離が近い第1領域RG1の電極膜に含まれる添加物の濃度は、第1領域よりも基板からの距離が遠い第2領域RG2の電極膜に含まれる添加物の濃度とは異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

抵抗変化メモリ

【課題】p-i-nダイオードをその特性の劣化なしに薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第一方向に延びる第一導電線L2(i)と、第一方向に交差する第二方向に延びる第二導電線L3(j)と、第一導電線と第二導電線との間に直列接続されるメモリ素子17及び整流素子13,14,15から構成されるセルユニットCU2とを備える。メモリ素子の抵抗値は、メモリ素子に印加される電圧を制御することにより、少なくとも第一値と第二値との間で可逆変化させる。整流素子は、p型半導体層、n型半導体層及びこれらの間の真性半導体層から構成されるp-i-nダイオードである。p-i-nダイオードは、少なくともp型半導体層の真性半導体層側の端部及びn型半導体層の真性半導体層側の端部に拡散防止領域を有する。

(もっと読む)

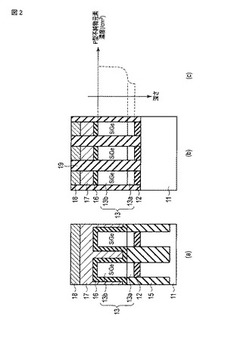

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】ドレイン電流の制御性を向上させつつ、メモリセルを縦方向に積層するとともに、メモリセルにフィン構造を用いた場合においても、制御ゲート電極および電荷蓄積層の加工の難易度を低下させる。

【解決手段】ブロック層13、電荷蓄積層14およびトンネル酸化膜15を順次介してフィン状の制御ゲート電極12aに埋め込まれたチャネル領域を有するボディ層17を設ける。

(もっと読む)

1 - 20 / 96

[ Back to top ]