Fターム[4M104EE08]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 多層電極の中層 (79)

Fターム[4M104EE08]に分類される特許

1 - 20 / 79

電界効果トランジスタ

シリコン膜の形成方法及び半導体装置の製造方法

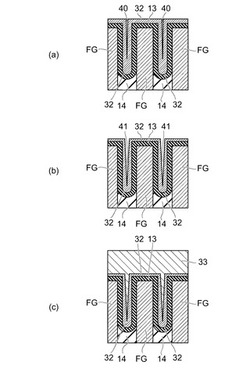

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

透明電極及び有機電子素子

【課題】導電性、透明性、フレキシブル性、導電性の面均一性に優れた透明電極と、該透明電極を用いた、寿命に優れた有機電子素子を提供する。

【解決手段】透明基板上に、少なくともパターン状に形成された金属粒子を含有する金属導電層と、少なくとも導電性ポリマーを含有するポリマー導電層を有し、かつ、該金属導電層が、該ポリマー導電層で被覆積層されている透明電極であって、該金属導電層表面の一部が絶縁層により被覆されている事を特徴とする透明電極及び有機電子素子。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 基板を処理容器内に搬入する工程と、処理容器内に処理ガスを供給し排気することで、基板上に所定膜厚の金属膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、金属膜を形成する途中もしくは金属膜を形成した後に処理容器内に酸素含有ガスおよび/または窒素含有ガスを熱またはプラズマで活性化して供給し排気することで、金属膜の底面もしくは表面を導電性の金属酸化層、導電性の金属窒化層または導電性の金属酸窒化層に改質する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

半導体装置

【課題】トレンチゲート構成のパワートランジスタを有する半導体装置のオン抵抗を低減する。

【解決手段】トレンチゲート構成のパワーMIS・FETQにおいて、ソース用の半導体領域3の上面の層間絶縁層12の端部(位置P1)と上記ソース用の半導体領域3の上面の上記ゲート電極9Eから遠い端部(溝16の外周の位置P2)との間の長さをaとし、上記層間絶縁層12と上記ソース用の半導体領域3の上面との重なり部の長さ(位置P1から溝5aの外周の位置P3までの長さ)をbとすると、0≦b≦aとする。これにより、ソースパッドSPとソース用の半導体領域3の上面との接触面積が増大する上、ソースパッドSPとチャネル形成用の半導体領域4との距離を短くすることができるので、トレンチゲート構成のパワーMIS・FETQのオン抵抗を下げることができる。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

半導体発光装置およびそれを備えた半導体パッケージ

【課題】活性層への注入電流の密度を均一化でき、その上、光取り出し効率を向上させることもできる半導体発光装置およびそれを備えた半導体パッケージを提供する。

【解決手段】半導体発光装置1は、サファイア基板11と、このサファイア基板11下に設けられたn型半導体層12と、このn型半導体層12下に設けられ、光を発する活性層13と、この活性層13下に設けられたp型半導体層14と、このp型半導体層14下に設けられ、上記光を透過する透明導電膜15と、この透明導電膜15下に設けられ、島状の第1開口16a複数有する層間絶縁膜16と、この層間絶縁膜16下に設けられて、第1開口16aに重なる島状の第2開口17aを複数有し、上記光を反射する反射膜17と、この反射膜17上に設けられると共に、一部が第1開口16aおよび第2開口17a内に入って透明導電膜15に接続された接続電極18とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

成膜装置及び基板処理装置

【課題】スループットを向上させつつ、反応ガスの消費を抑制する装置を提供すること。

【解決手段】真空容器10内に、多数の基板載置部5が搬送方向に一列に配列された基板載置部5の列を備えると共に、直線搬送路を有する周回搬送路に沿って前記基板載置部5の列を搬送する基板搬送機構4を設ける。また前記直線搬送路に沿って交互に配置され、基板載置部5の搬送路に対して夫々第1の反応ガス及び第2の反応ガスを供給するために、第1の反応ガスノズル61及び第2の反応ガスノズル62を設けると共に、前記第1の反応ガスが供給される領域と第2の反応ガスが供給される領域とを分離するために、第1の反応ガスノズル61及び第2の反応ガスノズル62の間に、基板載置部5の搬送路に対して分離ガスを供給する分離ガスノズル63を設ける。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写プロセスによりラインアンドスペースパターンを形成するときに、スペースの幅寸法を等しく形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層20上に第1の絶縁膜10、第2の絶縁膜12、第3の絶縁膜13を積層形成する工程と、ラインアンドスペースパターンのレジストをマスクとして絶縁膜12および13を異方性エッチングし、レジストを除去する工程と、絶縁膜12および13をスリミングし、ラインの断面形状をT字型の形状とするように加工する工程と、加工された絶縁膜12および13上に、これら絶縁膜12および13と異なる膜17を形成する工程と、異なる膜17を第2の絶縁膜13の上面および第1の絶縁膜10の上面が露出するまで異方性エッチングする工程と、絶縁膜12および13を除去後、第1の絶縁膜10をエッチングする工程とを備えたものである。

(もっと読む)

1 - 20 / 79

[ Back to top ]