Fターム[5F140BF38]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 不純物材料 (213)

Fターム[5F140BF38]に分類される特許

1 - 20 / 213

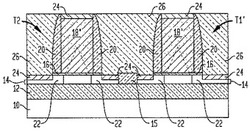

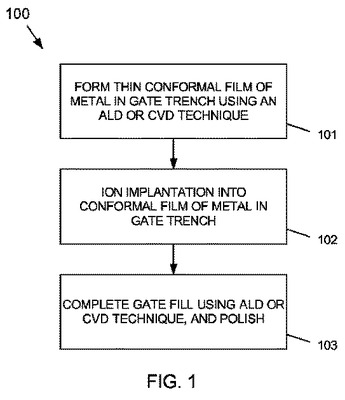

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

イオン注入を用いた圧縮金属ゲート応力の導入によるトライゲートMOSFETの駆動電流の増大化

半導体デバイスは、フィン及び金属ゲート膜を有する。フィンは半導体材料の表面に形成されている。金属ゲート膜は、フィン上に形成され、且つ金属ゲート内に圧縮応力を形成するために当該金属ゲート膜内に注入されたイオンを有する。典型的な一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<100>方向に沿っている。典型的な他の一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<110>方向に沿っている。フィンは、金属ゲート膜内の圧縮応力によって生成される面外圧縮を有する。  (もっと読む)

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

1 - 20 / 213

[ Back to top ]