Fターム[4M104DD29]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 膜形成 (298) | トンネル膜(絶縁物) (26)

Fターム[4M104DD29]に分類される特許

1 - 20 / 26

半導体装置の製造方法

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ液晶表示装置の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極、ゲート絶縁層、活性層及びソースドレイン電極を有した薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソースドレイン電極と該活性層のソースドレイン領域は重なり、該活性層と前記ソースドレイン電極間に電子の走行を許容する薄いSiNx又はSiOxNy層が設けられる。

(もっと読む)

ZnO系半導体素子

【課題】リーク電流をより小さくし、かつ、電気的特性を改善したショットキーバリア型のZnO系半導体素子を提供する。

【解決手段】基板1上にn型ZnO系半導体層2、酸化アルミニウム膜3が順に形成されている。また、酸化アルミニウム膜3上には、金属電極4、パッド電極5が形成される。金属電極4は、Pd層4a上にAu層4bが積層された多層膜構造を有している。金属電極4は、半透明電極として機能する。金属電極4上にはパッド電極5が形成されている。基板1の裏面には金属電極4に対向するように、裏面電極6が形成される。n型ZnO系半導体層2とPd層4aでショットキーバリア構造を構成している。

(もっと読む)

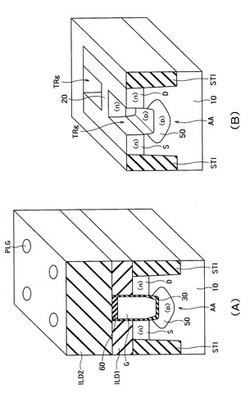

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

太陽電池セル及びその製造方法

【課題】アルミニウム電極における膨れや突起の発生を防止し、歩留まりに優れた太陽電池セル及びその製造方法を得ること。

【解決手段】p型多結晶Si基板1と、p型多結晶Si基板1の受光面に形成されたn型拡散層2と、n型拡散層2上に設けられた表面側電極7と、p型多結晶Si基板1の受光面とは反対側の面の表層に設けられたアルミニウム電極5及び銀電極16を有する太陽電池セルであって、アルミニウム電極5及び銀電極16とp型多結晶Si基板1との間にSi酸化膜4を介在させ、熱処理を施した。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

表示装置及び表示装置製造方法

【課題】表示装置の薄膜トランジスタ基板において、窒化ケイ素膜上への銅の微細配線を、より簡易に行う。

【解決手段】微細配線がされたTFT基板は、無アルカリガラスからなるガラス基板101と、インジウム錫酸化物からなる透明導電膜102と、アルミニウムを4原子%含有し銅を主成分とする合金からなる第一の導電層103及び109と、99.99%純度の純銅からなる銅配線である第二の導電層104及び110と、窒化ケイ素からなるゲート絶縁膜106と、非晶質ケイ素からなる半導体層107と、n+型非晶質ケイ素からなるコンタクト層108と、透明導電膜102と第一の導電層103との界面の金属酸化物層105と、を備える。

(もっと読む)

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

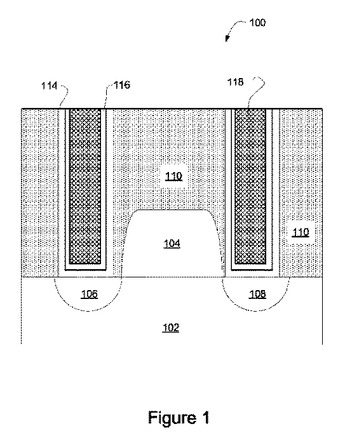

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

バリア膜とドレイン電極膜およびソース電極膜が高い密着強度を有する薄膜トランジスター

【課題】バリア膜とドレイン電極膜およびソース電極膜が高い密着強度を有する薄膜トランジスターを提供する。

【解決手段】上記酸化ケイ素膜のバリア膜と、上記純銅膜のドレイン電極膜およびソース電極膜の間に、水素プラズマ処理後の厚さ方向断面組織が、(a)上記純銅膜のドレイン電極膜およびソース電極膜側に形成された純銅化帯域と、(b)上記酸化ケイ素膜のバリア膜との界面部に形成され、構成成分がCuとCaと酸素とSiからなる成分凝集帯域、の2帯域で構成され、上記成分凝集帯域の厚さ方向に形成されたCaおよび酸素の含有ピークの最高含有量が、それぞれCa:5〜20原子%、酸素:30〜50原子%、であり、かつ、10〜100nmの目標膜厚を有する密着強化膜を介在させる。

(もっと読む)

半導体装置及びその製造方法

【課題】FEOLレベルから正負とも低電圧の範囲で拡散工程中のチャージアップから被保護素子を保護し、且つ、拡散工程完了後は被保護素子の駆動に必要な正負両極性の高電圧を被保護素子に印加することが可能な半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成され、被保護素子電極22を有する被保護素子21と、半導体基板11と電気的に接続された基板接続電極42を有する基板接続部41と、被保護素子電極22と基板接続電極42との間に形成されたヒューズ素子電極32を有するヒューズ素子部31とを備えている。ヒューズ素子電極32は、所定の電流を流すことにより切断可能に形成され、ヒューズ素子電極32が切断されていない状態において、被保護素子電極22、基板接続電極42及びヒューズ素子電極32は、一体に形成された導電膜15からなる。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

金属膜パターンの形成方法

【課題】電気めっきにより金属層を形成し、化学的機械研摩(CMP)法で研摩して金属膜パターンを形成する際に、金属膜パターンの組成分布、膜厚分布を小さくしてに電子デバイスの高性能化に対応し、かつ、めっき液、めっき装置への負荷を小さくして生産性を高める金属膜パターンの形成方法を提供する。

【解決手段】めっきする被めっき体10となる基板の表面に形成される金属膜パターン20Bを形成するために、基板表面をめっきするめっき工程と、そのめっき工程の後に、めっきにより形成された金属層20Aの膜厚を薄く平坦化するために研摩する研摩工程とを有する金属膜パターンの形成方法であって、めっき工程でめっきする部分に形成される金属層20Aが、被めっき体10表面全体に対してできるだけ小さくする。

(もっと読む)

1 - 20 / 26

[ Back to top ]