Fターム[5F140BF35]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 絶縁層を埋込んだもの (43)

Fターム[5F140BF35]に分類される特許

1 - 20 / 43

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】キャップ膜としてのランタン酸化膜の膜厚の増加を抑えつつ、閾値電圧の低減化を図れる、窒化チタン膜を含むメタルゲート電極/Hfを含有するゲート絶縁膜のゲートスタック構造を有するMOSFETを備えた半導体装置を適用すること。

【解決手段】P型半導体領域105を含む半導体基板101と、P型半導体領域101に形成されたNチャネルMOSFETとを具備してなり、前記NチャネルMOSトランジスタは、半導体基板101上に形成され、ハフニウムを含有するゲート絶縁膜108と、ゲート絶縁膜109上に形成され、膜厚が所定値以下のランタン酸化膜109と、ランタン酸化膜109上に形成され、N/Ti原子数比が1未満の窒化チタン膜110を含むゲート電極とを具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

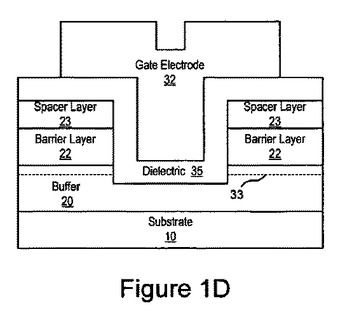

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作を安定化できる。

【解決手段】本発明の例に関わる半導体は、半導体基板1と、半導体基板1内に設けられる2つの拡散層7と、2つの拡散層7間のチャネル領域上に設けられるゲート絶縁膜2と、ゲート絶縁膜2上に設けられる複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが積層された積層体6と積層体6上に設けられるシリサイド層4Bとからなるゲート電極10と、を具備し、積層体6のうち、シリサイド層4Bとは異なる構成の導電膜3Aが、ゲート絶縁膜2と接触することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コストを低減した半導体装置を提供する。

【解決手段】半導体基板100表面部にチャネル領域101を挟むように形成された拡散層102と、チャネル領域101上に形成されたゲート絶縁膜103を有し、N型MOSFETのゲート電極104は第1のニッケルシリサイド層104a及び第1のニッケルシリサイド層104a上に形成され第1のニッケルシリサイド層104aよりニッケル含有率が高い第2のニッケルシリサイド層104bからなり、P型MOSFETのゲート電極104は第2のニッケルシリサイド層104bよりニッケル含有率が高い第3のニッケルシリサイド層からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域にSOG(spin on glass)膜を用いる構成で、LDD(lightly doped drain)構造を採用するトランジスタを形成する場合に、活性領域に転位が形成されて接合リーク特性が悪化するのを抑制することができる構成の半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1にトレンチ4を形成してSOG膜6を埋め込む構成で、LDD構造形成のための高濃度不純物領域1bを形成するためのイオン注入をしてから、SOG膜6をそれよりも深くなるように落とし込む。その後、熱処理を行なって注入したイオンを活性化する。SOG膜6による引張応力がイオン注入した活性領域2に作用して転位が発生するのを抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型トランジスタとPNゲートで構成されるプレーナ型トランジスタとが共存する半導体装置において、溝型トランジスタの溝ゲートの空乏化現象によるオン電流の低下を抑制し、溝型トランジスタと異なる導電型のP又はNゲートで構成されるプレーナ型トランジスタの閾値電圧のバラツキ増加を防止する。

【解決手段】溝型トランジスタのゲート電極であるポリシリコン膜中に高濃度不純物拡散材料9が埋設された構造を有する。

(もっと読む)

半導体装置の製造方法

【課題】MOS構造の半導体装置において、ゲート電極をイオン注入のチャネリングに対して強い構造とする。

【解決手段】半導体基板上でゲート絶縁膜の上に半導体材料を堆積してゲート電極を形成する。このゲート電極の表面または内部に非晶質層を形成する。その後、ゲートサイドウォールを形成し、ゲート電極およびサイドウォールをマスクとして半導体基板に不純物をイオン注入し、ソース/ドレインを形成する。非晶質層としては、窒素を1×1020〜1×1022/cm3個含む層を形成する。これを、熱処理に対する不純物析出抑制層とし、イオン注入に対するチャネリング防止層とする。

(もっと読む)

1 - 20 / 43

[ Back to top ]