Fターム[4M106AD01]の内容

半導体等の試験・測定 (39,904) | パッド(電極) (883) | 配列、配置 (168)

Fターム[4M106AD01]の下位に属するFターム

スクライブ部 (84)

Fターム[4M106AD01]に分類される特許

1 - 20 / 84

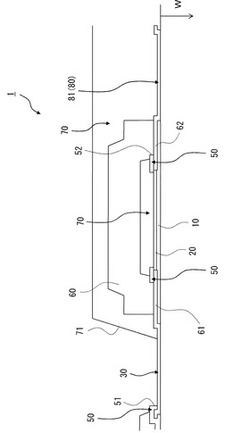

半導体チップ及びその製造方法、並びに半導体パッケージ

【課題】再配線形成前のウエハテストを適切に実施する。

【解決手段】半導体チップ1は、周辺電極パッド30内又はV/G配線20において周辺電極パッド30に相対的に近い位置にある第1の再配線接続部61と、V/G配線20において周辺電極パッド30から相対的に遠い位置にあり、再配線60の形成前における電位が第1の再配線接続部61よりも小さい第2の再配線接続部62とが、再配線60により接続されたものである。半導体チップ1は、第2の再配線接続部62、V/G配線20上の第2の再配線接続部62の近傍で再配線60の形成前における電位が第1の再配線接続部61よりも小さい部分、又は、V/G配線20から第2の再配線接続部62の近傍に引き出され、再配線60の形成前における電位が第1の再配線接続部61よりも小さい導電部に、ウエハテスト用の検査部80を備えている。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置

【課題】検査時におけるゲート電極パッドへのストレスを低減し得る半導体装置を提供する。

【解決手段】一実施形態に係る半導体装置は、MOSFET構造を有する複数の単位セルを含む半導体装置であって、各単位セルのMOSFET構造が有するゲート電極に電気的に接続されるゲート電極配線24と、ゲート電極配線に電気的に接続されており各ゲート電極を外部接続するためのゲート電極パッド30と、ゲート電極配線に電気的に接続されており検査用プローブが接触されるプローブ用電極パッド58とを備える。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

TEGPADを有する半導体装置及びそのTEGPAD配列方法

【課題】複数のTEG PADを有する半導体装置であって、カンチレバータイプのプローブカードを使用して同時に複数のTEG PADの測定を行う場合であっても、プローブのPADからの踏外しが生じにくい半導体装置を提供すること。また、このような半導体装置において、プローブのPADからの踏外しが生じにくいTEG PADの配列方法を提供すること。

【解決手段】複数本の探針を同時に接触させて測定を行う複数のTEG PADを配列した半導体装置であって、各TEG PADに投下される探針の投下位置と最終的に停止して接触する接触位置を対角として規定される長方形の領域内に、各TEG PADの中心位置を配置したことを特徴とする半導体装置及びそのTEG PAD配列方法。

(もっと読む)

マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器

【課題】電子部品の貫通電極において、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器を提供する。

【解決手段】電子部品の製造方法は、マザー基板に区画形成された電子部品の製造方法であって、基板の第1面における複数の区画領域に回路を形成する回路形成工程と、区画領域にて、第1面と第1面の反対面である第2面とを電気的に接続する貫通電極を形成する貫通電極形成工程と、互いに異なる区画領域に位置する貫通電極を第1面にて連結配線で電気的に接続する連結配線形成工程と、第2面にて、連結配線形成工程で電気的に接続された複数の貫通電極に検査プローブを電気的に接続させることによって、貫通電極の機能を検査する機能検査工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、薄いウェハでも破損させることなく、高温でもウェハの良否判定が可能な半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の半導体装置の製造方法は、(a)ウェハ13の第1主面と第2主面上に電極を有する半導体素子をウェハ13に形成する工程と、(b)工程(a)の後に、ウェハ13の第2主面と金属製の支持部材15の第1主面を接合部材14により接合する工程と、(c)工程(b)の後に、ウェハ13の第1主面上の電極と支持部材15の第2主面上に電圧を印加してウェハテストを行う工程とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

半導体装置

【課題】外部ループバックテストが容易な半導体装置を提供する。

【解決手段】主面に形成された格子状のダイシングライン14、15と、ダイシングライン14、15で囲まれた矩形状格子に形成され、信号出力パッド24有する送信回路22と、信号入力パッド25を有する受信回路23と、送信回路22および受信回路23に入出力されるデータを処理する内部回路21とを有する複数の集積回路12と、ダイシングライン14、15上に形成され、信号出力パッド24と信号入力パッド25間を電気的に接続する信号配線26とを具備する。

(もっと読む)

半導体ウェハ、および半導体装置、および当該半導体装置の製造方法

【課題】半導体チップを小型化することができる半導体ウェハを提供する。

【解決手段】半導体基板21における複数のチップ形成領域23にそれぞれ半導体素子24が形成され、一面上に層間絶縁膜50〜80が配置されていると共に、層間絶縁膜50〜80上に検査用パッド41aおよび信号用パッド41bが配置されている半導体ウェハにおいて、検査用パッド41aおよび信号用パッド41bのうち信号用パッド41bを、半導体素子24と対向する位置に備えると共に、層間絶縁膜50〜80の内部に形成されたビア52c〜82cを介して半導体素子24と電気的に接続する。そして、層間絶縁膜50〜80内の信号用パッド41bと半導体素子24との間に位置する部分に検査用配線61cを備え、検査用パッド41aと信号用パッド41bとを検査用配線61cを介して電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

高周波回路チップとこのチップを有する高周波回路装置並びにその製造方法

【課題】MMICの特性測定において,DCバイアス印加時の発振を抑制する。

【解決手段】この発明に係る高周波回路チップのMMIC60は、GaAs基板12上に所定の間隔をおいて並行して配設されたDCバイアス線路62が、その端部に互いに間隔をおいて隣接したDCパッド64を備えたもので、DCバイアス線路62の端部のDCパッド64に個別にDCバイアスを印加することができ、高周波信号の影響を少ない状態でチップの電気的特性を測定することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】接続部材が接続されるボンディングパッドを一面に有する半導体基板を備えた半導体装置において、接続部材の接続によるボンディングパッド下のダメージを検出する場合に、適切にパッド数の増加を抑制する。

【解決手段】半導体基板1の内部にてボンディングパッド11〜13の直下部位には、当該半導体装置の特性を検査するための検査用配線31〜33が設けられており、検査用配線31〜33の一端側は、半導体基板1の一面に設けられた検査用パッド20に導通し、検査用配線31〜33の他端側はボンディングパッド11〜13に導通している。

(もっと読む)

半導体装置

【課題】半導体チップを切り出す際に生じるばりによる半導体装置の歩留まりの低下及び信頼性の低下を防止し且つ半導体チップの取り数を向上させることができるようにする。

【解決手段】上面に複数のボンディングパッド14と複数の検査用パッドのパッド断片19とが形成された平面方形状の半導体チップにおいて、複数のパッド断片19は半導体チップの4辺のうちの対向する2辺に沿って形成されている。複数のボンディングパッド14は異なる2辺に沿って形成されている。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

半導体装置、半導体装置のレイアウト方法、及びプログラム

【課題】等ピッチに並んだ特性評価素子の境界の視認性が向上し、作業ミスの防止や、マニュアルプロービングによる測定において素子の位置の判断や、配置座標を用いた自動プロービングでのプロービングについて、正確に、かつ手間や時間を掛けない方法を提供する。

【解決手段】1つのスクライブTEGはMOSFETであれば評価素子3と4個の電極端子4a、4b、4c、4d及び評価素子と電極端子を電気的に接続する配線5により構成されている。抵抗体であれば評価素子と2個の電極端子及び評価素子3と電極端子を電気的に接続する配線5により構成されている。電極端子は異なる大きさで、等ピッチに並んでいる。スクライブ領域2には評価素子と電極端子及びスクライブTEGの評価素子と電極端子を接続する配線が存在する領域を避けるようにして配線層毎に配線ダミーが配置されている。

(もっと読む)

半導体ウェハおよび半導体ウェハにおける電圧供給方法

【課題】半導体チップを互いに接続する共通配線を備えた半導体ウェハの製造コストが増大するという課題を解決する半導体ウェハおよび半導体ウェハにおける電圧供給方法を提供する。

【解決手段】半導体基板101と、半導体基板101上に規則的に配置された複数の半導体チップ102と、半導体チップ102を互いに接続する共通配線103と、共通配線103に接続された共用電極パッド104、とを有し、共用電極パッド104は、複数の半導体チップ102を内包する露光照射領域と同一の規則性をもって配置され、かつ、露光照射領域に含まれる半導体チップ102を囲む外縁の内部に配置されている。

(もっと読む)

半導体装置及び半導体チップ

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

半導体装置形成用基板および半導体装置の製造方法

【課題】シェアテストを行う半導体装置形成用基板から得られる半導体装置の数量が減少するのを防止する。

【解決手段】半導体装置テスト用領域11aの周辺部には、半導体装置形成領域11内に形成される外部接続用電極21と同一プロセスで同一の外形サイズおよび断面積の外部接続用電極21が形成される。半導体装置テスト用領域11aは、有効半導体ウエハ領域1aの周縁部に数箇所設けられ、それぞれ、その一部が有効半導体ウエハ領域1aの外部に食み出すように形成される。このため、製品となる半導体装置形成領域の数量が減少するのを防止することができる。

(もっと読む)

半導体デバイス

【課題】データ入出力パッドとテストパッド間の経路や当該経路途中の回路の不良を検出することを可能とする方法を提供する。

【解決手段】半導体装置のテストのためのテストパッド(第2パッド22)と内部回路23との接続経路に、データ入出力のためのマイクロバンプパッド(第1パッド21)が配置されている。このため、前記第2パッド22を用いたテスト時に、前記内部回路23までの全経路の段線不良、回路不良が検出できる。

(もっと読む)

1 - 20 / 84

[ Back to top ]