Fターム[4M106AD10]の内容

半導体等の試験・測定 (39,904) | パッド(電極) (883) | 形成方法 (78)

Fターム[4M106AD10]に分類される特許

1 - 20 / 78

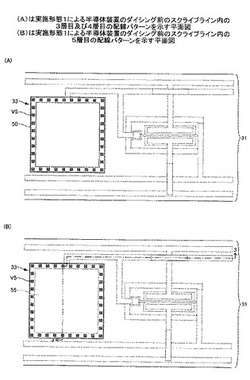

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

電気特性取得評価方法

【課題】電気特性取得評価方法に関し、試料側にもプローブ側にも問題を発生させることなく安定な電気特性取得評価を行う。

【解決手段】積層体の表面側電極に対するコンタクトホール21を露出する工程と、前記露出したコンタクトホール21に導電性物質を埋め込んで凸状構造22を形成する工程と、前記凸状構造22を含む領域にカンチレバーを間欠接触測定方式で接触させて前記凸状構造22の位置を認識する工程と、前記凸状構造22の中心軸の方向に前記カンチレバーを押しつけて電気特性を取得する工程とを設ける。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

チップパッケージ及びその形成方法

【課題】 チップパッケージの信頼性及び構造安定性を提供する。

【解決手段】 第1表面と第2表面を有する基板、前記基板の前記第1表面上に位置された導電パッド構造、前記基板の前記第1表面と前記導電パッド構造上に位置され、前記導電パッド構造の一部を露出する開口を有する誘電体層、及び前記誘電体層上に位置され、前記開口内に充填されるキャップ層を含むチップパッケージ。

(もっと読む)

マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器

【課題】電子部品の貫通電極において、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器を提供する。

【解決手段】電子部品の製造方法は、マザー基板に区画形成された電子部品の製造方法であって、基板の第1面における複数の区画領域に回路を形成する回路形成工程と、区画領域にて、第1面と第1面の反対面である第2面とを電気的に接続する貫通電極を形成する貫通電極形成工程と、互いに異なる区画領域に位置する貫通電極を第1面にて連結配線で電気的に接続する連結配線形成工程と、第2面にて、連結配線形成工程で電気的に接続された複数の貫通電極に検査プローブを電気的に接続させることによって、貫通電極の機能を検査する機能検査工程と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、薄いウェハでも破損させることなく、高温でもウェハの良否判定が可能な半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の半導体装置の製造方法は、(a)ウェハ13の第1主面と第2主面上に電極を有する半導体素子をウェハ13に形成する工程と、(b)工程(a)の後に、ウェハ13の第2主面と金属製の支持部材15の第1主面を接合部材14により接合する工程と、(c)工程(b)の後に、ウェハ13の第1主面上の電極と支持部材15の第2主面上に電圧を印加してウェハテストを行う工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】プローブ針の先端を研磨する時間を短縮することと接触抵抗を低く安定させること。

【解決手段】半導体基板上に形成された電子回路と、前記半導体基板上に形成され、前記電子回路と電気的に接続し、金属膜34と前記金属膜より硬い材料の層36とを備え、上視した場合前記層と前記金属膜とが配置された第1領域40と、前記金属膜が配置され前記層が形成されない第2領域42とを備えるパッド16と、を具備する半導体装置。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】1つの実施形態は、例えば、検査工程における検査用パッドへのコンタクトを容易化することに適した半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】1つの実施形態によれば、半導体装置は、表面に垂直な方向から見た場合にチップエリアを内側に含む半導体基板と、前記チップエリアを保護するように、前記表面上における前記チップエリアの周囲に配されたエッジシールと、前記表面上における縁部に配された複数のパッド片と、前記表面上における前記チップエリアに対して第1の方向の少なくとも片側と第2の方向の少なくとも片側とのそれぞれにおいて、前記パッド片における前記エッジシールの側の縁部を覆う絶縁膜パターンとを備える。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査に用いるプローブの耐久性を向上できる半導体装置を提供する。

【解決手段】ウエハーのスクライブ線150上に配置された第1チェック素子1を具備する。第1チェック素子1は、第1配線絶縁膜5と、第1配線絶縁膜5の第1開口部に配置された第1チェック素子パッド10とを備える。第1チェック素子パッド10は、導電性の第1パッドメタル部12と、矩形の平面形状を有する絶縁性の第1ダミー部13とを含む。第1ダミー部13の平面形状は、スクライブ線150の長手方向と垂直な2つの第1長辺と、第1チェック素子パッド10の外周部近傍に配置される2つの第1短辺とを含む。

(もっと読む)

DLTS測定用電極及びその製造方法

【課題】測定時において疑似ピークが現れないDLTS測定用電極を提供する。

【解決手段】シリコン基板上に設けられたアンチモンからなるショットキー電極12aと、シリコン基板10の表面10aとショットキー電極12aとの間に設けられたチタンからなる密着膜12bとを備える。本発明によれば、ショットキー電極の材料としてアンチモンを用いていることから、DLTS測定において疑似ピークがほとんど現れず、しかも、測定時におけるリーク電流を抑制することが可能となる。このため、シリコンウェーハに含まれている重金属の種類や濃度を正確且つ高感度に評価することが可能となる。

(もっと読む)

半導体装置

【課題】針傷を防止し、有効チップ数の減少を抑える半導体装置を提供すること。

【解決手段】対象チップ2−1は、ウェハ1に設けられている。隣接チップ2−2は、ウェハ1に設けられ、対象チップ2−1に隣接する。ボンディングパッド3は、対象チップ2−1の表面に設けられている。スクライブ領域4は、ウェハ1の対象チップ2−1と隣接チップ2−2との間に設けられ、ウェハ1の検査後にダイシングされる。貫通ビア5は、対象チップ2−1又は隣接チップ2−2に設けられている。表面配線6は、ボンディングパッド3からスクライブ領域4を介して対象チップ2−1又は隣接チップ2−2の表面の貫通ビア5に接続されている。検査用パッド7は、対象チップ2−1又は隣接チップ2−2の裏面に設けられている。裏面配線8は、対象チップ2−1又は隣接チップ2−2の裏面の貫通ビア5から検査用パッド7に接続されている。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

半導体装置

【課題】不導体被膜が、バンプ形成用領域に形成されることを防止する。

【解決手段】半導体装置は、半導体チップ1の上に形成された第1の電極パッド2aと、半導体チップ1の上に形成された第2の電極パッド2bと、半導体チップ1の上に形成され、第1の電極パッド2aの上面を露出する第1の開口部4a、及び第2の電極パッド2bの上面を露出する第2の開口部4bを有する絶縁膜4と、第1の電極パッド2aの上に形成された第1のUBM6aと、第2の電極パッド2bの上に形成された第2のUBM6bと、第1のUBM6aの上に形成された不導体被膜7と、第2のUBM6bの上に形成されたバンプ8とを有している。絶縁膜4における第1の電極パッド2aと第2の電極パッド2bとの間に形成された部分には、第1の溝5Xが形成され、第1の電極パッド側に位置する第1の溝5Xにより段差部5が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】プローブとパッドとを低接触抵抗で相互に電気的に接続させ、安定した特性検査を行うことができる方法の提供。

【解決手段】半導体装置は、電気的特性の検査を行う検査装置のプローブ8が接触されるパッド9を備え、パッド9の少なくとも表層部には、凹部21の内径がプローブ8の先端部8aよりも小径であり、凸部22の頂部が平坦である凹凸形状が形成されている。この構造により、パッド9上でオーバードライブされるプローブ8の先端部8aとパッド9の表面との摩擦を大きくすることができる。オーバードライブの際に、パッド9の表面に元々生成されている絶縁物をプローブ8の先端部8aで掻き取るようにして十分に剥がすことができる。こうすることで、プローブ8とパッド9とを低接触抵抗で相互に電気的に接続させ、安定した特性検査を行うことができる。

(もっと読む)

半導体装置

【課題】電極パッドの異常を容易に発見することが可能である。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板の第1領域における第1表面から前記第1表面に対向する第2表面まで空けられた第1貫通孔80内に形成された第1貫通電極25と、前記半導体基板の前記第1表面において、前記第1貫通電極に接して形成された第1電極パッド28と、前記第1電極パッドと離間して形成され、前記第1電極パッドと対向する第2電極パッド29と、前記半導体基板の前記第2表面上に形成され、前記第1貫通電極と電気的に接続された外部端子27と、前記半導体基板の前記第1表面において、前記半導体基板の前記第1領域と異なる第2領域における前記第1表面から前記第2表面まで空けられた第2貫通孔80上に形成され、電気的に浮遊した第3電極パッド28と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】電極を形成後において、半導体装置のテストを安定的に実施することができるとともに信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板11上に第一のパッド部12と、第二のパッド部13とを形成する工程と、第二のパッド部13上に第一の絶縁膜15を形成するとともに、第一のパッド部12上には第一の絶縁膜15を設けない工程と、第一のパッド部12上および第二のパッド部13上に金属膜16を形成する工程と、第一のパッド部12上に、金属膜16を介して電極17を形成する工程と、第二のパッド部13上の金属膜16を選択的に除去する工程と、第二のパッド部13上の第一の絶縁膜15を除去する工程とを含む。

(もっと読む)

1 - 20 / 78

[ Back to top ]