Fターム[4M106DJ23]の内容

半導体等の試験・測定 (39,904) | 装置の共通部 (6,103) | 表示 (351)

Fターム[4M106DJ23]の下位に属するFターム

CRT (16)

Fターム[4M106DJ23]に分類される特許

1 - 20 / 335

表面検査装置及び表面検査方法

外観検査装置

半導体パターン検査装置

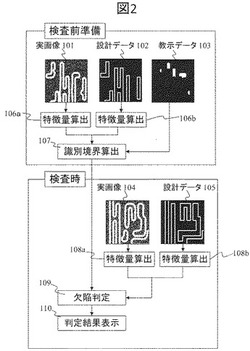

【課題】虚報を多発させることなく,システマティック欠陥を検出する半導体パターン検査装置を提供する。

【解決手段】検査に先立ち,前準備として,少数の実画像101と対応する設計データ102から,特徴量算出部でそれぞれのパターンの特徴を表す特徴量を算出し(106a,106b),これと,欠陥座標が指定された教示データ103とから,正常と欠陥を識別するルールである識別境界を識別境界算出部で算出する(107)。検査時には,検査対象の実画像104と,設計データ105から106a,106bと同様にして特徴量を算出し(108a,108b),これらに対し,検査前準備にて算出した識別境界107を適用することにより,欠陥判定部で欠陥判定109を行う。

(もっと読む)

欠陥観察方法及び欠陥観察装置

【課題】欠陥画像取得時間を短縮することが可能な欠陥観察方法および欠陥観察装置を提供する。

【解決手段】複数の画像取得条件から選択した任意の画像取得条件を用いて検査対象である試料の表面を撮像して欠陥画像を取得する画像取得工程と、前記画像取得工程にて取得した欠陥画像を処理して、該試料の表面上の欠陥位置を算出する欠陥位置算出工程と、前記欠陥位置算出工程にて算出した欠陥位置の確からしさである欠陥検出確度を求める欠陥検出確度算出工程と、前記欠陥検出確度算出工程にて求めた欠陥検出確度が予め定めた条件を満たすかどうかを判定する終了判定工程と、を備え、前記終了判定工程にて該条件を満たすと判断するまで、前記複数の画像取得条件から画像取得条件を選択し直し、前記画像取得工程と前記欠陥位置算出工程と前記欠陥検出確度算出工程と前記終了判定工程とを繰り返す。

(もっと読む)

レシピ生成装置、検査支援装置、検査システムならびに記録媒体。

【課題】設計レイアウトに記録された情報を、直接、解析して、所望の領域を抽出し、この抽出方法を用いて検査レシピを生成し、効率的な検査を実現する。

【解決手段】設計レイアウトデータの階層情報を解析して、その内部データであるセル一つ一つが設計レイアウトデータ内での参照回数を計算して、参照回数の多い順に並び替えて、対象を探索し、その上位セルを追跡することによって、メモリマットなどの所望の回路モジュールの領域抽出を容易にする。

(もっと読む)

半導体欠陥検査装置ならびにその方法

【課題】回路設計データを用いた半導体ウェーハ上の欠陥を自動的に検出し、欠陥発生原因の推定を行う半導体欠陥検査装置ならびにその方法を提供する。

【解決手段】回路設計データ1160から検査対象回路パターンと比較するために,欠陥発生要因毎に定められた形状変形項目について設計データに変形を加え,複数の形状を作成する(1192)。作成された形状群302と実パターンの比較により欠陥を検出する。また、それらの欠陥の発生原因を推定し,原因別に欠陥を分類する。

(もっと読む)

表面検査装置及び表面検査方法

【課題】検査速度の低下を伴うことなく、かつ装置容積に占める信号処理部の比率を増加させることなく、データメモリのオーバーフローを回避し、ウエハ全面の検査データを取得するが可能な表面検査装置を実現する。

【解決手段】後処理手段111のブロック化手段300は前処理手段からのデータを任意のデータ数で1ブロックとし1ブロックで1データを取り出す。ブロック化手段300は状態監視手段302の指示でブロック化数を変更する。閾値処理手段301は設定閾値に従いブロック化手段300からのデータに対し閾値を越えた場合にデータを取得しメモリ303へ送る。状態監視手段302はメモリ303の空容量を監視しメモリ303内の空き容量の減少を検知した場合ブロック化手段300に対し、メモリ303がオーバーフローしないように1ブロックのデータ数を増加させる。

(もっと読む)

半導体試験装置、半導体試験方法及びプログラム

【課題】ウェハに含まれる半導体集積回路の電気的特性の測定には、測定対象となる全ての半導体集積回路が専用の測定回路を備えている必要があるが、全ての半導体集積回路に対して専用の測定回路を配設すると、半導体集積回路の面積が増加してしまう問題がある。そのため、半導体集積回路の面積を増加させることなく、半導体集積回路の電気的特性の測定を可能とする半導体試験装置が望まれる。

【解決手段】半導体試験装置は、第1の半導体集積回路と、電気的特性を測定するための測定回路及び測定端子と、前記測定回路に近接する第2の半導体集積回路と、を含むウェハの特性の測定を行う測定部と、第2の半導体集積回路に対して実施するウェハテストから得られる第1の電気的特性と、測定端子から測定した第2の半導体集積回路についての第2の電気的特性と、の相関に基づいて第1の半導体集積回路について第2の電気的特性を推定する制御部と、を備えている。

(もっと読む)

半導体デバイスの欠陥検査方法およびそのシステム

【課題】

ステップ・アンド・リピート式の高解像度SEMを用いて予め定められた危険点を検査し、危険点での欠陥発生頻度を統計的かつ信頼性を持って推定する半導体デバイスの欠陥検査方法及びそのシステムを提供する。

【解決手段】

デザインデータ上で欠陥タイプ別に検査点を指定し、この指定された検査点の中から予め指定された数の検査点を欠陥タイプ別に選択し、この選択した欠陥タイプ別に予め指定された数の検査点を撮像してこの検査点における欠陥を検出し、欠陥タイプ別に撮像した検査点の数に対する検出した欠陥の数の比である欠陥比率とこの欠陥比率の信頼区間を算出し、この算出した欠陥タイプ別の欠陥比率の信頼区間と予め設定した基準値とを比較し、この基準値を超える欠陥発生比率をもつ欠陥タイプを求める半導体デバイスの欠陥検査方法及びそのシステムとした。

(もっと読む)

多結晶シリコンウェーハの評価方法

【課題】日常的な工程管理に利用可能な、多結晶シリコンウェーハの品質を簡便に評価する方法を提供すること。

【解決手段】評価対象の多結晶シリコンウェーハ表面を選択エッチングし、該表面において結晶欠陥を顕在化させること、結晶欠陥を顕在化させた多結晶シリコンウェーハ表面のマクロ画像を散乱画像として取得すること、および、取得したマクロ画像の輝度分布に基づき、前記多結晶シリコンウェーハにおける結晶欠陥分布を定量的に評価すること、を含む多結晶シリコンウェーハの評価方法。

(もっと読む)

欠陥分類方法及び欠陥分類システム

【課題】自動欠陥分類機能では、装置毎に適切な処理パラメータが異なるが同一の工程において複数の装置が運用される場合でも、それぞれの分類レシピにおける分類クラスに差が発生しないようにする。

【解決手段】同一の工程で異なる画像撮像装置から得られた画像から同種の欠陥画像を特定する対応欠陥特定部209、同一の工程で異なる画像撮像装置から得られた画像を変換し、比較可能な類似した画像に変換する画像変換部212、同一の工程の分類レシピについて、同一の分類クラスを定義し、特定された同種の欠陥画像をそれぞれの対応する分類レシピ内の分類クラスに登録するレシピ更新部211を備えた。

(もっと読む)

基板検査装置および基板検査方法

【課題】基板に形成された凹部の深度を、非破壊、非接触で検査できるとともに、高速に検査できるようにする技術を提供する。

【解決手段】基板検査装置100は、ポンプ光の照射に応じて、基板Wに向けてテラヘルツ波を照射する照射部12と、プローブ光の照射に応じて、基板Wを透過したテラヘルツ波の電場強度を検出する検出部13と、テラヘルツ波が検出部13に到達する時間と、検出部13における検出タイミングを遅延させる遅延部14とを備える。また、基板検査装置100は、基板Wの第1領域を透過した第1テラヘルツ波の時間波形を構築する時間波形構築部21と、基板Wの第2領域を透過した第2テラヘルツ波について、特定の検出タイミングで検出される電場強度と、前記時間波形とを比較することにより、第1テラヘルツ波と第2テラヘルツ波の位相差を取得する位相差取得部24とを備える。

(もっと読む)

半導体装置の製造方法及び洗浄装置

【課題】パターニング前工程にて半導体製造基板の歩留りへの影響を受けず、SEMレビューを可能とする半導体装置の製造方法及び洗浄装置を提供する。

【解決手段】製造装置30aにて所定の製造処理が施されたウェハWは、検査装置10にて欠陥が検査された後、評価装置20に搬送される。評価装置20では、検査装置10にて検出された欠陥がSEMレビューされる。そのSEMレビューされたウェハWは、洗浄装置40に搬送され、その表面に有機溶剤が塗布されて洗浄される。その洗浄後のウェハWは、製造装置30bに搬送され、次工程の製造処理が施される。

(もっと読む)

電子線応用装置

【課題】回路パターンを有する半導体装置等の検査において、陰影コントラストの強調された像を取得することを可能にし、浅い凹凸の微細な異物等を高感度に検出することを可能にする荷電粒子ビーム検査技術を提供する。

【解決手段】高分解能観察の為に電子光学系の対物レンズに電磁重畳型対物レンズ103を用い、その対物レンズを用いて電子ビームを細く絞り、対物レンズ内にアシスト電極106と左・右検出器110、111を設け、その電子ビームを試料104に照射することで発生する二次電子の速度成分を選別し、さらに方位角成分を選別して検出する。

(もっと読む)

表面欠陥検査装置及び方法

【課題】ウエーハ等の表面欠陥検査装置において、前方散乱光を高感度で検出し、正反射光をも同時に高感度検出可能とすることで、欠陥捕捉率の高い高効率の欠陥検査を実現。

【解決手段】前方散乱光検出手段20は、ベアウエーハ1の前方散乱光を受光する光学系であり、照明手段10よりベアウエーハ1に照射された検査光3による欠陥2からの散乱光を受光する検出レンズ21と全反射ミラー22とで構成され、その中央部(検査光入射平面と直行した方向)で分割した特徴を持つ。この全反射ミラー22で側方に分離された前方散乱光は光電変換素子23で検出され、中央の分割領域を直通する正反射光7は正反射光検出手段30で検出されるので、前方散乱光と正反射光とで互の影響を抑制しつつ同時に検出することできる。

(もっと読む)

プローブカードの熱的安定化方法及び検査装置

【課題】プローブカードに熱源を直に接触させて短時間でプローブカードを所定の温度に調整すると共に、熱的に安定したかを正確に判断することができるプローブカードの熱的安定化方法を提供する。

【解決手段】プローブカードの熱的安定化方法は、載置台に熱伝達用基板を載置し、載置台を介して熱伝達用基板の温度を調整する第1の工程と、載置台を上昇させて熱伝達用基板と複数のプローブを所定の目標荷重で接触させる第2の工程と、熱伝達用基板との間で熱を授受するプローブカードの熱的変化に即して変化する熱伝達用基板と複数のプローブとの接触荷重を検出する第3の工程と、プローブカードが熱的に安定するまで接触荷重が所定の目標荷重になるように昇降駆動機構を介して載置台を昇降制御する第4の工程と、を備えている。

(もっと読む)

欠陥検査装置及び欠陥検査方法

【課題】半導体装置の歩留りを効率的に、かつ高精度に算出する。

【解決手段】薄膜を一様に形成した半導体ウェハ2の画像データを取得し、品種ごとに形成された欠陥識別データ38と製品パターン39とを用いて、薄膜に形成された欠陥を抽出する。欠陥識別データ38は、半導体装置の電気特性に影響を与える欠陥サイズの情報であり、製品パターン38は、回路パターンが疎な領域をマスクしたパターンである。さらに、抽出した欠陥が存在するチップの数から歩留り率の予想値を算出し、その品種に必要とされる規定の歩留り数と比較して半導体ウェハ2の良否を判定する。

(もっと読む)

評価素子、半導体装置および半導体装置の製造方法

【課題】活性領域と素子分離絶縁膜との段差を精度よく評価する技術を提供する。

【解決手段】半導体基板10に形成されたトレンチに埋め込まれた素子分離絶縁膜18と、前記半導体基板10に形成され不純物を含む活性領域36と、前記活性領域36と前記素子分離絶縁膜18との間の段差を測定するための前記活性領域36の幅W1〜W7が異なる複数の段差測定部52a〜52gと、を具備する評価素子によって前記段差を測定し、この測定結果に基づき、ゲート寸法を調整する。

(もっと読む)

欠陥検査方法及びその装置

【課題】

電子顕微鏡で画像を撮像するとき,焦点を合わせるために動作させるZ座標の走査範囲を短くして,焦点を合わせる時間を短縮する。

【解決手段】

走査電子顕微鏡で試料上の複数の箇所のSEM画像を順次取得することを、最初の所定の数の箇所においては電子ビームの焦点位置を試料の表面の法線方向に所定の範囲走査して電子ビームの焦点を試料の表面に合わせてから試料を撮像し、最初の所定の数の箇所において試料の表面に合わせた電子ビームの焦点位置の情報を用いて試料の表面の曲面形状を推定し、最初の所定の数の箇所で撮像した後は、電子ビームの焦点を試料の表面に合わせるために電子ビームの焦点位置を法線方向へ走査する範囲を推定した曲面情報を用いて最初の所定の数の箇所において走査した所定の範囲よりも狭い範囲で走査して電子ビームの焦点を試料の表面に合わせて前記試料を撮像するようにした。

(もっと読む)

システマティック欠陥判定方法およびその装置

【課題】

欠陥密度の差の信頼性を高く維持した状態で、より少ない時間でステマティック欠陥判別を可能にする。

【解決手段】

半導体デバイスの特定レイヤの回路パターンをサンプリングし、このサンプリングされた回路パターンと特定レイヤ以外の1つ以上のレイヤの回路パターンとの重なり方をデザインデータを用いて判定し、その重なり方に応じて分類し、その比率を基準比率として算出し、この特定レイヤを他の検査装置で検査して検出された欠陥位置に対応するデザインデータ上のパターンと特定レイヤ以外のレイヤの欠陥の位置に対応する位置におけるパターンの重なり方を判定し、判定した重なり方を該重なり方に応じて分類し、この分類した比率を検査結果比率として算出し、この算出した基準比率と算出した検査結果比率とを比較し、基準比率と検査結果比率とを比較した結果に基づいてシステマティック欠陥を判定するようにした。

(もっと読む)

1 - 20 / 335

[ Back to top ]