Fターム[4M112CA34]の内容

圧力センサ (26,807) | 素子の構造 (8,535) | ビーム(梁)型、重錘型素子 (4,892) | 保護、絶縁層 (113)

Fターム[4M112CA34]に分類される特許

21 - 40 / 113

2軸加速度センサ

【課題】2方向の加速度を精度よく感知することができ、小型化及び製造コストの低減化を可能とする2軸加速度センサを提供することを目的とする。

【解決手段】本発明は、平板状の錘部、この錘部の側面を囲う枠部、上記錘部の側面と枠部の内面とを連結する1又は複数の梁部、及び上記梁部に付設される歪み感知手段を備える平板状の2軸加速度センサであって、上記梁部の厚さが幅より大きく、上記1又は複数の梁部が、厚さ方向と垂直な直交2方向の正負それぞれの加速度に対する撓みパターンの組合せが異なる少なくとも2つの変形領域を有し、上記歪み感知手段として、上記各変形領域の両端側かつその幅方向両側近傍に二対のピエゾ抵抗素子が配設されていることを特徴とする。

(もっと読む)

半導体加速度センサ

【課題】構造的制限を設けることなく、X、Y、Z軸の検出感度の差を小さくし、且つ、ドリフトが小さく、3軸間の信号出力の変動を低減する半導体加速度センサを提供すること。

【解決手段】本発明によると、半導体基板に、枠部と、錘部と、前記枠部と前記錘部との間に配置される可撓部と、前記可撓部に第1の方向に配置される複数のピエゾ抵抗素子と、前記第1の方向と直交する第2の方向に配置される複数のピエゾ抵抗素子と、前記複数のピエゾ抵抗素子をそれぞれ含む複数のブリッジ回路とを有し、前記ブリッジ回路に電圧を印加する高電位端及び低電位端のうちの何れか一方と、前記ブリッジ回路との間に第1の抵抗体を有する少なくとも1つの前記ブリッジ回路を備えることを特徴とする半導体加速度センサが提供される。

(もっと読む)

半導体装置の製造方法

【課題】 短時間で確実にデポ膜を除去することができる半導体装置の製造方法を提供する。

【解決手段】 錘部と、錘部を開口部を挟んで囲むように配置された外枠支持部と、錘部と支持部とを連結する梁部とを備える半導体装置の製造方法であって、支持基板をエッチングして錘部と支持部とを形成する基板加工工程と、基板加工工程のエッチングで生じたデポ膜に接する錘部及び支持部各々の開口部側の側壁を変質させる変質工程と、変質工程後、側壁の変質箇所をデポ膜と共に錘部及び支持部各々から除去するデポ膜除去工程と、を備える。

(もっと読む)

MEMSマイクロフォンと製造方法

本発明は、二重固体電極を有するMEMSマイクロフォンの改善された製造方法と、改善された性質を有するマイクロフォンを提供する。 (もっと読む)

センサデバイス及びその製造方法

【課題】センサ内部の配線パターンの設計や製造工程を変更せずに、配線パターンを容易に変更可能にするセンサデバイス及びその製造方法を提供する。

【解決手段】センサデバイスは、複数のピエゾ素子231,232と、複数の接続パッド261〜265と、ピエゾ素子231,232と電気的に接続された上層配線240、241と、上層配線240及び241に接続された下層配線251及び252と、下層配線251及び252に対して垂直方向に交差する上層配線242〜244と、上層配線242〜244の下層の下層配線253〜257があり、下層配線253〜257の他端部の上層には、絶縁層を介して接続パッド261〜265が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁分離領域に起因するMEMS素子の感度の制限が抑制される半導体装置及び半導体装置の製造方法を提供する。

【解決手段】上面に凹部100が形成された半導体基板10と、凹部100を囲むように半導体基板10上に配置された支持体70と、凹部100上方に配置された可動電極21を有し、可動電極21より離間した位置において支持体70に固定された梁型の可動部20と、可動電極21に対向して凹部100上方に配置され、支持体70に固定された梁型の固定電極30と、半導体からなる分離柱401とその分離柱401の側面に配置された分離絶縁膜402を有し、可動電極21及び固定電極30と支持体70間にそれぞれ配置され、可動電極21及び固定電極30と支持体70とを電気的に分離する絶縁分離領域40とを備える。

(もっと読む)

1軸加速度センサ

【課題】 少ない工程で製造できる1軸加速度センサを提供する。

【解決手段】 支持部(S)と、平行する二つの面に内周面が開口している凹部(50)が形成され前記凹部内に重心を有する錘部(M)と、一端が前記支持部と結合し他端が前記凹部の底面に結合している板ばね形の可撓部(F)と、前記可撓部の長手方向の両端近傍でかつ前記可撓部の短手方向の両端近傍に少なくとも2つずつ互いに前記可撓部の厚さ方向に離間して設けられる歪み検出素子(P1〜P4)と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】振動子と半導体基板間の短絡が防止され、且つ製造工程の増大を抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】上面に凹部100が形成され、凹部100の底面101に半導体層が露出した半導体基板10と、凹部100内に配置され、且つ側面及び下面に絶縁膜が配置された梁型の可動電極21を有し、可動電極21より離間した位置において半導体基板10に固定された振動子20と、可動電極21に対向して凹部100内に配置され、可動電極21と電気的に分離されて半導体基板10に固定された梁型の固定電極30とを備える。

(もっと読む)

加速度センサ

【課題】ウエハレベルパッケージを用いて、電極パッド近傍の信頼性を向上させることができる加速度センサを提供する。

【解決手段】加速度センサ100は、加速度検出素子と枠111に形成された電極パッド115(115a〜115d)とを接続するAl配線116とからなるセンサ部110と、枠111上に形成されたAl配線116と電極パッド115(115a〜115d)の一部に積層される保護膜117と、センサ部110を覆って、センサ部110を密閉空間に収容するキャップ部118と、保護膜117上に積層され、センサ部110とキャップ部118とを接合する接着層119とを有する。

(もっと読む)

加速度センサ

【課題】ウエハレベルパッケージを用いて、電極パッド近傍の信頼性を向上させることができる加速度センサを提供する。

【解決手段】加速度センサ100は、加速度検出素子と枠111に形成された電極パッド115とを接続するAl配線116とからなるセンサ部110と、センサ部110に実装されてセンサ部110を密閉空間に収容するキャップ部117と、センサ部110とキャップ部117とを接合する接着層118とを備え、電極パッド115は、センサ部110の密閉空間の方向に拡張された拡張部115Aを有し、キャップ部117は、拡張部115Aの端部と積層される接着層118によりセンサ部110と接合する。

(もっと読む)

MEMSセンサー、電子機器

【課題】基板と垂直なZ方向に変位する可動錘部の質量を増大させることができ、CMOSプロセスを用いて自在かつ容易に製造可能なMEMSセンサーを提供すること。

【解決手段】連結部130Aを介して支持部110に連結されてZ方向に移動する可動錘部120Aを有するMEMSセンサー100Aは、可動錘部が、複数の導電層と、複数の導電層間に配置された複数の層間絶縁層と、複数の層間絶縁層の各層に貫通形成された埋め込み溝パターンに充填され、層間絶縁膜よりも比重が大きいプラグと、を含む積層構造体を有し、各層に形成されたプラグは、層間絶縁層と平行な二次元平面の少なくとも一軸方向に沿って壁状に形成された壁部を含む。可動電極部140Aは積層構造体にて形成され、これと対向する固定電極部150Aとの間の対向面積が可動錘部のZ方向変位に応じて変化する。

(もっと読む)

MEMSセンサー、MEMSセンサーの製造方法、および電子機器

【課題】可動錘部の質量を効率的に増大させることができ、多層配線を使用するCMOSプロセスを用いて、自在かつ容易に製造することが可能なMEMSセンサー(例えば静電容量型加速度センサー)を提供すること。

【解決手段】連結部130Aを介して支持部110に連結され、周囲に第1,第2空隙部111,112が形成されてZ方向に移動する可動錘部120Aを有するMEMSセンサー100Aは、可動錘部120Aが、複数の導電層と、複数の導電層間に配置された層間絶縁層と、層間絶縁層に貫通形成された埋め込み溝パターンに充填され、層間絶縁膜よりも比重が大きいプラグと、を含む積層構造体を有する。プラグは、層間絶縁層と平行な二次元平面の少なくとも一軸方向に沿って壁状に形成された壁部を含む。複数の導電層の一つが可動電極面を有する可動電極部140Aとなり、これと対向する固定電極部150Aが設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】2枚の基板が一体化されたものに外力が加わっても、接合界面における密着力の低下を抑制することができる構造を備えた半導体装置およびその製造方法を提供する。

【解決手段】センサ部10とキャップ部20との積層体に、センサ部10とキャップ部20との界面40を貫く凹部41を設け、この凹部41内に封止部材として絶縁膜42および封止用外周金属層43を設ける。これによると、凹部41に配置された封止部材42、43が盾となるので、凹部41よりも内側の界面40に外力が直接伝わらない。したがって、センサ部10とキャップ部20との密着力の低下が抑制される。

(もっと読む)

MEMSセンサ及び製造方法

【課題】 特に、IC表面にセンサ部が形成された構造において、スティッキング防止構造を簡単に形成できるMEMSセンサ及びその製造方法を提供することを目的としている。

【解決手段】 IC11と、IC表面の凹凸に倣って形成された保護層13と、前記保護層13上に形成されたセンサ部14とを有する。前記センサ部14には、可動電極部14aを有するセンサ機能部19が設けられ、前記センサ機能部19は、空間22を介して、表面13aが凹凸面から成る前記保護層13と対向している。本発明では、IC表面の凹凸を利用し、その凹凸に倣って保護層13の表面13aを凹凸面で形成することで、可動電極部14aと保護層13との間の接触面積を小さくでき、簡単な構造で適切にスティッキングを防止できる。

(もっと読む)

MEMSセンサー、MEMSセンサーの製造方法、および電子機器

【課題】可動錘部の質量を効率的に増大させることができ、また、物理量を高精度で検出可能であり、また、多層配線を使用するCMOSプロセスを用いて、自在かつ容易に製造することが可能なMEMSセンサー(例えば静電容量型加速度センサー)を提供する。

【解決手段】弾性変形部130を介して固定枠部110に連結され、周囲に空洞部111,112が形成された可動錘部120を有するMEMSセンサー100Aにおいて、可動錘部120は、複数の導電層121A〜121Dと、複数の導電層間に配置された複数の層間絶縁層122A〜122Cと、複数の層間絶縁層の各層に貫通形成された所定の埋め込み溝パターンに充填され、層間絶縁膜よりも比重が大きいプラグ123A〜123Cと、を含む積層構造体を有し、各層に形成されたプラグは、一または複数の長手方向に沿って壁状に形成された壁部を含む。

(もっと読む)

加速度センサ及び加速度センサの製造方法

【課題】配線導体による起伏の影響を抑えつつ、小型化に対応した加速度センサおよび加速度センサの製造方法を提供する

【解決手段】固定部3と、加速度が加わったときに固定部3に対し変位する重り部1と、一端が固定部3に、他端が重り部1にそれぞれ連結され、重り部1の変位に伴って撓む梁部2と、を有するセンサ素子20と、センサ素子20が実装される平板状の第1の基板30と、第1の基板30が実装される基体40であって、内部または第1の基板30が実装される面40Sに配線導体41が配置されている基体40と、第1の基板30と基体40との間に介在され、第1の基板30を基体40に固定するための第1の接着材10と、を備えた構成とする。

(もっと読む)

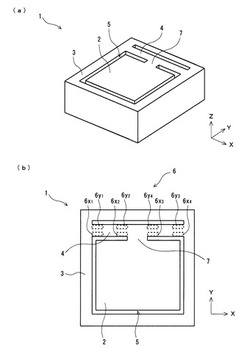

加速度センサ装置

【課題】耐衝撃性を向上させた加速度センサ装置を提供する。

【解決手段】固定部13と、固定部13に対し変位可能な重り部11と、一方端が固定部13に連結され、且つ他方端が重り部11に連結され、重り部11の変位に伴って撓む梁部12と、を有する加速度センサ素子20と、加速度センサ素子20が実装されるとともに、固定部13を囲繞する枠状部5を有する実装基体1と、固定部13の外側面17と実装基体1の枠状部5の内側面18との間に介在し、加速度センサ素子20と実装基体1とを接合する第1の接着材8を有する。

(もっと読む)

加速度センサー、電子機器

【課題】耐衝撃性に優れた加速度センサーを得ること。

【解決手段】固定電極41と可動電極21との間の距離が変化するX軸方向の加速度印加時において、固定電極41と可動電極21との間隙70に存在する気体の流れは、対向面に形成された一方向に向かって延びる凸部43によって一方向への流れが発生する。この気体の流れによるスクイーズフィルムダンピングにより、大きな減衰定数cを得ることができる。したがって、可動部20と支持体10との間隔を狭くすることなく、固定電極41と可動電極21との間隙70の構造によって減衰定数cの調節を可能にでき、可動部20と支持体10との衝突破壊が低減した耐衝撃性の優れた加速度センサー100を得ることができる。

(もっと読む)

ウェハレベルパッケージ構造体

【課題】アルミ溶断による陽極接合の不良発生を抑制するウェハレベルパッケージ構造体を提供する。

【解決手段】半導体ウェハ11と、この半導体ウェハ11の一表面側に形成される絶縁膜12と、この絶縁膜12において前記半導体ウェハ11と反対側に形成されるアルミ膜13と、を含む積層構造を備えるセンサウェハ1と、このセンサウェハ1においてアルミ膜13が形成された一面側に接合されるカバーウェハ2と、を備え、センサウェハ1において、アルミ膜13の一部は、絶縁膜12に設けられた貫通孔5内部に突出する凸部6を備えるように形成され、この凸部6と電気的に接触する半導体ウェハ11の所定箇所をコンタクト部7となし、コンタクト部7を介して電流をアルミ膜13に流すことによりセンサウェハ1とカバーウェハ2とをアルミ膜13を介して陽極接合させてなるようにした。

(もっと読む)

ウェハレベルパッケージ構造体

【課題】微小デバイスチップの半導体基板表面における付着物による不良をチップレベルで検知できるようにする。

【解決手段】半導体基板1の一表面側にカバーガラス2が接着され、前記半導体基板の前記一表面側とは反対側の他表面側にベースガラス3が接着されてなる積層構造状のウェハレベルパッケージ構造体であって、前記積層構造状の複数の微小デバイスチップが集合してなり、複数の微小デバイスチップのうちの少なくとも一つの微小デバイスチップは、半導体基板の前記一表面側に接着されたカバーガラス2を分離し得る構造を備え、半導体基板1の前記一表面側が検査対象とされる検査対象用微小デバイスチップTであるようにした。

(もっと読む)

21 - 40 / 113

[ Back to top ]