Fターム[4M118BA19]の内容

固体撮像素子 (108,909) | 基本構造 (11,702) | 受光部(光電変換部)を複数持つもの (11,448) | 半導体結晶型 (10,136) | 受光・転送基板分離型 (196)

Fターム[4M118BA19]に分類される特許

1 - 20 / 196

固体撮像装置、カメラおよび固体撮像装置の設計方法

半導体装置、半導体装置の製造方法、および電子機器

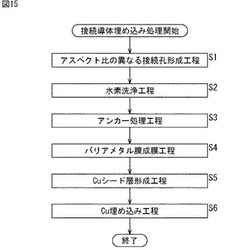

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続した構成の固体撮像装置において、それぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と、第2の基板に配置され、光電変換素子で発生した信号をアナログの読み出し信号として出力する読み出し回路とを具備する画素が複数配置された画素部と、読み出し信号に対して信号処理を行う信号処理回路とを備え、信号処理回路を構成する回路要素を区分基準に基づいて第1の基板側または第2の基板側に区分し、第1信号処理回路に区分された回路要素を第1の基板内に配置し、第2信号処理回路に区分された回路要素を第2の基板内に配置する。

(もっと読む)

固体撮像装置および撮像装置

【課題】複数枚のチップを接続することによって構成される固体撮像装置において、回路規模の増大や、チップ間の接続部の数が増加することなく、それぞれのチップに形成された画素に制御信号を送ることができる固体撮像装置および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と第2の基板に配置された読み出し回路とを有する画素が2次元に複数配置された画素部と、画素からの信号の読み出しを制御する読み出し制御回路とを備え、読み出し制御回路は、パルス生成部と選択部とロジック部とを具備し、読み出し制御回路の構成要素の内、一部の構成要素を第1の基板内に配置し、残りの構成要素を第2の基板内に配置し、接続部を介して、第1の基板と第2の基板とに配置された読み出し制御回路の構成要素を電気的に接続する。

(もっと読む)

撮像素子

【課題】高解像度化した画素を有する撮像素子を提供する。

【解決手段】撮像素子10は、X,Y軸平面上に正方又は六方配置された各感光部から蓄積電荷に相当する信号をZ軸方向に並列に抽出して出力する積層素子100a,100b,100c,100dと、この積層素子における感光部を有する素子100aに対して設けられ、それぞれの感光部に対して一部の領域で受光するための当該感光部の面積よりも小さい面積を有する1つのアパーチャ(開口部)110を、当該感光部の領域の範囲内で走査することにより各感光部を所定の分割数で分割し、当該分割した各領域によって画素を形成するマスク106及びアクチュエータ107とを備える。

(もっと読む)

固体撮像装置、撮像装置、および信号読み出し方法

【課題】複数の基板の面積を有効に活用する。

【解決手段】本発明の一態様に係る固体撮像装置は、第1〜第n(nは2以上の整数)の基板どうしが接続部を介して電気的に接続された固体撮像装置であって、光電変換素子を含む画素が行列状に配置された画素部と、前記画素部内の画素の列に対応して配置され、対応する列の画素に含まれる前記光電変換素子で発生した信号を信号処理する複数の列処理回路を含む列回路部と、前記列処理回路によって信号処理された信号を当該装置の外部に出力する出力部と、を備え、前記第1の基板に前記画素部が配置され、前記第1〜第nの基板のうち少なくとも2以上の異なる基板のそれぞれに前記列回路部が配置され、前記画素部内の各列の画素に対応する信号処理を、前記少なくとも2以上の異なる基板のそれぞれに配置された前記列回路部で分散して行うことを特徴とする。

(もっと読む)

焦電型光検出器、焦電型光検出装置および電子機器

【課題】焦電型光検出器の検出出力を高めること。

【解決手段】焦電型光検出器は、基板10と、基板上に支持される支持部材215と、支持部材に接して形成されている焦電型光検出素子251と、を有する。焦電型光検出素子251は、支持部材側に設けられる第1電極234と、第1電極と対向して設けられ、平面視における面積が、第1電極より小さい第2電極236と、第1電極234と第2電極236との間に設けられる焦電体232と、を含むキャパシター230を有する。焦電型光検出素子251はさらに、キャパシター上に形成されている光吸収層270を含む。平面視における光吸収層の面積を受光部面積Aaとし、平面視における第2電極の面積をキャパシター面積Acとし、Aa/Acは、2.0<Aa/Ac<49.0を満足する。

(もっと読む)

固体撮像素子およびカメラシステム

【課題】チップ内の熱勾配を緩和することが可能で、ひいてはダークシェーディングを緩和することが可能な固体撮像素子およびカメラシステムを提供する。

【解決手段】第1チップは画素アレイ部が配置され、第2チップはロジック部およびレギュレータが配置され、レギュレータは、基準電圧を生成する基準電圧生成部と、複数の出力段トランジスタと、基準電圧と複数の出力段トランジスタの共通化された出力電圧を比較する演算増幅器とを含み、演算増幅器の出力は複数の出力段トランジスタのゲートに接続され、出力段トランジスタの出力経路は一つのノードに接続され、演算増幅器にフィードバックされ、複数の出力トランジスタの電源側端子は外部電源電圧が供給される供給電源端子に接続され、演算増幅器は、基準電圧と複数の出力段トランジスタのノードで共通化された出力電圧を比較して複数の出力段トランジスタのゲート電圧を制御する。

(もっと読む)

固体撮像装置および撮像装置

【課題】MOS型固体撮像素子において、チップ面積に対して画素領域の占める面積比率をより高めることができる。

【解決手段】第1の基板10から第n(nは2以上の整数)の基板が接続部を介して電気的に接続され、かつ段積みされた固体撮像装置であって、第m(mは1以上n以下の整数)の基板は、光電変換素子を含む画素を有する画素領域50を備え、第mの基板以外の他の基板は、画素の駆動の用に供する回路要素を有する第一垂直走査回路160と第二垂直走査回路161とを備え、他の基板の領域のうち、画素領域と垂直方向に重なる重複領域51内に、第一垂直走査回路160と第二垂直走査回路161との少なくとも一部分が配置されている。

(もっと読む)

固体撮像素子ウエハ、固体撮像素子の製造方法、および固体撮像素子

【課題】裏面照射型の固体撮像素子を備えたチップ領域が複数配列された固体撮像素子ウエハにおいて、個片化されるチップ領域のサイズを縮小し、これにより固体撮像素子の小型化を図る。

【解決手段】複数のチップ領域200と、チップ領域200を囲んで配置された分割領域300と、各チップ領域200に設けられた光電変換部20と、各チップ領域200において光電変換部20に対する受光面Aとは逆の表面側に設けられた駆動回路と、駆動回路に接続され各チップ領域200において表面側に引き出されたデバイス用端子33と、駆動回路に接続され分割領域300において受光面A側に露出された検査用端子400とを備えた固体撮像素子ウエハ100−1である。

(もっと読む)

光検出装置

【課題】開口率を著しく向上することが可能な光検出装置を提供すること。

【解決手段】光検出装置1は、半導体基板1Nを有する半導体光検出素子10Aと、半導体光検出素子10に対向配置される搭載基板20とを備える。半導体光検出素子10Aは、ガイガーモードで動作すると共に半導体基板1N内に形成された複数のアバランシェフォトダイオードAPDと、それぞれのアバランシェフォトダイオードAPDに対して電気的に接続されると共に半導体基板1Nの主面1Nb側に配置された電極E7とを含む。搭載基板20は、電極E7毎に対応して主面20a側に配置された複数の電極E9と、それぞれの電極E9に対して電気的に接続されると共に主面20a側に配置されたクエンチング抵抗R1とを含む。電極E7と電極E9とが、バンプ電極BEを介して接続されている。

(もっと読む)

撮像素子

【課題】 撮像性能の向上に適した撮像素子の新たな構造を提供する。

【解決手段】 撮像素子は、第1チップ、および第2チップを備える。この第1チップには、受光画素、および貫通配線とが形成される。複数の受光画素は、受光面に配列され、入射光に応じた電気信号を生成する。貫通配線は、受光画素の電気信号を受光面の反対面へ伝達する。一方、第2チップには、読み出し回路が形成される。読み出し回路は、貫通配線を介して電気信号を読み出して画像信号として出力する。この撮像素子は、上記の第1チップの反対面と、上記の第2チップの読み出し回路とが対向する向きに配置され、貫通配線と読み出し回路との端子間が電気的に接合される。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

3次元構造を持つイメージセンサの分離型単位画素及びその製造方法

【課題】フォトダイオードに入射する光の多様な入射角に対する対応能力を提供する。

【解決手段】3次元構造を持つイメージセンサの分離型単位画素は、半導体物質の導電型とは反対の不純物を含有しているフォトダイオード14および、前記フォトダイオードの光電荷量を外部に転送するためのパッド17を備える第1のウエハ10と、前記フォトダイオードを除いたトランジスタ構成の規則的な配列を持つ画素アレイ領域、前記画素アレイ以外のイメージセンサの構造を持つ周辺回路領域、及び前記各画素を接続するためのパッド21を備える第2のウエハ20と、前記第1のウエハのパッドと前記第2のウエハのパッドとを接続する連結手段30と、を含む。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

量子型赤外線撮像素子およびその製造方法

【課題】

読み出し回路を備えた第一基板と受光素子を備えた第二基板をバンプ接続した量子型赤外線熱感知デバイスにおいて、HgCdTe等で構成された第二基板に影響を与えることなくシリコン基板等で構成された第一基板と、第二基板の熱膨張係数の違いに起因する隣接バンプ間の接触を防止する。

【解決手段】

量子型撮像素子は、読み出し回路を備えた第一基板と、前記第一基板とフリップチップボンディング(FCB)によって電気的に接続された、受光素子を備えた第二基板と、前記第一基板と前記第二基板をFCBによって電気的に接続する導体バンプ群と、各バンプの周囲を囲むように存在し、前記第一基板側にのみ固定され、前記第二基板との間に空隙を設けた絶縁壁とを有する。

(もっと読む)

電子部品および電子機器ならびにこれらの製造方法。

【課題】 光硬化樹脂43および光硬化樹脂43に分散した無機粒子44を有する接着部材4に生じ得る点剥がれを抑制する。

【解決手段】 無機粒子44の体積基準の粒子径分布において、分布累積値が50%となる粒子径をD50、分布累積値が90%となる粒子径をD90、接着部材4の厚みをTとして、D50≧0.5μm、D90≦5.0μm、D90/T≦0.4および5μm≦T≦40μmを満たす。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板間の接合性を改善してボイドの発生を抑制することにより、信頼性の向上が図られた3次元構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1を、第1電極33および第1絶縁膜35を含むと共に、これらの第1電極33および第1絶縁膜35を露出させた貼合せ面41を有する第1基板2と、第1電極33に電気的に接続された第2電極67および第2絶縁膜69を含むと共に、これらの第2電極67および第2絶縁膜69を露出させた貼合せ面71を有し、第1基板2に貼り合わされて設けられた第2基板7と、各基板の貼合せ面41,71の間に狭持された絶縁性薄膜12とを備えた構成とする。

(もっと読む)

固体撮像素子および電子機器

【課題】画質の低下を抑制する。

【解決手段】センサチップは、複数のPDが配置された半導体基板を有している。信号処理チップは、センサチップに積層され、センサチップを駆動するためのロジック回路が形成された半導体基板を有している。そして、センサチップの半導体基板と、信号処理チップの半導体基板との間に、信号の送受信を行う配線を有する配線層が配置されており、その配線層において配線が形成されていない領域に、遮光性を備えた遮光膜が配設される。本技術は、例えば、裏面照射型のCMOS型固体撮像素子に適用できる。

(もっと読む)

1 - 20 / 196

[ Back to top ]