Fターム[4M118FA27]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 分離構造 (2,603) | 溝による分離 (532)

Fターム[4M118FA27]に分類される特許

61 - 80 / 532

固体撮像素子および電子情報機器

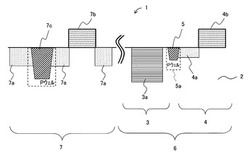

【課題】製造工程も簡易で、信号読み出しも容易であり、素子分離部により素子分離を確実に行い、素子分離部から発生する暗電流を抑制しつつ、N型フォトダイオードの飽和蓄積電子数を増加させる。

【解決手段】光電変換素子部3と信号走査回路部4とを分離するトレンチ分離部5の深さが、周辺回路形成領域7で素子間を分離するトレンチ分離部7cの深さの1/8〜1/2として、画素形成領域6のトレンチ分離部5の深さを浅くする。これによって、トレンチ分離部5の幅の縮小が可能となる。トレンチ分離部5が従来のように基板表面から突出していない。しかも、光電変換素子部3の不純物濃度が最大となるN型電荷蓄積領域の深さがトレンチ分離部5の深さよりも浅く構成されている。

(もっと読む)

固体撮像装置及びカメラ

【課題】少なくとも暗電流の抑制を図ることができる固体撮像装置を提供する。

【解決手段】基板の第1面側に配線層を有し、基板の第2面側から光を受光する固体撮像装置であって、基板に形成された受光部と、基板の第2面側に形成された第1の絶縁膜と、第1の絶縁膜の前記基板と反対側の面に形成された第2の絶縁膜とを備える。第1の絶縁膜は、ハフニウム、ジルコニウム、アルミニウム、タンタル、チタン、イットリウム、及び、ランタノイドから選ばれる少なくとも1種以上の元素を含む酸化物絶縁膜からなる。

(もっと読む)

固体撮像素子およびその製造方法

【課題】裏面入射型の固体撮像素子の製造工程を簡略化する。

【解決手段】固体撮像素子の製造方法は、互いに反対側の面である第1面および第2面を有する半導体基板に対して前記第1面の側からイオンを注入することによって前記半導体基板に光電変換部を形成する第1注入工程と、前記半導体基板に対して前記第1面の側からイオンを注入することにより、第1不純物半導体領域および第2不純物半導体領域を含む混在領域を前記半導体基板に形成する第2注入工程と、前記半導体基板を前記第2面の側から薄化して前記混在領域を露出させる薄化工程と、前記第1不純物半導体領域のエッチングレートと前記第2不純物半導体領域のエッチングレートとが異なるエッチャントを用いて前記混在領域をエッチングすることによって前記混在領域に段差を有するマークを形成するエッチング工程とを含む。

(もっと読む)

固体撮像装置及び撮像装置

【課題】開口率を低下させることなく広ダイナミックレンジを実現することができ、高照度下においても撮像可能な固体撮像装置を提供する。

【解決手段】半導体基板20の表面に形成された画素部が二次元状に配列された撮像領域2Aを有する固体撮像装置であって、撮像領域2Aは、2行2列の画素部からなる画素ブロックを配列単位として構成され、当該画素ブロックは赤色信号を検出する赤色画素11Rと、青色信号を検出する青色画素11Bと、第1の輝度信号を検出する白色画素11W1と、第2の輝度信号を検出する白色画素11W2とで構成されており、白色画素11W2の受光面上部には、可視光線領域の光透過率を低減させる光減衰フィルタが設けられている。

(もっと読む)

固体撮像装置及びその製造方法

【課題】混色及び白傷の少ない画像取得可能な固体撮像装置及びその製造方法を提供する。

【解決手段】第1導電型の基板101と、前記基板内に格子状に形成された素子分離絶縁膜121とを備える。更に、前記装置は前記素子分離絶縁膜により互いに分離された第1導電型の複数の第1半導体領域111,112,113と、前記基板内において前記素子分離絶縁膜上に格子状に形成され、画素分離領域として機能する第1導電型の第2半導体領域115とを備える。更に、前記装置は前記基板内において前記第2半導体領域の側方に形成され、前記第2半導体領域により互いに分離され、電荷蓄積領域として機能する第2導電型の複数の第3半導体領域114と、前記基板内において前記第2及び第3半導体領域上に形成された第1導電型の第4半導体領域116とを備える。更に、前記装置では前記素子分離絶縁膜は、前記第1及び第2半導体領域により側壁面が覆われている。

(もっと読む)

固体撮像装置

【課題】従来の裏面入射型の固体撮像装置においては、撮像面である裏面と反対側の面(表面)から、受光部が設けられた半導体基板内に迷光が入り込む可能性がある。

【解決手段】固体撮像装置1は、半導体基板10、受光部14、および遮光膜20を備えている。固体撮像装置1は、裏面入射型であり、半導体基板10の裏面S2に入射した被撮像体からの光を半導体基板10の内部で光電変換し、その光電変換により発生した電荷を受光部14で受けて当該被撮像体を撮像する。受光部14は、半導体基板10と共にPN接合ダイオードを構成している。半導体基板10の表面S1側には、受光部14を覆うように遮光膜20が設けられている。この遮光膜20は、固体撮像装置1の外部から上記表面S1に入射しようとする光を遮るものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】メタル汚染を防ぐことができる半導体装置の製造方法を得ること。

【解決手段】第1の基板の表面、裏面および側面上に絶縁膜を形成する。つぎに、前記第1の基板の表面側の前記絶縁膜を除去し、前記絶縁膜が除去された前記第1の基板の表面上に接着層を形成する。そして、前記接着層を介して前記第1の基板を、第2の基板と貼り合わせる。

(もっと読む)

固体撮像装置及びその製造方法

【課題】画素領域中央部での電圧降下を抑制することができる固体撮像装置とその製造方法を提供する。

【解決手段】複数の画素部100が二次元配置されてなる画素領域61を有する固体撮像装置1であって、半導体基板5と、半導体基板5上に形成された層間絶縁膜20〜22と、層間絶縁膜20〜22上に形成された下部電極40と、下部電極40上に形成された光電変換膜41と、光電変換膜41上に形成された透光性を有する上部電極42と、を有し、上部電極42は画素領域61全体に拡がっており、上部電極42における少なくとも一部には、隣接する画素部100の間を通り、上部電極42を構成する材料よりも電気抵抗率が小さい材料からなる金属配線45が積層されていることを特徴とする固体撮像装置1とする。

(もっと読む)

撮像素子および撮像装置

【課題】さらなる高性能化を実現する。

【解決手段】固体撮像素子21は、受光した光を電荷に変換する光電変換素子が平面的に配置されたフォトダイオード層25と、フォトダイオード層25の上面に配置される導体構造体層24とを備える。導体構造体層24は、フォトダイオード層25の受光面と平行な平面内で所定の周期間隔の微細加工が施されて形成された微小導体粒子であるアイランド28を有する微小粒子層29が複数積層されて形成されている。本発明は、例えば、デジタルスチルカメラに適用できる。

(もっと読む)

固体撮像装置およびその製造方法

【課題】暗電流や残像の発生を抑制することができる固体撮像装置およびその製造方法を提供する。

【解決手段】固体撮像装置は、半導体基板101をベースに、複数の撮像画素100が形成されてなり、各撮像画素100は、入射光を光電変換して信号電荷を生成する光導電膜126と、半導体基板101内に形成され、光導電膜126で生成された電荷を蓄積する蓄積ダイオード104と、を有する。そして、固体撮像装置において、蓄積ダイオード104に対しては、接続電極110との接続部分を除く部分を覆うようにピニング層107が形成されている。ピニング層107は、n+層である蓄積ダイオード104とは反対の導電型であるp+層であって、電荷の表面再結合を抑制する役割を果たす。

(もっと読む)

撮像素子、撮像モジュール及び撮像素子の製造方法

【課題】生産性を向上した撮像素子、撮像モジュール及び撮像素子の製造方法を提供する。

【解決手段】実施形態の撮像素子は、基板と、光検出部と、回路部と、貫通配線と、を備える。基板は、凹部及び貫通孔を有する。凹部は基板の第1主面に設けられる。凹部は、第1主面とは反対の第2主面の方向に後退して設けられる。貫通孔は第1主面と第2主面とに連通し第1主面から第2主面に向かう第1方向に延在する。光検出部は、凹部の上で基板と離間して設けられる。回路部は、光検出部と導通し、第1主面の上に設けられる。

貫通配線は、回路部と導通し貫通孔の内部に設けられる。凹部は、第1主面に対して傾斜する第1傾斜面を有する。貫通孔は、第1傾斜面に平行な第2傾斜面を有する。

(もっと読む)

固体撮像素子およびその製造方法、電子情報機器

【課題】素子分離領域のパターンと不純物注入の角度を最適化し、イオン注入量を注入場所に応じて制御することにより、画素の読み出し特性を改善しかつ暗電流を抑制する。

【解決手段】受光部2の周囲の素子分離領域、電荷転送トランジスタ素子3の読み出し領域の素子分離領域および電荷電圧変換部としてのフローティング領域4の周囲の素子分離領域に応じて、受光部2とは逆極性の不純物層の不純物濃度を変えている。例えば、受光部2の周囲の素子分離領域の不純物濃度を濃く、電荷転送トランジスタ3の読み出し領域の活性層における素子分離領域の不純物濃度を薄くするようにイオン注入方向を、X軸方向およびY軸方向から所定角度(ここでは45度)で傾き、かつ互いの角度が直角である4方向(図1の矢印(1)〜(4))のイオン注入方向に調整する。

(もっと読む)

固体撮像装置とその製造方法、並びに電子機器

【課題】裏面照射型の固体撮像装置において、白点、暗電流の発生及び混色を抑制し、感度の向上を図る。

【解決手段】光電変換部PDと複数の画素トランジスタからなる画素38が2次元配列された画素領域と、画素領域内に形成され、トレンチ42内にエピタキシャル成長による半導体層43が埋め込まれて構成された画素間を分離する素子分離領域41を有する。さらに、多層配線層33とは反対の半導体基板裏面22b側の受光面を有し、裏面照射型として構成される。

(もっと読む)

CMOS撮像装置アレイの製造方法

【課題】画素間のクロストークが小さく、優れた量子効率を持つCMOS撮像装置の製造方法を提供する。

【解決手段】CMOS撮像装置のための光検出器アレイまたは画素アレイを製造する方法であって、複数の高アスペクト比のトレンチを基板の正面側に形成するステップと、複数のフォトダイオードを基板の正面側に形成し、複数のフォトダイオードの各々が基板の正面に対して平行な面内で高アスペクト比のトレンチによって囲まれるようにするステップとを含む。トレンチをクリーニングするため、酸化物層を複数のトレンチの内壁に形成し、そして複数のトレンチの内壁から酸化物層を除去する。トレンチは高ドープ材料で充填し、基板は裏面から薄型化する。このクリーニングは、側壁を通過する拡散を制限し、トレンチ側壁での不要な電荷キャリア再結合を生じさせ、画素間のクロストークをもたらす欠陥、残留物、不純物をトレンチ側壁から除去する。

(もっと読む)

固体撮像素子及びその製造方法、並びに撮像装置

【課題】集光特性の向上が図られ、フレアやスミア等の光学的雑音が抑制された裏面照射型の固体撮像素子及びその製造方法を提供する。また、その固体撮像素子を用いた固体撮像装置、撮像装置を提供する。

【解決手段】半導体基板の素子分離領域に、半導体基板の裏面側から100nm〜300nmの線幅の第1の溝部61が形成され、第1の溝部61には酸化ハフニウム膜62を介して二酸化シリコン63が埋め込まれている。

(もっと読む)

裏面照射型固体撮像装置

【課題】画像の劣化を抑制する。

【解決手段】裏面照射型固体撮像装置は、半導体層36と、前記半導体層内に形成され、前記半導体層の裏面側から照射された光を信号変換して電荷を蓄積する複数の受光部PDと、前記半導体層の表面上に形成され、前記複数の受光部に蓄積された電荷を読み出す複数の回路部33と、を備える裏面照射型固体撮像装置であって、前記半導体層内の前記裏面から前記表面まで達するように形成され、隣接する2つの前記受光部を分離する不純物分離層34と、前記不純物分離層内の前記裏面側の一部に、前記裏面から前記表面に向かって形成された遮光膜35と、を具備する。

(もっと読む)

固体撮像装置用の部材および固体撮像装置の製造方法

【課題】 隙間のない接合面を有する固体撮像装置用の基板および製造方法を提供する。

【解決手段】 光電変換素子が主面に配された第1基板と第1配線構造とを準備する工程と、周辺回路の一部が主面に配された第2基板と第2配線構造とを準備する工程と、第1基板、第1配線構造、第2配線構造、第2基板とがこの順に配置されるように接合する工程と、を有する。そして、少なくとも第1配線構造の上面あるいは第2配線構造の上面のいずれかに凹部が配置され、凹部の底面は導電体が配されている。

(もっと読む)

固体撮像装置及びその製造方法

【課題】周辺論理回路領域を微細化し、かつ画素特性の劣化を防止する固体撮像装置及びその製造方法を提供する。

【解決手段】本実施形態によれば、固体撮像装置の製造方法は、複数の単位画素領域を有する撮像領域と、撮像領域の周辺に設けられた周辺論理回路領域とを備える固体撮像装置の製造方法である。この方法は、半導体基板上に第1膜厚の電極膜及びブロック膜を形成する工程と、単位画素領域のトランジスタのゲート電極に対応した第1レジストパターンをマスクとして前記ブロック膜を除去し、前記電極膜を薄くする工程と、周辺論理回路領域のトランジスタのゲート電極に対応した第2レジストパターン及び前記ブロック膜をマスクとして前記電極膜を除去する工程と、を備える。

(もっと読む)

固体撮像装置

【課題】電気的容量結合による単位画素セル間の信号混合を抑えることが可能な積層型の固体撮像装置を提供する。

【解決手段】単位画素セル13を備える固体撮像装置であって、単位画素セル13は、シリコン基板1上に形成された光電変換膜6及び画素電極5と、シリコン基板1内に形成され、画素電極5と結線されたゲート電極3を有し、画素電極5の電位に応じた信号電圧を出力する増幅トランジスタ10と、シリコン基板1内に形成され、増幅トランジスタ10のゲート電極3の電位をリセットするリセットトランジスタ11とを有し、固体撮像装置は、単位画素セル13の列に対応して設けられ、対応する列の単位画素セル13の信号電圧を伝達する垂直信号線17と、垂直信号線17に信号電圧を出力させる単位画素セル13の行を選択する垂直走査部15とを備え、垂直信号線17はそれに対応する単位画素セル13の画素電極5の下方に位置する。

(もっと読む)

固体撮像装置

【課題】 暗電流やリーク電流の発生を抑制することが可能な固体撮像装置を提供する。

【解決手段】 固体撮像装置は、光電変換素子が主面に配された第1基板と、導電体を含む第1の接合部を有する第1配線構造と、周辺回路の一部が主面に配された第2基板と、導電体を含む第2の接合部を有する第2配線構造と、を有する。そして、第1基板と、第1配線構造と、第2配線構造と、第2基板とがこの順に配置されるように第1の接合部及び第2の接合部とが接合されている。そして、第1の接合部の導電体と、第2の接合部の導電体とは、導電体に対する拡散防止膜で囲まれている。

(もっと読む)

61 - 80 / 532

[ Back to top ]