Fターム[4M118HA22]の内容

Fターム[4M118HA22]に分類される特許

1 - 20 / 335

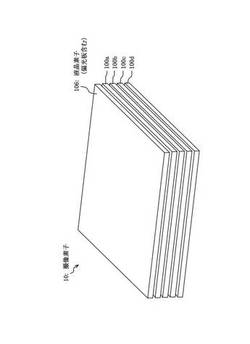

センサユニット及び固体撮像装置

固体撮像素子

撮像素子

【課題】高解像度化した画素を有する撮像素子を提供する。

【解決手段】本発明の撮像素子10は、X,Y軸平面上に正方又は六方配置された各感光部101から蓄積電荷に相当する信号をZ軸方向に並列に抽出して出力する積層素子100a,100b,100c,100dと、この積層素子における感光部101を有する素子100aに対して設けられ、それぞれの感光部101に対して一部の領域を遮光するための当該感光部101の面積よりも小さい面積を有する1つの遮光部110を、当該感光部101の領域の範囲内で走査することにより各感光部101を所定の分割数で分割し、当該分割した各領域における遮光による蓄積電荷の変化量によって画素を形成する液晶素子106とを備える。

(もっと読む)

光電変換素子およびその製造方法、ならびに撮像素子およびその製造方法

【課題】バリア性および耐熱性に優れた光電変換素子およびその製造方法、ならびに撮像素子およびその製造方法を提供する。

【解決手段】基板と、基板上に形成された下部電極と、下部電極上に形成され、光が照射されると電荷を発生する有機層と、有機層上に形成された、可視光に対して透明な上部電極と、上部電極上に形成された素子保護層とを有する光電変換素子の製造方法である。この素子保護層を形成する工程は、有機層に対し不活性なキャリアガスを供給し、プラズマを生成する工程と、キャリアガスが供給されてプラズマが生成された状態で、さらにSiH4ガス、支燃性ガスおよびアンモニアガスを含む反応性プロセスガスを供給して珪素含有保護膜を形成する工程とを有する。

(もっと読む)

固体撮像装置

【課題】TDI動作によって撮像を行う際に、撮像に要する時間を短くすることができる固体撮像装置を提供する。

【解決手段】固体撮像装置1Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、撮像面12に対して列方向の一端側に各列毎に配置されたN個の信号読出回路20、及び、撮像面に対して列方向の他端側に各列毎に配置されたN個の信号読出回路30を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子50と、信号読出回路30から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子60とを備える。

(もっと読む)

半導体装置、および、その製造方法、固体撮像装置

【課題】ショートチャネル特性などを向上する。

【解決手段】n型FET111Nの半導体活性層111Cの上面に、バックゲート絶縁膜401を介してバックゲート電極121を金属材料で形成する。ここでは、バックゲート電極121,221について、半導体活性層111Cの上面においてゲート電極111Gおよび一対のソース・ドレイン領域111A,111Bに対応する部分を被覆するように、バックゲート電極121を形成する。

(もっと読む)

固体撮像装置および撮像装置

【課題】MOS型固体撮像素子において、チップ面積に対して画素領域の占める面積比率をより高めることができる。

【解決手段】第1の基板10から第n(nは2以上の整数)の基板が接続部を介して電気的に接続され、かつ段積みされた固体撮像装置であって、第m(mは1以上n以下の整数)の基板は、光電変換素子を含む画素を有する画素領域50を備え、第mの基板以外の他の基板は、画素の駆動の用に供する回路要素を有する第一垂直走査回路160と第二垂直走査回路161とを備え、他の基板の領域のうち、画素領域と垂直方向に重なる重複領域51内に、第一垂直走査回路160と第二垂直走査回路161との少なくとも一部分が配置されている。

(もっと読む)

半導体装置、固体撮像装置、およびカメラシステム

【課題】隣接ビアを伝送される信号間の干渉を低減でき、ひいてはビア数の増大を抑止でき、センサを搭載したチップの面積、実装工程を低減でき、結果的にコスト削減を図ることができる半導体装置、固体撮像装置、およびカメラシステムを提供する。

【解決手段】第1チップ110と、第2チップ120と、を有し、第1チップ110と第2チップ120は貼り合わされた積層構造を有し、第1チップと第2チップ間の配線は、ビア114を通して接続され、第1チップ110は、各センサ111で発生したアナログ信号を時間離散化した信号が、対応するビアを介して第2チップに伝送され、第2チップ120は、ビアを介した第1チップから伝送された信号を第1チップでサンプリングしたタイミングとは異なるタイミングでサンプリングする機能と、量子化してデジタル信号を得る機能と、を含む。

(もっと読む)

比較器、AD変換器、固体撮像装置、およびカメラシステム

【課題】一層のノイズ低減を図ることができることはもとより、低周波ノイズの低減を図ることができる比較器、AD変換器、固体撮像装置、およびカメラシステムを提供する。

【解決手段】比較器500Aは、第1の入力サンプリング容量C511と、第2の入力サンプリング容量C512と、出力ノードdと、一方の入力端子に、第1の入力サンプリング容量を介して、信号レベルが傾きをもって変化するスロープ信号を受け、他方の入力端子に、第2の入力サンプリング容量を介して入力信号を受けて、スロープ信号と入力信号との比較動作を行う差動比較部としてのトランスコンダクタンス(Gm)アンプ511と、Gmアンプの出力部cと出力ノードdとの間に配置され、Gmアンプの出力部の電圧を一定に保持するアイソレータ530とを有する。

(もっと読む)

撮像素子

【課題】 撮像性能の向上に適した撮像素子の新たな構造を提供する。

【解決手段】 撮像素子は、第1チップ、および第2チップを備える。この第1チップには、受光画素、および貫通配線とが形成される。複数の受光画素は、受光面に配列され、入射光に応じた電気信号を生成する。貫通配線は、受光画素の電気信号を受光面の反対面へ伝達する。一方、第2チップには、読み出し回路が形成される。読み出し回路は、貫通配線を介して電気信号を読み出して画像信号として出力する。この撮像素子は、上記の第1チップの反対面と、上記の第2チップの読み出し回路とが対向する向きに配置され、貫通配線と読み出し回路との端子間が電気的に接合される。

(もっと読む)

固体撮像素子および電子機器

【課題】配線層における導体層の層数の削減をより有効に行うことができる裏面照射型CMOSイメージセンサを提供する。

【解決手段】撮像素子11は、複数の画素31が配置される半導体基板51と、複数本の配線が配設された複数層の導体層58が絶縁膜57に埋め込まれて構成される配線層55とが積層されて構成される。そして、配線層55では、画素31により得られた画素信号を出力する配線、および、画素の駆動に必要な電力を供給する配線、画素を駆動するための駆動信号を供給する配線が、2層の導体層58で形成される。

(もっと読む)

固体撮像装置、固体撮像素子、固体撮像装置の製造方法及び固体撮像素子の製造方法

【課題】高画質化を図ることができる固体撮像装置、固体撮像素子、固体撮像装置の製造方法及び固体撮像素子の製造方法を提供する。

【解決手段】実施形態に係る固体撮像装置は、上面に複数の画素が形成されたセンサ基板と、複数のマイクロレンズが形成されたマイクロレンズアレイ基板と、前記マイクロレンズアレイ基板における前記マイクロレンズ間の領域に一端が接合され、前記上面に他端が接合された接続ポストと、を備える。

(もっと読む)

固体撮像装置、固体撮像素子及び固体撮像素子の製造方法

【課題】高画質化を図ることができる固体撮像装置、固体撮像素子及び固体撮像素子の製造方法を提供する。

【解決手段】実施形態に係る固体撮像装置は、複数の画素が形成された上面が窪むように湾曲したセンサ基板と、前記上面側に設けられた結像レンズと、を備える。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】受光面側にパッド配線を設けた裏面照射型の固体撮像装置において、絶縁膜の薄膜化を図ることにより光電変換部での受光特性の向上を図ることが可能な裏面照射型の固体撮像装置を提供する。

【解決手段】このような目的を達成するための本技術の固体撮像装置は、光電変換部が配列形成された画素領域を有するセンサ基板を備え、このセンサ基板において光電変換部に対する受光面とは逆の表面側には駆動回路が設けられている。また画素領域の外側の周辺領域には、センサ基板における受光面側から駆動回路に達しする貫通ビアが設けられている。さらに、周辺領域の受光面側には、貫通ビア上に直接積層されたパッド配線が設けられている。

(もっと読む)

量子型赤外線撮像素子およびその製造方法

【課題】

読み出し回路を備えた第一基板と受光素子を備えた第二基板をバンプ接続した量子型赤外線熱感知デバイスにおいて、HgCdTe等で構成された第二基板に影響を与えることなくシリコン基板等で構成された第一基板と、第二基板の熱膨張係数の違いに起因する隣接バンプ間の接触を防止する。

【解決手段】

量子型撮像素子は、読み出し回路を備えた第一基板と、前記第一基板とフリップチップボンディング(FCB)によって電気的に接続された、受光素子を備えた第二基板と、前記第一基板と前記第二基板をFCBによって電気的に接続する導体バンプ群と、各バンプの周囲を囲むように存在し、前記第一基板側にのみ固定され、前記第二基板との間に空隙を設けた絶縁壁とを有する。

(もっと読む)

電子部品および電子機器ならびにこれらの製造方法。

【課題】 光硬化樹脂43および光硬化樹脂43に分散した無機粒子44を有する接着部材4に生じ得る点剥がれを抑制する。

【解決手段】 無機粒子44の体積基準の粒子径分布において、分布累積値が50%となる粒子径をD50、分布累積値が90%となる粒子径をD90、接着部材4の厚みをTとして、D50≧0.5μm、D90≦5.0μm、D90/T≦0.4および5μm≦T≦40μmを満たす。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板間の接合性を改善してボイドの発生を抑制することにより、信頼性の向上が図られた3次元構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1を、第1電極33および第1絶縁膜35を含むと共に、これらの第1電極33および第1絶縁膜35を露出させた貼合せ面41を有する第1基板2と、第1電極33に電気的に接続された第2電極67および第2絶縁膜69を含むと共に、これらの第2電極67および第2絶縁膜69を露出させた貼合せ面71を有し、第1基板2に貼り合わされて設けられた第2基板7と、各基板の貼合せ面41,71の間に狭持された絶縁性薄膜12とを備えた構成とする。

(もっと読む)

汎用性相互接続性能を有するイメージセンサ

【課題】より汎用性のあるピクセルアクセス性能を有するイメージングデバイスを提供する。

【解決手段】イメージセンサは、構成可能な相互接続回路を介してアナログ回路へと結合されたイメージセンサピクセルを含む。アナログ回路は、多数のアナログ回路ブロックを含み、関連付けられたイメージセンサピクセルを制御し、そこからの信号を読み出す。構成可能な相互接続回路は、アナログ回路ブロックと、イメージセンサピクセルのうちの特定のグループとの間の接続を再度確立するために制御される。デジタル回路は、アナログ回路へと結合される。デジタル回路は少数のアナログ回路ブロックによって制御される有意に多くのイメージピクセルが存在し、同様に、少数のアナログ回路ブロックは、さらに少数のデジタル回路ブロックによって制御される。イメージセンサピクセルアレイ、構成可能な相互接続回路、アナログ回路およびデジタル回路は、垂直に積層される。

(もっと読む)

赤外線検出素子の製造方法、赤外線検出素子及び電子機器

【課題】犠牲膜をエッチングして形成された空隙を備えるセンサーにおいて、犠牲膜のみをエッチングして空隙を形成する方法を提供する。

【解決手段】基板2上に絶縁膜14を形成する絶縁膜形成工程と、絶縁膜14に凹部15を形成する凹部形成工程と、凹部15に酸化シリコンからなる犠牲膜を形成する犠牲膜形成工程と、犠牲膜上に支持部23を形成する支持部形成工程と、支持部23上に赤外線検出部4を形成する検出部形成工程と、エッチング液を用いて犠牲膜をエッチングして空隙16を形成するエッチング工程と、を有し、絶縁膜はエッチング液に対して耐食性を有する。

(もっと読む)

周辺回路を配置しチップ面積増大を抑制した撮像素子及び撮像装置

【課題】画素部の性能を損なわず、かつ周辺回路のチップ面積増大によるコストの増大を抑制する撮像素子を提供する。

【解決手段】撮像素子において、画素部101のうち、転送スイッチ203およびFD204およびリセットスイッチ207および増幅MOSアンプ205が第1半導体基板に形成され、列読み出し回路103または出力回路107または駆動回路の少なくとも一部が第1半導体基板以外の第2半導体基板に形成されている。

(もっと読む)

1 - 20 / 335

[ Back to top ]