Fターム[4M119DD55]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 選択素子と記憶素子の位置関係 (261) | FETのSDの直上に記憶素子 (256)

Fターム[4M119DD55]に分類される特許

61 - 80 / 256

磁気ランダムアクセスメモリ

【課題】書き込み電流を低減する磁気ランダムアクセスメモリを提供する。

【解決手段】磁気ランダムアクセスメモリは、半導体基板と、半導体基板の上方に配置され、垂直磁化膜で形成されたMTJ素子10と、MTJ素子10の上側に配置されかつ半導体基板に対して引っ張る方向に応力を加える引っ張り応力膜21及びMTJ素子10の下側に配置されかつ半導体基板に対して圧縮する方向に応力を加える圧縮応力膜の少なくとも一方を有する応力膜と、を具備する。

(もっと読む)

半導体記憶装置

【課題】 熱負荷によるTMR比の減少を抑制できる磁気抵抗効果を利用した半導体記憶装置を提供すること。

【解決手段】 実施形態の磁気抵抗素子は、非磁性元素を含む第1の垂直磁化磁性膜116と、第1の垂直磁化磁性膜上に設けられた絶縁膜119と、第1の垂直磁化磁性膜と絶縁膜との間に設けられた第1の中間磁性膜118と、絶縁膜上に設けられ、非磁性元素を含む第2の垂直磁化磁性膜123と、絶縁膜と第2の垂直磁化磁性膜との間に設けられた第2の中間磁性膜120と、第1の垂直磁化磁性膜と第1の中間磁性膜との間、および、第2の中間磁性膜と第2の垂直磁化磁性膜との間の少なくとも一方に設けられ、非磁性元素の拡散に対してバリア性を有する金属窒化物または金属炭化物で形成された拡散防止膜117,121を含む。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 信頼性が劣化しない磁気ランダムアクセスメモリ及びその製造方法を提供することである。

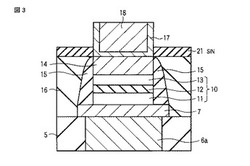

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、半導体基板を持つ。前記半導体基板上に、前記半導体基板上層部に拡散層を有する選択トランジスタが設けられる。前記拡散層上にコンタクトプラグが設けられる。前記選択トランジスタを覆い、前記コンタクトプラグとの側面と接する保護膜が設けられる。前記コンタクトプラグ上に非晶質膜が設けられる。前記非晶質膜上に下部電極が設けられる。前記下部電極上に第1の磁性層が設けられる。前記第1の磁性層上に非磁性層が設けられる。前記非磁性層上に第2の磁性層が設けられる。前記第2の磁性層上に上部電極が設けられる。前記コンタクトプラグ上に、前記下部電極の側面と接する第1の側壁コンタクト膜が設けられる。

(もっと読む)

記憶素子、メモリ装置

【課題】書込電流を増大させることなく、熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子3は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層16とを有する。そして磁化固定層は、非磁性層を上下に強磁性層で挟み込む構造となっており、上下の強磁性層は磁気的に反平行に結合される積層フェリピン構造であり、記憶層、絶縁層、磁化固定層を有する層構造の積層方向にスピン偏極した電子を注入することにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われるとともに、記憶層が受ける、実効的な反磁界の大きさが、記憶層の飽和磁化量よりも小さい。

(もっと読む)

磁気記憶素子及び磁気記憶装置

【課題】スピン注入による磁化反転方式の磁気記憶素子及び磁気記憶装置において、書き換え電流が低く、かつ良好な磁気特性を有する磁気記憶素子及び磁気記憶装置を提供する。

【解決手段】磁化方向が一定方向に固定された固着層(PL)と、固着層(PL)と接する非磁性誘電体層(TN1)と、非磁性誘電体層(TN1)と接する第1面と、第1面と対向する第2面とを備え、磁化方向が反転可能な記憶層(FL)との積層構造からなり、積層構造を流れる電流により記憶層(FL)の磁化方向を反転させる磁気記憶素子において、記憶層(FL)の第1面の全面が非磁性誘電体層(TN1)に覆われ、非磁性誘電体層(TN1)と固着層(PL)との接合面において、接合面を囲むように非磁性誘電体層(TN1)が露出し、固着層(PL)の外縁は記憶層(FL)の外縁より内側に配置される。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 磁気抵抗効果素子において磁化反転のための電流を十分に確保した磁気ランダムアクセスメモリ及びその製造方法を提供する。

【解決手段】 実施形態の磁気ランダムアクセスメモリは、シリコン基板を持つ。前記シリコン基板の表面部にはゲート電極が埋め込まれ、前記ゲート電極を覆うように前記シリコン基板中にはゲート絶縁膜が埋め込まれる。前記ゲート絶縁膜および前記ゲート電極を挟むように、前記シリコン基板の表面部に第1の拡散層および第2の拡散層が設けられる。前記第2の拡散層上には、少なくとも磁化記憶層、非磁性層、および磁化参照層を有する記憶素子が設けられる。

(もっと読む)

集積回路とその製造方法

【課題】今後ますます増加するトランジスタの閾値のばらつきに対して、高速に動作させることができる集積回路を提供する。

【解決手段】集積回路1は、電流制御型のMOS電流論理回路10と、電流制御型のMOS電流論理回路10の定電流用MOSFET16に接続される可変抵抗素子20と、電流制御型のMOS電流論理回路10の閾値のばらつきにより生じる出力基準電圧の変動△VBを検出するアンプ22と、可変抵抗素子20の抵抗値を書き込む回路34と、を備えている。電流制御型のMOS電流論理回路10の基準電圧VBと出力信号との差がアンプ22によって検出され、可変抵抗素子20の抵抗が書き込み回路34によって書き込まれる。回路を構成するトランジスタの閾値がばらついても、集積回路1は高速且つ安定に動作する。

(もっと読む)

記憶素子、メモリ装置

【課題】書込電流を増大させることなく、熱安定性を改善することができる記憶素子の提供、及び記憶層の微細加工時の抵抗上昇の防止。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層16とを有する。そして積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して情報の記録が行われる。ここで記憶層が受ける実効的な反磁界の大きさが、記憶層の飽和磁化量よりも小さいものとされている。これにより書込電流を増大させることなく、熱安定性を改善することができる。また記憶層17を構成する強磁性層は、CoFeBを母材とし且つ当該母材に耐食性元素が添加されている。これにより記憶層の微細加工時の抵抗上昇の防止が図られる。

(もっと読む)

記憶素子及び記憶装置

【課題】垂直磁気異方性を利用したST−MRAMの書込電流の低減及び熱安定性の向上を図り、回路の複雑化や読み出し速度の低下の防止を図る。

【解決手段】膜面に垂直な磁化を有し、情報に対し磁化の向きが変化する記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に非磁性体による絶縁層を有し、上記記憶層、上記絶縁層、上記磁化固定層の積層方向に流れる電流により発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行い、上記記憶層に接し上記絶縁層と反対側の層を、導電性酸化物で構成する。記憶層との界面に酸化物を用いることで垂直磁気異方性が誘起され書込電流低減、熱安定性向上を図り、導電性酸化物を用いることで読み出し時のトンネル磁気抵抗効果に寄与しない抵抗成分が小となり、回路の複雑化や読み出し速度低下の防止を図る。

(もっと読む)

記憶素子及び記憶装置

【課題】垂直磁気異方性を利用したST−MRAMの書込電流の低減及び熱安定性を向上し、回路の複雑化や読み出し速度の低下を防止する。

【解決手段】膜面に垂直な磁化を有し、情報に対して磁化の向きが変化する記憶層と、膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間の非磁性体による絶縁層とを有し、上記記憶層、上記絶縁層、上記磁化固定層の積層方向に流れる電流により発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行い、上記記憶層を、磁性層と導電性酸化物との積層構造で構成する。記憶層において磁性層と酸化物層と積層構造を採ることで垂直磁気異方性が誘起され書込電流が低減し熱安定性が向上し、当該酸化物として導電性酸化物が用いられることで読み出し時にトンネル磁気抵抗効果に寄与しない抵抗成分が小となり、回路の複雑化や読み出し速度の低下を防止する。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】磁気トンネル接合に導入されるダメージによる磁気デバイスの劣化を抑制すること。

【解決手段】上面に凹部26を備える下部電極28と、前記下部電極の前記凹部の内面と前記凹部外の前記下部電極上とに形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に、前記磁気トンネル接合層の側面に達しないように形成された上部電極40と、を具備する磁気デバイス。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】複数のトンネル接合素子の間隔を短縮すること。

【解決手段】上面に凹部26が形成された下地層24と、前記凹部の内面と前記凹部の両側の下地層上とに形成された下部電極28と、前記凹部の両側の前記下部電極上に形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に形成され、前記凹部の上方において電気的に分離された複数の上部電極40と、を具備する磁気デバイス。

(もっと読む)

記憶装置、書込制御方法

【課題】ST−MRAMにおいて記憶素子の破壊を防ぎつつ記憶素子に情報を記憶させ、併せて書込速度の向上を図る。

【解決手段】メモリブロック1−1、1−2に対する書込制御部51−1、51−2とを複数対設け、各書込制御部51−1、51−2が、対を為すメモリブロック1−1または1−2の各記憶素子に書き込まれるべき情報をシフトレジスタ52に格納し、当該シフトレジスタ52から1つの情報をメモリブロック1−1、1−2に出力し、当該出力した情報の書込成否を判定し、書込失敗と判定した場合はメモリブロック1−1、1−2に対して再度同一情報を出力し、書込成功と判定した場合はメモリブロック1−1、1−2において書込可能状態とする前記記憶素子を選択するためのアドレス値を増加させかつ、シフトレジスタ52から次の情報をメモリブロック1−1、1−2に出力する、という書込制御を個々に独立して行う。

(もっと読む)

半導体記憶装置

【課題】上部電極と第2のビット線との間のビアコンタクトの劣化を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に配置された複数の磁気トンネル接合素子と、複数の磁気トンネル接合素子の一端に電気的に接続された複数の選択トランジスタとを備える。第1のビット線が、各磁気トンネル接合素子の一端に1つまたは複数の選択トランジスタを介して接続されている。複数の上部電極は、複数の磁気トンネル接合素子の他端に接続されえいる。第2のビット線は、各磁気トンネル接合素子の他端に上部電極を介して接続されている。上部電極は、第2のビット線に沿って延伸しており第2のビット線の延伸方向に配列された複数の磁気トンネル接合素子の各他端に共通に接続されている。

(もっと読む)

記憶素子、メモリ装置

【課題】スピントルクを利用した磁気メモリにおいて、300℃から400℃程度の温度の熱処理において、垂直磁化が得られ半導体プロセスで容易に作製可能な磁気メモリを実現する。

【解決手段】膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層17に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層17と磁化固定層15の間に設けられる酸化物による絶縁層16とを有する記憶素子において、記憶層もしくは磁化固定層の少なくとも一方は、絶縁層に接する界面側からFe膜、Niを含む膜が順に形成され、熱処理後において界面側でNiに対するFeの組成比が大きい傾斜組成分布が形成されているようにする。

(もっと読む)

磁気異方性物質の自由磁性層を含むストレージノード、これを含む磁気メモリ素子及びその製造方法

【課題】磁気異方性物質の自由層を含むストレージノードと、これを含む磁気メモリ素子及びこれらの製造方法を提供する。

【解決手段】下部磁性層と、下部磁性層上に形成されたトンネルバリアと、トンネルバリア上に形成され、スピン電流により磁化方向がスイッチングされる自由層と、を含み、自由層は水平または垂直磁気異方性物質層を含み、自由層下に形成された少なくとも一つの物質層を包むキャップ構造を持つ磁気メモリ素子のストレージノード。

(もっと読む)

不揮発性ラッチ回路および半導体集積回路

【課題】 抵抗変化素子の磁化特性が劣化することを防止し、読み出しマージン等の電気的特性の低下を防止する。

【解決手段】 不揮発性ラッチ回路は、相補の記憶ノードである第1および第2ノードを含むラッチ回路と、電流を流すことにより抵抗値が変化する第1および第2抵抗変化素子と、第1および第2抵抗変化素子をラッチ回路に接続するスイッチ回路とを有している。スイッチ回路は、外部からラッチ回路に論理が書き込まれる通常動作時に、第1および第2抵抗変化素子とラッチ回路との接続を遮断する。これにより、外部からラッチ回路の論理が書き換えられるときに、第1および第2抵抗変化素子に電流が流れることを防止でき、抵抗変化素子の磁化特性が劣化することを防止できる。この結果、読み出しマージン等の電気的特性の低下を防止できる。

(もっと読む)

マルチレベルセル(MLC)磁気メモリセルを有する装置およびマルチレベルセル磁気メモリにデータを記憶させる方法

【課題】スピントルク注入ランダムアクセスメモリ(STRAM)メモリセルのような磁気メモリ素子にデータを書込むための方法および装置を提供する。

【解決手段】さまざまな実施の形態に従うと、マルチレベルセル(MLC)磁気メモリセルスタックは、第1の制御線に接続された第1および第2の磁気メモリ素子と、第2の制御線に接続されたスイッチング素子とを有する。第1のメモリ素子は並列に第2のメモリ素子と接続され、第1および第2のメモリ素子はスイッチング素子に直列に接続される。第1および第2のメモリ素子は、さらに、スタック内において、異なる、重ならない高さに配置される。プログラミング電流が第1および第2の制御線の間に流れて、第1および第2の磁気メモリ素子を、異なるプログラムされた抵抗に同時に設定する。

(もっと読む)

磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法

【課題】本発明は、磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法を提供する。

【解決手段】磁気トンネル接合構造体の製造方法は、基板上に第1磁性層、トンネル絶縁層、及び第2磁性層を順次に積層して磁気トンネル接合層を形成し、前記第2磁性層上にマスクパターンを形成し、少なくとも1回のエッチング工程と少なくとも1回の酸化工程を複数回行い、磁気トンネル接合層パターン及び前記磁気トンネル接合層パターンの少なくとも一つの側壁上に側壁絶縁層パターンを形成し、前記少なくとも一つのエッチング工程は、不活性ガスと前記マスクパターンを利用して前記磁気トンネル接合層の一部をエッチングする第1エッチング工程を含み、前記少なくとも一つの酸化工程は、前記磁気トンネル接合層のエッチング面に付着した第1エッチング生成物を酸化する第1酸化工程を含む。

(もっと読む)

磁気抵抗効果メモリ

【課題】読み出しディスターブを低減する磁気抵抗効果メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗効果メモリは、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、第1の磁性層と第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子1と、磁気抵抗効果素子1にパルス形状の読み出し電流を流して、前記磁気抵抗効果素子に記憶されたデータを判別する読み出し回路2と、を具備し、読み出し電流のパルス幅は、第2の磁性層内に含まれる磁化が、初期状態から共動してコヒーレントに歳差運動するまでの期間より短い。

(もっと読む)

61 - 80 / 256

[ Back to top ]