Fターム[4M119DD55]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 選択素子と記憶素子の位置関係 (261) | FETのSDの直上に記憶素子 (256)

Fターム[4M119DD55]に分類される特許

21 - 40 / 256

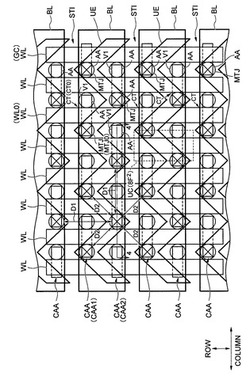

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

記憶素子及び記憶装置

【課題】書込電流と熱安定性をバランスさせた記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層とを有する。そして記憶層、絶縁層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層のサイズが磁化の向きの変化が一斉に生じる大きさよりも小さくなっている。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁気ランダムアクセスメモリの読み出しマージンを増大させる。

【解決手段】メモリセル200は、磁気記録層2と、磁気記録層2に接合された固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42と、リファレンス層41、42と磁気記録層2との間にそれぞれに挿入されたトンネルバリア膜31、32とを備えている。固定層11、12は、互いに逆の方向に固定された磁化を有している。リファレンス層41、42とトンネルバリア膜31、32とは、固定層11、12の間の位置に設けられている。リファレンス層41、42は、互いに逆の方向に固定された磁化を有している。

(もっと読む)

エッチング装置及び半導体装置の製造方法

【課題】難エッチング材料を、高速、高精度及び低ダメージでエッチングする。

【解決手段】実施形態に係わるエッチング装置は、上面側に披処理基板19が搭載されるステージ11と、ステージ11の上面側を覆うチャンバー12と、ステージ11の下面側に付加され、開口部を有する下部電極13aと、チャンバー12内にエッチングガスを供給するガス供給部14と、下部電極13aに高周波を印加することにより、チャンバー12内のエッチングガスをプラズマ化する高周波電源部17と、下部電極13aの開口部を介して被処理基板19にマイクロ波を印加することにより、披処理基板19の温度を最適範囲内に設定するマイクロ波発生部15と、ガス供給部14、高周波電源部17及びマイクロ波発生部15を制御する制御部18とを備える。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果は、下部電極と、第1の磁性層と、第1の金属層と、第1の界面磁性層と、非磁性層と、第2の界面磁性層と、第2の金属層と、第2の磁性層と、上部電極層と、を持つ。前記第1の磁性層は、前記下部電極上に設けられて第1の金属原子を含む。前記第1の金属層は、前記第1の磁性層上に設けられて前記第1の金属原子を含む。前記第1の界面磁性層は、前記第1の金属層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の界面磁性層は、前記非磁性層上に設けられる。前記第2の金属層は、前記第2の界面磁性層上に設けられ、第2の金属原子を含む。前記第2の磁性層は、前記第2の金属層上に設けられ、前記第2の金属原子を含む。前記上部電極層は、前記第2の磁性層上に設けられる。前記第1の界面磁性層は、前記非磁性層側と反対側の界面にアモルファス金属層を含む。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果素子は、下部電極と、第1の磁性層と、第1の界面磁性層と、第2の界面磁性層と、第2の磁性層と、上部電極とを持つ。前記第1の磁性層は前記下部電極上に設けられる。前記第1の界面磁性層は、前記第1の磁性層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の磁性層は前記第2の界面磁性層上に設けられる。前記上部電極は、前記第2の磁性層上に設けられる。前記第1および第2の磁性層は、それぞれ磁化記憶層および磁化参照層の一方および他方である。前記上部電極は、貴金属と遷移元素もしくは希土類元素の合金層もしくは混合物層、または導電性酸化物層を含む。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

半導体記憶装置

【課題】MTJ素子にデータを書き込むために充分に大きな電流を駆動することができるセルトランジスタを備え、かつ、容易に製造可能なメモリを提供する。

【解決手段】本実施形態によるメモリはアクティブエリアを備え、セルトランジスタはアクティブエリアに形成されている。MTJ素子の一端がセルトランジスタのソース/ドレインの一方に電気的に接続されている。第1のビット線は、セルトランジスタのソース/ドレインの他方に電気的に接続されている。第2のビット線は、MTJ素子の他端に電気的に接続されている。ワード線は、セルトランジスタのゲートに電気的に接続され、あるいは、セルトランジスタのゲートとして機能する。1つの第1のビット線に対して複数の第2のビット線が対応している。MTJ素子が同一のワード線および同一のアクティブエリアを共有している。アクティブエリアは、第1および第2のビット線の延伸方向に連続して形成されている。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリセル及びランダムアクセスメモリ

【課題】信頼性の高い低消費電力不揮発性メモリを提供する。

【解決手段】磁気メモリセルが備えるトンネル磁気抵抗効果素子402の強磁性自由層200の磁化容易軸方向に対して直交する方向、特に膜面垂直方向に45度の角度をなす方向に適当な磁界を印加した状態でスピントランスファートルクにより強磁性自由層の磁化反転を行う。

(もっと読む)

磁気記憶装置及び磁気記憶装置の製造方法

【課題】 基準素子の抵抗値のばらつきを抑制することが望まれている。

【解決手段】 基板上に磁気抵抗素子及び基準素子が形成されている。磁気抵抗素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、自由磁化層の磁化方向によって低抵抗状態と高抵抗状態との間で抵抗が変化し、第1の方向に長い平面形状を有する。基準素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、磁気抵抗素子の低抵抗状態の抵抗と高抵抗状態の抵抗との間の抵抗を有し、第1の方向と直交する第2の方向に長い平面形状を有する。

(もっと読む)

記憶素子及び記憶装置

【課題】外部放射線に対し耐性を有し、誤動作なく安定した動作する信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層は、Bを含有する強磁性層を含み、Bにふくまれる10Bの同位体比率が、自然界における19.9%よりも低くなっている。

(もっと読む)

記憶素子及び記憶装置

【課題】書き込み電流(反転電流)および熱安定性のばらつきを抑制し、安定して動作する、信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の面内磁化状態により保持する記憶層と、該記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層とを有する。

そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行うとともに記憶層の困難軸方向の異方性磁界が、垂直方向の異方性磁界よりも小さくなっている。

(もっと読む)

記憶素子及びメモリ

【課題】書き込み電流を増大させることなく、熱安定性を改善することができるメモリを提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層を有し、この記憶層に対して、中間層を介して磁化固定層が設けられ、中間層が絶縁体から成り、積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる記憶素子と、この記憶素子の積層方向に流す電流を供給する配線とを備え、記憶素子の上に隣接して積層された層に、記憶層と熱膨張係数の異なる、TiN,WN,TaN,Moのうちのいずれかの材料が用いられ、記憶層に歪が印加されているメモリを構成する。

(もっと読む)

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、熱安定性及び反転電流のバラツキを抑制する。

【解決手段】上記記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、上記記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。この構成において、記憶層の飽和磁化をMs(emu/cc)、上記記憶層の膜厚をt(nm)としたときに、記憶層の膜厚tは、(1489/Ms)−0.593<t<(6820/Ms)−1.55を満たすようにする。

(もっと読む)

21 - 40 / 256

[ Back to top ]