Fターム[4M119DD55]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 選択素子と記憶素子の位置関係 (261) | FETのSDの直上に記憶素子 (256)

Fターム[4M119DD55]に分類される特許

141 - 160 / 256

抵抗変化型メモリ

【課題】製造コストの低減及び動作特性の向上が可能な抵抗変化型メモリを提供する。

【解決手段】本発明の例に関わる抵抗変化型メモリは、第1の方向に延在するビット線BL1と、第2の方向に延在するビット線bBL1,bBL2と、ワード線WL1,WL2と、制御端子がワード線WL1に接続され、電流経路の一端が第2のビット線bBL1に接続される選択トランジスタST1と、制御端子がワード線WL2に接続され、電流経路の一端がビット線bBL2に接続され、電流経路の他端が選択トランジスタST1の他端と共有ノードN1をなす選択トランジスタST2と、一端がビット線BL1に接続され、他端が共有ノードN1に接続される抵抗変化型記憶素子10と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子の特性バラツキを低減することで、動作マージンを大きくすることが可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、メモリ領域に配置され、かつ抵抗値の変化に応じてデータを記憶し、かつ第1の配線SLに一端が電気的に接続され、第2の配線に他端が電気的に接続された複数の可変抵抗素子23と、メモリ領域に配置され、かつ可変抵抗素子23と同じ材料からなり、かつ電気的に絶縁された複数のダミー素子28とを含む。MTJ素子23及びダミー素子28を合わせた素子アレイは、格子状の密集パターンを有している。すなわち、MTJ積層膜を加工する際のレジストパターンを格子状の密集パターンによって形成する。そして、このレジストパターンを用いてMTJ積層膜を加工することで、MTJ素子23とダミー素子28とを合わせた素子アレイを格子状の密集パターンに配置する。

(もっと読む)

磁気抵抗効果素子および磁気記憶装置

【課題】低コストでホイスラー合金の規則化を促進させ、高い磁気抵抗効果を実現すること。

【解決手段】下地層11に自由磁化層12、非磁性層13、固定磁化層14、反強磁性層15および保護層16を積層した積層構造を有する磁気抵抗効果素子1において、自由磁化層12を固定磁化層14のうち少なくともいずれか1層をホイスラー合金で形成し、下地層、非磁性層13、保護層16のうち少なくとも1層をB2規則化構造の合金層で形成する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】スピン注入型の磁気ランダムアクセスメモリに関し、より小さいサイズのメモリセル選択トランジスタで効率的な書き込みが可能な磁気ランダムアクセスメモリを提供する。

【解決手段】ビット線24、接続導体層25及びMTJ素子30が形成された層間絶縁膜22上には、層間絶縁膜26が形成されている。層間絶縁膜26には、接続導体層25に接続されたプラグ27と、MTJ素子30に接続されたプラグ28とが埋め込まれている。層間絶縁膜26上には、プラグ27とプラグ28とを電気的に接続する局所内部配線29が形成されている。これにより、MTJ素子30のフリー層側は、プラグ28、局所内部配線29、プラグ27、接続導体層25、プラグ23、接続導体層21、及びプラグ19を介して、n型ドレイン領域16に電気的に接続されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】磁気抵抗変化素子を備えたメモリセルに記憶された2値の情報を適切に読み出すことができる半導体記憶装置等を提供する。

【解決手段】記憶用磁気抵抗変化素子を備えた複数のメモリセルを含むメモリセルアレイ51と、参照用磁気抵抗変化素子を備えた複数の参照セルを含み、参照電流を出力する参照セルアレイ53と、前記参照電流から求められる参照抵抗値と前記記憶用磁気抵抗変化素子の抵抗値とを比較して当該メモリセルに記憶されている情報を判定する判定手段56と、が設けられている。更に、前記参照セルアレイが前記参照電流を出力する際に、前記複数の参照用磁気抵抗変化素子から選択される高抵抗状態の参照用磁気抵抗変化素子及び低抵抗状態の参照用磁気抵抗変化素子を特定する情報並びにこれらの接続関係を示す制御情報を記憶する記憶手段55と、前記制御情報に基づいて前記参照セルアレイの動作を制御する制御手段54と、が設けられている。

(もっと読む)

垂直異方性を有するST−RAMセル

磁気トンネル接合セルとも称される、磁気スピントルクメモリセルは、関連した強磁性層についての、ウェハ平面に垂直に揃えられた、または「面外」の磁気異方性(すなわち、ゼロ磁場およびゼロ電流における磁化方向)を有する。メモリまたは磁気接合セルは、強磁性自由層と、第1の固定基準層と、第2の固定基準層を有し、各々は、基板に対して垂直な磁気異方性を有する。自由層は、スピントルクによって、第1の方向から反対の第2の方向へ切換可能な、基板に垂直な磁化方向を有する。  (もっと読む)

(もっと読む)

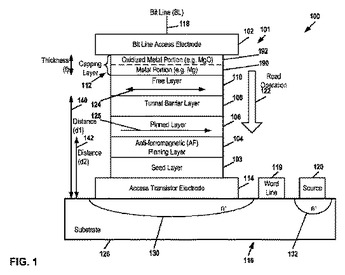

磁気トンネル接合デバイスおよび製造

磁気トンネル接合デバイスおよび製造方法が開示される。特定の実施形態では、方法は、磁気トンネル接合構造のフリー層(110)上にキャップ材料(112)を堆積させてキャップ層を形成するステップと、キャップ材料の一部分を酸化して酸化された材料の層を形成するステップを含む。  (もっと読む)

(もっと読む)

スピントルク移動磁気抵抗ランダムアクセスメモリ(STT‐MRAM)のソースローディング効果の低減

STT‐MRAMのソースローディング効果を低減するシステム及び方法が開示される。特定の実施形態では、本方法は、メモリセルの安定動作を可能にする磁気トンネル接合(MTJ)構造のスイッチング電流比を決定することを含む。メモリセルは、アクセストランジスタに直列に結合されたMTJ構造を含む。本方法は、MTJ構造の自由層に入射するオフセット磁場を変更することも含む。変更されたオフセット磁場によって、MTJ構造がそのスイッチング電流比を示すようにする。  (もっと読む)

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】磁気抵抗効果素子の信頼性の向上と素子の微細化を両立する。

【解決手段】本発明の例に関わる磁気抵抗効果素子は、下部電極20上に設けられる第1の強磁性層11と、強磁性層11上に設けられるトンネルバリア層12と、トンネルバリア層12上に設けられる第2の強磁性層13と、強磁性層13上に設けられる上部電極21と、具備し、上部電極21は六角形状の断面形状を有し、上部電極21の最大寸法Waが、トンネルバリア層12の寸法Wcよりも大きい。

(もっと読む)

磁気ランダムアクセスメモリの製造方法及び混載メモリの製造方法

【課題】パターンの合わせずれを抑制する。

【解決手段】磁気ランダムアクセスメモリの製造方法は、下部電極9上に磁気抵抗効果素子の磁性材10を形成する工程と、磁性材上に上部電極14を形成する工程と、上部電極上にナノインプリントリソグラフィ用のレジストを塗布する工程と、磁気抵抗効果素子及び下部電極の第1のパターンが作り込まれた第1のテンプレート20又は磁気抵抗効果素子及び上部電極の第2のパターンが作り込まれた第2のテンプレートをレジストに接触させて硬化させることで、レジストに第1のパターン又は第2のパターンを形成する工程と、第1のパターンを有するレジストを用いて磁性材及び下部電極を一括でパターニングする、又は、第2のパターンを有するレジストを用いて磁性材及び上部電極を一括でパターニングする工程とを具備する。

(もっと読む)

磁気メモリ装置

【課題】磁気メモリ装置のメモリセルを縮小化する。

【解決手段】MTJ素子と選択トランジスタとが直列接続された1T1MTJメモリセルでは、MTJ素子に流す電流の向きによって選択トランジスタの電流駆動能力が異なることに鑑み、電流駆動能力の低い方でMTJ素子に流される書き込み電流が、電流駆動能力の高い方でMTJ素子に流される書き込み電流より小さくなるように、MTJ素子の特性を調整することで、より小さなサイズの選択トランジスタが使用できるようにする。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能なロジック回路とMRAMを備えた半導体記憶装置を提供する。

【解決手段】第1MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Aが形成されている。ソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Bが形成されている。コンタクトプラグ16A上には第1配線層M1Aが形成されている。磁気抵抗効果素子19は、コンタクトプラグ16B上の、第1配線層M1Aと半導体基板面から同じ高さの層に配置されている。第2MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Cが形成されている。そして、第1配線層M1Bは、コンタクトプラグ16C上の、第1配線層M1A及び磁気抵抗効果素子19と半導体基板面から同じ高さの層に配置されている。

(もっと読む)

不揮発性磁気メモリ装置

【課題】垂直磁化型の記録層における磁化容易軸をより確実に垂直方向に向かせ得る構成、構造を有する不揮発性磁気メモリ装置を提供する。

【解決手段】不揮発性磁気メモリ装置は、(A)磁化容易軸が垂直方向を向いている記録層53を有する積層構造体50、(B)積層構造体50の下部に電気的に接続された第1の配線41、並びに、(C)積層構造体50の上部に電気的に接続された第2の配線42から成る磁気抵抗効果素子を備えており、積層構造体50の側面に近接して、記録層53を構成する材料のヤング率よりも高い値のヤング率を有する高ヤング率領域171が配置されている。

(もっと読む)

フローティングボディー効果を利用した磁気抵抗メモリセル、これを含むメモリ素子及びその動作方法

【課題】高集積の磁気抵抗メモリ素子に必要な選択トランジスタの電流駆動能力をフローティングボディー効果によって向上させた磁気抵抗メモリセル、これを含む磁気抵抗メモリ素子及びその動作方法を提供する。

【解決手段】磁気抵抗メモリセルは、磁気トンネル接合素子及び選択トランジスタを含む磁気抵抗メモリセルであり、選択トランジスタは、第1導電型の半導体層101;半導体層101上にゲート絶縁膜22を介して形成されたゲート電極20;半導体層101内に相互離隔して形成され、第2導電型を持つ第1及び第2拡散領域40;を含む。ここで、第1及び第2拡散領域40の間の半導体層101の一部が電気的にフローティングされたボディー領域103に形成される。本発明によれば、フローティングボディー効果を利用した高性能の選択トランジスタを適用することで、磁気抵抗メモリ素子の高集積化を達成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMデバイスを含む半導体装置において、外部磁界に対する耐性を向上させることにより、MRAMデバイスのデータ保持特性の向上を図ることができる技術を提供する。

【解決手段】ダイパッドDP上にダイアタッチフィルムDAF1を介して磁気シールド材PM1を配置する。そして、この磁気シールド材PM1上にダイアタッチフィルムDAF2を介して半導体チップCHPを搭載する。さらに、半導体チップCHP上にダイアタッチフィルムDAF3を介して磁気シールド材PM2を配置する。つまり、半導体チップCHPは、磁気シールド材PM1と磁気シールド材PM2で挟まれるように配置する。このとき、磁気シールド材PM2の平面的な面積は、磁気シールド材PM1の平面的な面積よりも小さくなっているが、磁気シールド材PM2の厚さは、磁気シールド材PM1の厚さよりも厚くなっている。

(もっと読む)

半導体装置の製造方法

【課題】 簡便で自己整合な方法で形成されたボーダレスコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】 基板上に第1絶縁層を形成する工程と、第1絶縁層の上に素子を形成する工程と、第1絶縁層の上に、素子を覆う第2絶縁層を形成することで、素子の上に第2絶縁層の突出部を形成する工程と、第2絶縁層の上に上面が平坦なレジスト層を形成する工程と、第2絶縁層の突出部が露出するまでレジスト層を削除する工程と、レジスト層をマスクとして素子の上面が露出するまで第2絶縁層をエッチングする工程と、を含み、第2絶縁層及び素子上に配線層を形成する工程を更に備える。

(もっと読む)

抵抗変化型メモリデバイス

【課題】準安定状態への遷移確率を減らし、注入電流の広い範囲にわたって安定な磁化反転を実現する。

【解決手段】抵抗変化型のメモリセルMCと、複数のパルスからなる書き込みパルス(電流値:Iz)と、書き込みパルスのパルス間レベルを規定するオフセットパルス(電流値Iz0)との合成パルスを発生し、発生した合成パルスをメモリセルMCに書き込み時に与える駆動回路と、を有する。

(もっと読む)

抵抗変化型メモリデバイス

【課題】準安定状態への遷移確率を減らし、注入電流の広い範囲にわたって安定な磁化反転を実現する、スピントランスファ効果を利用してデータの書き込みを行う抵抗変化型メモリデバイスを提供する。

【解決手段】抵抗変化型のメモリセルMC内に、記憶層磁化53の向きが反転可能な記憶層16を含み接続プラグ31上に形成された磁性層12,14,16を含むトンネル磁気抵抗効果素子1の積層体を有し、積層体の各層の中心を結ぶ線が、当該積層体が形成された接続プラグ31の上面と垂直な方向から斜めに傾いている。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】ユニットセルの選択用のワードラインとは別個に磁気抵抗素子の書き込み用のワードラインを設けることなく、選択トランジスタ上に磁気抵抗素子が積層された半導体記憶装置を提供する。

【解決手段】不純物層12、チャネル層13および不純物層16を支柱状に半導体基板11上に順次積層し、チャネル層13の周囲を取り巻くようにゲート絶縁膜14を介してゲート電極15を配置することで選択トランジスタ31を構成し、磁性層17、非磁性層18および磁性層19を不純物層16上に順次積層することで、選択トランジスタ31上にスピン注入磁化反転素子32を形成する。

(もっと読む)

磁気抵抗素子、及び磁気メモリ

【課題】非磁性層を挟む2つの磁性層間のショートを防ぎつつ、素子形状のばらつきを低減する。

【解決手段】磁気メモリは、基板20上に設けられた層間絶縁層26と、層間絶縁層26上に設けられた導電性の下地層11と、下地層11上に設けられ、かつ2つの磁性層12、13と、これらに挟まれた非磁性層13とを有する磁気抵抗素子とを含む。下地層11のエッチングレートは、各磁性層のそれよりも低い。

(もっと読む)

141 - 160 / 256

[ Back to top ]