Fターム[4M119EE13]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | ヨーク(クラッド)構造 (106) | 配線の3面にヨーク形成 (50)

Fターム[4M119EE13]に分類される特許

1 - 20 / 50

電子装置、半導体装置およびその制御方法、ならびに携帯端末装置

【課題】選択されない磁気抵抗素子の磁化状態が誤って書き換えられる現象の発生が確実に抑制される半導体装置の制御方法を提供する。

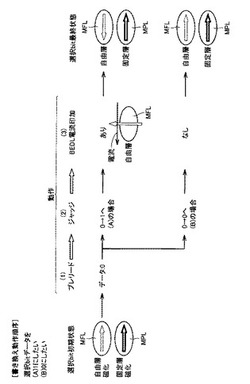

【解決手段】当該制御方法は、半導体基板と、半導体基板の主表面上に位置する、固定層MPLと、トンネル絶縁層と、磁化容易軸を有する自由層MFLとを含む磁気抵抗素子と、磁気抵抗素子に隣接する第1の配線とを備える半導体装置における磁化状態を書き換える制御方法である。上記制御方法は以下の工程を備えている。まず上記自由層MFLの磁化状態を変更する前の初期磁化状態が判定される。上記判定する工程において、自由層MFLの磁化状態を変更する必要があると判定された場合に、第1の配線にパルス電流が流される。上記パルス電流により、自由層MFLの磁化容易軸と交差する方向に発生するパルス磁場を磁気抵抗素子に印加することにより自由層MFLの磁化状態が変更される。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置

【課題】磁気抵抗素子を有する半導体装置であって、フリー層に所望の磁化方向と反対方向の磁界の成分が印加されることによる誤動作を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板の主表面上に位置する、磁化自由層を有する磁気抵抗素子TMRと、磁気抵抗素子TMRの下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第1配線DLと、磁気抵抗素子TMRの上方に位置し、第2方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第2配線BLとを備えている。磁化自由層は、第2方向に対して対称であり、平面視における第2方向に垂直な方向に対して非対称である。上記第1配線DLは、磁化自由層と平面視において重なる領域において、磁化自由層が磁化されやすい方向に延びる磁化容易軸の延在する方向Heに沿うように延在している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置およびその製造方法

【課題】生産コストを抑えながら高いスループットが得られる半導体装置の製造方法と半導体装置とを提供する。

【解決手段】ヨークカバーとなる積層膜として、バリアメタル層、磁性体層およびバリアメタル層が順次形成される。次に、積層膜MLに、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理、一酸化炭素(CO)、アンモニア(NH3)ガスおよびアルゴン(Ar)ガスの混合ガスによる反応性イオンエッチング処理、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理を施すことにより、ヨークカバーYCが形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

シフトレジスタ型記憶装置及びデータ記憶方法

【課題】信頼性が高いシフトレジスタ型記憶装置及びデータ記憶方法を提供する。

【解決手段】一態様によれば、一方向に沿って連なり、その特徴方向が前記一方向に延びる回転軸についてそれぞれ回転可能な複数の回転子を備えたシフトレジスタが提供される。前記複数の回転子には一軸異方性が付与され、前記複数の回転子は、隣り合う2つの前記回転子毎に複数の対に組分けされており、同一の前記対に属する2つの前記回転子には、前記特徴方向を反平行とするような第1の力が作用し、隣り合う前記対に属する隣り合う2つの前記回転子には、前記第1の力よりも弱く、前記特徴方向を反平行とするような第2の力が作用する。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になったデータの誤反転を抑制して信頼性の高い書き込み動作を行うことができる磁気記憶素子およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91とそれに交差する磁化困難軸92とを有する記録層3と、磁化容易軸91の方向と交差する方向に磁界を形成するライト線WTと、記録層3の配置位置において磁化困難軸92の方向と交差する方向に磁界を形成するビット線BLとを備え、記録層3は、ライト線WTとビット線BLとの間に挟まれるように配置されており、ライト線WTおよびビット線BLと記録層3とが積層された積層方向からみた記録層3の平面形状は、積層方向からみてライト線WTが延びる方向に沿うライト線WTの仮想の第1の中心線AWに対して一方側に位置する一方の部分と他方側に位置する他方の部分とを有し、積層方向からみた一方の部分の面積S2が他方の部分の面積S1の1/3以下である。

(もっと読む)

磁気記憶装置

【課題】配線に流れる電流によって発生した誘導磁界による磁気記憶素子の誤作動を低減しつつ、大容量化および高集積化を図ることができる磁気記憶装置を提供する。

【解決手段】複数の磁気記憶素子3とビット線4と複数のトランジスタ2と磁気シールド用磁性膜22とを備えている。磁気記憶素子3は、磁化方向が一定である固着層19、磁化方向が可変である記憶層21、および、固着層19と記憶層21との間に配置されたトンネル絶縁膜20を有し、スピン偏極した電子により記憶層21の磁化方向を反転させる。ビット線4は、複数の磁気記憶素子3のそれぞれが互いに間隔を置いて接続され、複数の磁気記憶素子3に対向して配置されている。トランジスタ2は、複数の磁気記憶素子3の内の対応した磁気記憶素子3を経由してビット線4に電気的に接続されている。磁気シールド用磁性膜22は、ビット線4と磁気記憶素子3との間に配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子への不純物の侵入や応力の負荷を抑制し、低い駆動電力で高精度に作動する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する磁気抵抗素子MRDとを備えている。その他、保護層IIIと、配線BLと、第1上部電極UEL1と、第2上部電極UEL2とを備えている。保護層IIIは、磁気抵抗素子MRDの側面を覆うように配置されている。配線BLは、上記磁気抵抗素子MRDの上部に位置する。第1上部電極UEL1は、上記磁気抵抗素子MRD上に、平面視における大きさが磁気抵抗素子MRDと実質的に同じであるものが配置されている。第2上部電極UEL2は、上記第1上部電極UEL1上にて、上記第1上部電極UEL1と電気的に接続されており、平面視における大きさが第1上部電極UEL1より大きい。

(もっと読む)

半導体装置

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】半導体基板は主表面を有する。磁気抵抗素子32は半導体基板の上記主表面上に位置する。配線43は上記磁気抵抗素子32上に位置する。バリア層41a、410は上記配線43の側面および上面を連続するように覆うように配置される。クラッド層41c、41dは上記バリア層41a、410の、配線43に対向する表面と反対側の表面を連続して覆うように配置される。上記磁気抵抗素子32と上記配線43と上記バリア層41a、410と上記クラッド層41c、41dとを含むメモリユニットが複数形成される。複数の上記メモリユニットが配線43の延在する方向に交差する方向に並列しており、複数のメモリユニット間でクラッド層41c、41dが分離されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】下部電極31は、半導体基板100の主表面上に形成される。磁気抵抗素子32は、固定層35と、トンネル絶縁膜38と、自由層37とを含む。上部電極44は、自由層37のトンネル絶縁膜38と対向する一方の主表面と反対側に位置する他方の主表面上に配置される。磁気抵抗素子32を構成する固定層35は、下部電極31の一方の主表面上に配置された、磁化の方向が一定である層である。自由層37は、トンネル絶縁膜38の、固定層35と対向する一方の主表面と反対側に位置する他方の主表面上に配置された、磁化の方向が可変である層である。上記下部電極31、固定層35、トンネル絶縁膜38、自由層37、上部電極44の積層方向に交差する方向において、上部電極44の幅は、下部電極31および固定層35の幅よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】書き換え特性の劣化が抑制される半導体装置を提供する。

【解決手段】メモリセル領域RMでは、半導体磁気記憶装置における磁気抵抗素子18は、一方向に延在するディジット線3と、これと略直交する方向に延在するビット線32とが交差する部分に配置される態様で、アレイ状に形成されている。ディジット線3とビット線32は、配線本体となる銅膜3b、31aにクラッド層3a、36aを被覆した配線構造とされる。磁気抵抗素子18の一端側は、非磁性材料から形成されたトップヴィア25aを介してビット線32に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】選択された磁気抵抗素子に書き込み動作等を行う際に、非選択の磁気抵抗素子の誤動作の抑制が図られた半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】 半導体装置は、磁化の向きが可変とされた磁化自由層を含み、引出配線上に形成された磁気記憶素子と、磁気記憶素子の下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能なディジット線50とを備え、ディジット線50は、配線本体部51と、配線本体部51の底面および側面を覆うように設けられ、上方に向けて開口するクラッド層52とを含み、クラッド層52は、配線本体部51の側面を覆うように形成された側壁部52bと、配線本体部51の底面を覆うように形成された底壁部52aとを含み、側壁部52bの厚さW1は、底壁部52aの厚さW2よりも厚く形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の生産性を向上させる。

【解決手段】シリコン基板1を覆う層間絶縁膜ILと、複数のメモリセルとを有する半導体装置であって、複数のメモリセルは、層間絶縁膜IL内に配置された記憶素子部mr1と、記憶素子部mr1に電気的に接続するようにして配置された下部電極BEおよび上部電極TEとを有する。下部電極BEと上部電極TEとは層間絶縁膜IL内において互いに交差するようにして配置され、その交差部に挟まれるようにして記憶素子部mr1が配置されている。記憶素子部mr1は、磁気抵抗メモリ、相変化メモリ、または、抵抗変化メモリからなる。

(もっと読む)

スピンメモリ

【課題】スピン注入書き込み時の電流値が低い磁気抵抗効果素子を提案する。

【解決手段】本発明の例に関わるスピンメモリは、磁化方向が不変の第1強磁性層、磁化方向が可変の第2強磁性層、及び、これらの間の第1非磁性層を有する磁気抵抗効果素子17と、第2強磁性層の磁化困難軸に対して、θ(45°≦θ≦90°)の方向に延び、長手方向の一端で磁気抵抗効果素子17を挟み込む下部電極16及び上部電極18と、下部電極16の長手方向の他端に接続されるスイッチ素子14と、上部電極18の長手方向の他端に接続されるビット線20とを備える。第2強磁性層の磁化反転は、第2強磁性層にスピン偏極した電子を与える書き込み電流を下部電極16と上部電極18との間に流すと共に、下部電極16及び上部電極18に流れるその書き込み電流により発生する磁界を用いて実行する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程を複雑化することなく、配線の信頼性低下を招かない、配線構造を有する半導体装置及びその製造方法を得る。

【解決手段】接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTa/TaN積層バリア層12を介して、NiFe磁性層13をPVD装置のNiFeチャンバを用いたPVD法によって成膜する。次に、同一のPVD装置の同一のNiFeチャンバを用いて、成膜条件を変更することにより、接続孔30及び配線用溝31の底面上及び層間絶縁膜11の表面上におけるNiFe磁性層13を選択的に除去する。さらに、同一のPVD装置のTaチャンバ及びCuチャンバを用いて、接続孔30の底面及び側面上並びに配線用溝31の底面及び側面上にTaバリア層及びCuシード層を順次形成する。

(もっと読む)

1 - 20 / 50

[ Back to top ]