Fターム[4M119GG01]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリセル(ユニット)間レイアウト (125)

Fターム[4M119GG01]に分類される特許

61 - 80 / 125

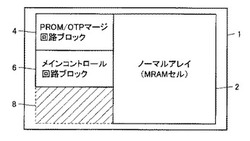

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子の特性バラツキを低減することで、動作マージンを大きくすることが可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、メモリ領域に配置され、かつ抵抗値の変化に応じてデータを記憶し、かつ第1の配線SLに一端が電気的に接続され、第2の配線に他端が電気的に接続された複数の可変抵抗素子23と、メモリ領域に配置され、かつ可変抵抗素子23と同じ材料からなり、かつ電気的に絶縁された複数のダミー素子28とを含む。MTJ素子23及びダミー素子28を合わせた素子アレイは、格子状の密集パターンを有している。すなわち、MTJ積層膜を加工する際のレジストパターンを格子状の密集パターンによって形成する。そして、このレジストパターンを用いてMTJ積層膜を加工することで、MTJ素子23とダミー素子28とを合わせた素子アレイを格子状の密集パターンに配置する。

(もっと読む)

情報保存装置及びその動作方法

【課題】情報保存装置及びその動作方法を提供する。

【解決手段】情報保存装置及びその動作方法に係り、該情報保存装置は、バッファトラック及びこれに連結された複数の保存トラックを含む磁性構造体;磁性構造体に備わった書込み/読取りユニット;バッファトラック、複数の保存トラック及び書込み/読取りユニットにそれぞれ連結された複数のスイッチング素子を含む。該バッファトラックと複数の保存トラックとに連結されたスイッチング素子は、同じ信号ラインに連結されうる。該磁性構造体と書込み/読取りユニットとのうち、少なくとも一つに電流を印加するための回路部がさらに備わりうる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】スピン注入型の磁気ランダムアクセスメモリに関し、より小さいサイズのメモリセル選択トランジスタで効率的な書き込みが可能な磁気ランダムアクセスメモリを提供する。

【解決手段】ビット線24、接続導体層25及びMTJ素子30が形成された層間絶縁膜22上には、層間絶縁膜26が形成されている。層間絶縁膜26には、接続導体層25に接続されたプラグ27と、MTJ素子30に接続されたプラグ28とが埋め込まれている。層間絶縁膜26上には、プラグ27とプラグ28とを電気的に接続する局所内部配線29が形成されている。これにより、MTJ素子30のフリー層側は、プラグ28、局所内部配線29、プラグ27、接続導体層25、プラグ23、接続導体層21、及びプラグ19を介して、n型ドレイン領域16に電気的に接続されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】磁気抵抗変化素子を備えたメモリセルに記憶された2値の情報を適切に読み出すことができる半導体記憶装置等を提供する。

【解決手段】記憶用磁気抵抗変化素子を備えた複数のメモリセルを含むメモリセルアレイ51と、参照用磁気抵抗変化素子を備えた複数の参照セルを含み、参照電流を出力する参照セルアレイ53と、前記参照電流から求められる参照抵抗値と前記記憶用磁気抵抗変化素子の抵抗値とを比較して当該メモリセルに記憶されている情報を判定する判定手段56と、が設けられている。更に、前記参照セルアレイが前記参照電流を出力する際に、前記複数の参照用磁気抵抗変化素子から選択される高抵抗状態の参照用磁気抵抗変化素子及び低抵抗状態の参照用磁気抵抗変化素子を特定する情報並びにこれらの接続関係を示す制御情報を記憶する記憶手段55と、前記制御情報に基づいて前記参照セルアレイの動作を制御する制御手段54と、が設けられている。

(もっと読む)

共に結合された2つ以上の基板から形成された電子デバイス、電子デバイスを備える電子システム、及び、電子デバイスの製造方法

電子デバイスは、第1の基板及び第2の基板を備える。第1の基板は、第1の基板の少なくとも一部を介して相互に少なくとも実質的に平行な複数の導電性トレースを含む回路を備える。複数のボンドパッドは、第1の基板の表面上に配置されるとともに、複数の導電性トレースの少なくとも2つの上に延在する幅を持つ。複数のビアは、少なくともいくつかの導電性トレースの隣接部から複数のボンドパッドまで延在する。第2の基板は、第1の基板に結合されるとともに、複数の導電性バンプを有する第1の基板上の複数のボンドパッドに接続される回路を備える。更に、メモリデバイスと、電子デバイス及びメモリデバイスを形成する関連方法とが開示され、同様に電子システムも開示されている。 (もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の生産性を向上させる。

【解決手段】シリコン基板1を覆う層間絶縁膜ILと、複数のメモリセルとを有する半導体装置であって、複数のメモリセルは、層間絶縁膜IL内に配置された記憶素子部mr1と、記憶素子部mr1に電気的に接続するようにして配置された下部電極BEおよび上部電極TEとを有する。下部電極BEと上部電極TEとは層間絶縁膜IL内において互いに交差するようにして配置され、その交差部に挟まれるようにして記憶素子部mr1が配置されている。記憶素子部mr1は、磁気抵抗メモリ、相変化メモリ、または、抵抗変化メモリからなる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

メモリ素子

【課題】電界によって分極と磁化を誘起し、その強度と方向を制御できるメモリ素子を提供する。

【解決手段】メモリ素子において、マルチフェロイック固体材料1からなる構造を有し、上下の金属電極2,2′に電界を印加するように配置し、上下の金属電極2,2′間に誘起される電荷、磁化を利用する。データの書き込みは、特定の選択されたビット線4とワード線5の間に印加する電圧による電界で分極を発生させることにより実現する。データの読み出しは、保持されている電気分極に起因する電圧強度で0もしくは1を判定すればよい。データの消去は、そのメモリセル3へ印加する電圧の符号を先に印加した電圧と反転させ、一定の強度を与えればよい。一方、分極発生すると同時に磁化6が発生する。この磁化6は磁界7をメモリセル3の外部に及ぼす。このことからメモリセル3の情報に相応した磁界を発生し得るアクティブ型メモリ素子を提供することができる。

(もっと読む)

抵抗変化型メモリデバイス

【課題】準安定状態への遷移確率を減らし、注入電流の広い範囲にわたって安定な磁化反転を実現する、スピントランスファ効果を利用してデータの書き込みを行う抵抗変化型メモリデバイスを提供する。

【解決手段】抵抗変化型のメモリセルMC内に、記憶層磁化53の向きが反転可能な記憶層16を含み接続プラグ31上に形成された磁性層12,14,16を含むトンネル磁気抵抗効果素子1の積層体を有し、積層体の各層の中心を結ぶ線が、当該積層体が形成された接続プラグ31の上面と垂直な方向から斜めに傾いている。

(もっと読む)

複合材の製造方法及び半導体装置の製造方法

【課題】大気中でも安定した複合材を容易に得ることができる複合材の製造方法及び半導体装置の製造方法を提供する。

【解決手段】基体1上に、複数の表面酸化微粒子2を堆積する。表面酸化微粒子2の直径は10nm以下であることが好ましく、例えば0.5nm〜5nm程度である。表面酸化微粒子2は、グラファイト層を形成する際の触媒として機能し得るコバルト等の強磁性体金属微粒子とこの表面を覆う酸化膜から構成されている。次いで、炉内に基体1及び表面酸化微粒子2を挿入し、炉内を高真空にして基体1を510℃程度まで昇温する。この結果、基体1及び表面酸化微粒子2に付着していた異物等が除去される。その後、炉内の雰囲気を炭化水素系ガス雰囲気にする。この結果、表面酸化微粒子2の表面に存在した酸化膜が還元され、更に、強磁性体金属微粒子の表面にグラファイトが析出し、グラファイト被覆微粒子3が強磁性体複合微粒子として得られる。

(もっと読む)

マルチフェロイック電子装置

【課題】 交流磁場で電流を誘起でき、または電気分極の強度と方向を制御できるマルチフェロイック電子装置を提供する。

【解決手段】 マルチフェロイックナノ発電機は、金属電極2に挟まれたマルチフェロイック固体材料1からなる構造を有し、金属電極2に平行に交流磁界5を印加するように配置し、金属電極2間に誘起される電流を利用する。

(もっと読む)

半導体記憶装置

【課題】レイアウト面積が小さな半導体記憶装置を提供する。

【解決手段】このMRAMでは、メモリブロックMB1用のDLドライバ10をトランジスタ20,21で構成し、メモリブロックMB2内のアクセストランジスタ19のサイズを適正化し、空いた領域にドライバトランジスタ21を配置する。また、メモリブロックMB2用のDLドライバ14をトランジスタ22,23で構成し、メモリブロックMB1内のアクセストランジスタ19のサイズを適正化し、空いた領域にドライバトランジスタ23を配置する。したがって、レイアウト面積が小さくなる。

(もっと読む)

対称なSTT−MRAMビットセルデザイン

対称なスピントランスファトルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルおよびSTT−MRAMビットセルアレイが示される。STT−MRAMビットセルは、ポリシリコン層、磁気トンネル接合(MTJ)記憶素子およびボトム電極(BE)プレートを含んでいる。 (もっと読む)

矩形のボトム電極プレートを有するSTT−MRAMビットセル

スピントランスファトルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルが提供される。STT−MRAMは、矩形のボトム電極(BE)プレートおよび矩形のボトム電極(BE)プレート上の記憶素子を含んでいる。矩形のボトム電極(BE)プレートの幅と記憶素子の幅との間の差は、所定の最小間隔条件以上ある。ボトム電極(BE)プレートの幅は、活性層の幅または複数の金属層の幅と実質的に等しい。 (もっと読む)

不揮発性半導体記憶装置

【課題】磁気ランダム・アクセス・メモリの書込に関連する回路のレイアウト面積を低減する。

【解決手段】可変磁気抵抗素子(VR)の磁化容易軸(EX)と直交する方向に書込ビット線(WBL0,WBL1)を配置し、書込データに応じて双方向に書込ビット線に電流を流す。一方、書込ビット線と交差するようにビット線(BL0−BL3)を配置し、書込データの論理値にかかわらず一定方向に電流を流す。書込ビット線へは、セルトランジスタ(CT)の耐圧よりも高い高電圧(VCC)から電流を供給する。

(もっと読む)

抵抗変化型メモリ

【課題】セル面積の増加を抑制しつつ、書き込み電流を増大する。

【解決手段】抵抗変化型メモリは、第1の素子領域10と、第1の素子領域の上方に配置され、第1の方向Xにそれぞれ延在された第1及び第2のビット線BL1,BL2と、第1及び第2のビット線にそれぞれ接続された第1及び第2の抵抗変化素子MTJ1,MTJ2と、第1及び第2の抵抗変化素子の両方に直列接続され、第1の素子領域内に形成され、第1の方向と交差する第2の方向Yに延在された第1のゲート電極G1を有し、第1のゲート電極のゲート幅は第1の素子領域の第2の方向の幅と等しい第1のトランジスタTr1とを具備する。

(もっと読む)

磁気記憶素子及び磁気記憶装置

【課題】フリー層の磁化方向を反転させるのに必要な反転電流を低減しつつ、磁化方向を反転させた場合の抵抗の変化率を大きくした磁気記憶素子および磁気記憶装置を提供する。

【解決手段】スピン偏極した電子により磁化方向を反転させる磁気記憶素子であって、第1ピン層と、第1トンネル絶縁層と、第1フリー層との積層構造を含む第1単位磁気記憶素子と、第2ピン層と、第2トンネル絶縁層と、第2フリー層との積層構造を含む第2単位磁気記憶素子と、第1ピン層と第2ピン層を電気的に接続して、第1単位磁気記憶素子と第2単位磁気記憶素子とを直列に接続する接続電極とを含み、電子の移動方向に垂直な方向の第2単位磁気記憶素子の断面積が、第1単位磁気記憶素子の断面積より大きい。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】隣接するスピン注入型磁気抵抗効果素子に起因したディスターブ現象が発生し難い構成、構造を有する磁気抵抗効果素子を提供する。

【解決手段】磁気抵抗効果素子30は、電流によるスピン注入磁化反転に基づき情報が書き込まれる記録層53が設けられた積層構造体50を備えており、記録層53の外縁部は、絶縁領域170を介して磁気シールド層180によって囲まれており、磁気シールド層180は、記録層53の延在部53Aから構成されている。

(もっと読む)

半導体メモリ

【課題】しきい値電流以上の書き込み電流を用いることができる。

【解決手段】本発明の例に関わる半導体メモリは、第1及び第2のビット線BL1,BL2と、第1及び第2のビット線BL1,BL2と交差する方向に延びる第1のワード線WL1と、第1及び第2の端子を有し、第1の端子が前記第1のビット線BL1に接続される第1のMTJ素子と、第1のワード線WL1に接続される第1のゲート電極と、一端が第2のビット線BL2に接続され、他端が第1のMTJ素子MTJ1の第2の端子と接続される第1の電流経路とを有する第1の選択トランジスタTr11と、ゲート電極と一端が第1のMTJ素子MTJ1の第2の端子に接続される電流経路とをそれぞれ有する第1乃至第3の補助トランジスタTr21,Tr31,Tr41と、を備える。

(もっと読む)

61 - 80 / 125

[ Back to top ]