Fターム[4M119GG01]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリセル(ユニット)間レイアウト (125)

Fターム[4M119GG01]に分類される特許

81 - 100 / 125

半導体記憶装置

【課題】メモリセルに含まれる選択トランジスタのゲート配線のピッチに対する上層の杭打用金属配線ピッチの影響を低減する。

【解決手段】メモリセルアレイ(1)の両側にワード線ドライブ回路(2R,2L)を対向して配置し、各ワード線ドライブ回路には、ワード線ドライバをメモリセル行に対して交互に配置する。メモリセルの選択トランジスタのゲート配線(PGo,PGe)は、各メモリセル行に対応して配置される。杭打用の上層の金属配線(MLo,MLe)は、対向配置されるワード線ドライブ回路からメモリセルアレイの中央部の接続領域(10)まで延在させ、接続領域においてゲート配線に交互に電気的に接続する。金属配線は、ゲート配線の2倍のピッチで対向して配置する。

(もっと読む)

半導体メモリ

【課題】半導体装置のプロセスマージンを向上できる。

【解決手段】本発明の例の半導体メモリは、同一の配線層内に設けられる2つのビット線BL1,BL2と、メモリセルアレイ内に設けられるアクティブ領域AA2と、アクティブ領域AA2と交差する2つのワード線WL1,WL2と、ゲートがワード線WL1,WL2にそれぞれ接続されアクティブ領域AA2上に設けられる第1及び第2のトランジスタTr1,Tr2と、ビット線BL2とトランジスタTr1のソース/ドレインとに接続される第1の抵抗性記憶素子MTJ1と、ビット線BL2とトランジスタTr2のソース/ドレインとに接続される第2の抵抗性記憶素子MTJ2と、ビット線BL1と2つのトランジスタTr1,Tr2の共有ノードに接続され、ワード線WL1,WL2間に配置される配線層M2とを具備し、アクティブ領域AA2はメモリセルアレイの一端から他端まで延在する。

(もっと読む)

多重レベル磁気記憶装置

【課題】記憶容量を高めたメモリ(100)を有する記憶装置を提供する。

【解決手段】データ・ビットはスタック(50)に沿う複数のメモリ位置に垂直に記憶する。各メモリ位置(56,58)は非磁気層(60,64)と切替え可能な磁気層(62,66)とを含む。電流源(102)からスタック内に電流を流して、スピン運動量移動により、各位置の隣の磁気層の間にトルクを発生させて磁化の方向を決めることによりデータ・ビットを記憶する。複数のスタック・メモリ位置は複数のデータ・ビットを記憶することができる。

(もっと読む)

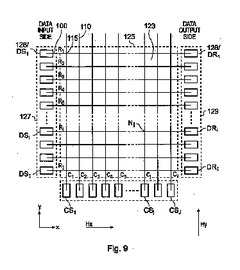

磁気抵抗ランダムアクセスメモリ(MagnetoresistiveRandomAccessMemory:MRAM)ビットセルのアレイ・ストラクチャル・デザイン(arraystructuraldesign)

スピン・トランスファ・トルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルが開示される。前記ビットセルは、第1の面内に形成されたソース線と、第2の面内に形成されたビット線とを含む。ビット線は、前記ソース線の長手方向軸に対して平行である長手方向軸を有し、かつ、前記ソース線は少なくとも前記ビット線の一部にオーバーラップする。  (もっと読む)

(もっと読む)

熱支援書き込みを用いる磁気素子

熱支援磁場書き込みまたは熱支援スピン移動書き込みを用いる磁気素子であって、固定方向の磁化を有する基準磁性層43と、反強磁性層41と交換トラップされた記憶磁性層40であって、記憶層40の磁化方向が、前記部材が反強磁性層41のブロッキング温度より少なくとも高い温度に加熱され得る場合には、変化できる記憶磁性層40と、基準層と記憶層との間に設けられた、絶縁もしくは半導電性層42、または電流狭窄路を有する層と、を各々が含む磁気素子において、磁気素子31がまた、磁性部材を加熱するための少なくとも1つの電気抵抗薄層48を含むことを特徴とする磁気素子。  (もっと読む)

(もっと読む)

三次元六角形マトリックスメモリアレイとその製造方法

不揮発性メモリデバイスは、実質的に六角形のパターンに配置された複数の不揮発性メモリセルを含む。不揮発性メモリセルはピラー形の不揮発性メモリセルであってよく、これは三重または四重露光リソグラフィか自己集合層によりパターニングできる。セルは平行四辺形のサブアレイに配置される。ビット線は60度の角度でワード線と交差する。このメモリデバイスは三次元アレイにできる。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】コストの増加を抑制しつつ、磁化反転をアシストする。

【解決手段】スピン注入型の磁気ランダムアクセスメモリは、固定層11と記録層13と非磁性層12とを有し、固定層及び記録層の磁化は膜面に対して垂直方向を向く磁気抵抗効果素子10aと、磁気抵抗効果素子の一端に接続されたソース線SLaと、磁気抵抗効果素子の他端に電流経路の一端が接続されたトランジスタTraと、トランジスタの電流経路の他端に接続され、ソース線と平行に延在されたビット線BLと、磁気抵抗効果素子及びトランジスタを介してビット線及びソース線間に書き込み電流Iを流し、ビット線を通過した書き込み電流によって発生された磁場の磁気抵抗効果素子に対する印加方向が磁気抵抗効果素子を通過する書き込み電流の方向と反対であるソース/シンカとを具備する。

(もっと読む)

電気的にプログラム可能な抵抗特性を有するクロスポイントメモリ

【課題】外部影響(特に電気的パルス)により電気的抵抗が変化する特性を有する材料を用いた不揮発性メモリの大容量化を可能としたクロスポイントメモリデバイスを提供すること。

【解決手段】下部電極と上部電極とのクロスポイントに対応するビット領域は、互いに交差するように配列された下部電極と上部電極との間に配置されたアクティブ層の一部である。アクティブ層は、電気信号に応答して変化する抵抗性を有し得る材料である。下部電極と上部電極との間を通る電気信号は、ビット領域を通過する。ビット領域では、電気信号に応答して抵抗率を変化させる。

(もっと読む)

分離CPPアシスト書込を行うスピン注入MRAMデバイス

【課題】再生および記録の効率性を高めるスピンRAM構造を提供する。

【解決手段】スピン注入MRAM50は、上部CPPセル80と下部MTJセル60との間に導電性スペーサ70をそれぞれ有する2つのサブセル50を備える。各ビットセルの2つの導電性スペーサ70は、トランジスタにより結合される。トランジスタは、書込ワード線により制御される。各ビットセルの2つのCPPセル80は異なる抵抗状態を有し、各サブセル80のMTJセル60とCPPセル80とは異なる抵抗状態を有する。MTJフリー層67は、CPPフリー層が発揮する大きな反磁場に起因して、CPPフリー層の反転に応じて回転する。同一のビットセルの内部の第2のMTJをリファレンスとすることにより、高速で信頼性の高い再生動作を可能とする改善された回路構造が開示される。

(もっと読む)

磁気記録装置

【課題】比較的簡素な構成により、データの読み取り時間、好ましくは更にデータの書き込み時間を大幅に短縮させてデータ転送速度を向上させ、しかもデータの蓄積領域を十分に確保し、記録装置としての使用効率を向上させる磁気記録装置を提供する。

【解決手段】読取素子2及び書込素子3をそれぞれ2つずつ磁性細線1のデータ蓄積領域1a上に配設し(読取素子2a,2b及び書込素子3a,3bと図示する。)、データ蓄積領域1aを各分割領域1a1,1a2に分割する。このように各2つの読取素子2及び書込素子3を配設した場合、素子群数n=2であることから、読取素子2及び書込素子3を各1つずつ配設する場合に比べて、データ読み取り時間及び書き込み時間はそれぞれ半分に短縮される。同様に、磁性細線1で必要とされるバッファ領域1bの占める割合は1/3(≒33%)(データ蓄積領域1aの占める割合は2/3(≒67%))となる。

(もっと読む)

積層されたNAND型抵抗性メモリセルストリングを含む不揮発性メモリ素子及びその製造方法

【課題】積層されたNAND型抵抗性メモリセルストリングを含む不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】NAND型抵抗性メモリセルストリングSTR1,STR2は、ビットラインBL及びビットラインBLに直列接続された複数個の抵抗性メモリセルCL1,CL2,CL3を含み、複数個の抵抗性メモリセルCL1,CL2,CL3のそれぞれは、第1ノードN1、第2ノードN2及び第3ノードN3、第1ノードN1と第2ノードN2との間に接続されたヒータH1、H2、H3、第2ノードN2と第3ノードN3との間に接続された可変抵抗体R1、R2、R3、第1ノードN1に接続された第1端子及び第3ノードN3に接続された第2端子を有するスイッチング素子SW1、SW2、SW3とを含む。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】 磁化状態がより安定している参照セルを有する磁気ランダムアクセスメモリを提供する。

【解決手段】 磁気ランダムアクセスメモリは、半導体からなる基板を含む。第1磁気抵抗素子MRaは、基板表面の上方に設けられ、磁気抵抗効果によって抵抗値の異なる2つの定常状態を取り、基板表面に投影された形状が第1方向に沿った第1長さと第2方向に沿った前記第1長さ以上の長さの第2長さとを有する。第2長さの第1長さに対する比は第1値である。第2磁気抵抗効果素子MRbは、基板表面の上方に設けられ、第1磁気抵抗効果素子の抵抗状態を判定するために用いられ、磁気抵抗効果によって抵抗値の異なる2つの定常状態を取り、基板表面に投影された形状が第3方向に沿った第3長さと第4方向に沿った第3長さ以上の長さの第4長さとを有する。第4長さの第3長さに対する比は第1値より大きい。

(もっと読む)

磁気半導体メモリ

【課題】高速動作が可能で、データ保持の信頼性が高い磁気半導体メモリを提供する。

【解決手段】本発明の磁気半導体メモリは、MTJ素子2を含むメモリセル1と、Y軸方向に延設された配線11、12とを具備する。配線11の中心線11aは、MTJ素子2から+X方向にずれており、且つ、配線12の中心線12aは、MTJ素子2から前記−X方向にずれている。

(もっと読む)

磁気抵抗ラム

【課題】ワードラインとP−Nダイオードとの間にMTJ(Magnetic Tunnel Junction)を結合して2つ以上のデータを記憶させ、構造が簡単でセルサイズが小さい磁気抵抗ラム(MRAM)用セルを具現する。

【解決手段】半導体基板にドーピングされたN+領域と、前記N+領域のライン上にドーピングされたP型の不純物領域でなるP−Nダイオード、前記P型の不純物領域の上に積層されたバリヤー導電層、前記バリヤー導電層の上部に積層されたMTJ(Magnetic Tunnel Junction)、及び前記MTJの上部に積層されたワードライン、を備えるMRAMセルを含み、前記ワードラインに印加される電圧の大きさに従って前記MTJに流れる電流を制御し、前記MRAMセルにデータを書き込み、読み出すことを特徴とする。

【選択図】図3  (もっと読む)

(もっと読む)

データストレージデバイスおよびデータストレージ方法

各データ担持ナノワイヤが、そのナノワイヤの全長に沿って複数の交差するナノワイヤを有して、磁壁ピン留めサイトを構成する交差接合部を形成する。データは、交差するナノワイヤとの整列と反整列の間で交番する磁界の作用の下で磁区を動かすことによって、各データ担持ナノワイヤを通って送られる。データは、上向きキラリティ横磁壁および下向きキラリティ横磁壁が、0および1を符号化するのに使用されて、磁壁のキラリティに符号化される。データは、事前定義されたキラリティの磁壁を有する磁区を核形成することができる適切な核形成磁界発生器を使用して、各ナノワイヤの中にクロック制御されて入れられる。データは、このキラリティを検知する適切な磁界センサを使用して、各ナノワイヤからクロック制御されて出される。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】磁気ランダムアクセスメモリの大容量化と製法の提供。

【解決手段】第1の固定層Ps1と第1の記録層Fsと前記第1の固定層及び前記第1の記録層の間に設けられた第1の非磁性層Ts1とを有し、前記第1の固定層及び前記第1の記録層の電流の向きに応じて磁化方向が平行状態又は反平行状態となる1重トンネル接合素子MTJsと、第2及び第3の固定層Pw1,Pw2と第2の記録層Fwと前記第2の固定層及び前記第2の記録層の間に設けられた第2の非磁性層Tw1と前記第3の固定層及び前記第2の記録層の間に設けられた第3の非磁性層Tw2とを有し、前記第2の固定層及び前記第2の記録層の間に流す電流の向きに応じて前記第2の固定層及び前記第2の記録層の前記磁化方向が平行状態又は反平行状態となる2重トンネル接合素子MTJwと、互いに並列接続された前記1重トンネル接合素子及び前記2重トンネル接合素子を有するメモリセルMC。

(もっと読む)

高密度の平面磁壁メモリ装置およびその形成方法

【課題】より費用対効果の高い製造環境で、実用的な磁壁メモリ構造を製造すること。

【解決手段】書き込み/読み取り機能を備えた磁壁メモリ装置は、内部に複数の磁区を有する強磁性材料から形成された伸長トラックをそれぞれが備える、複数の共面シフト・レジスタ構造であって、さらにこのシフト・レジスタ構造が磁壁の配置を容易にするために内部に複数の不連続部を有する、複数の共面シフト・レジスタ構造と、それぞれのシフト・レジスタ構造に関連付けられた磁気読み取り要素と、それぞれのシフト・レジスタ構造に関連付けられた磁気書き込み要素であって、さらにこの磁気書き込み要素がそれぞれの共面シフト・レジスタ構造の縦軸とほぼ直交する縦軸を有する単一の書き込みワイヤを備える、磁気書き込み要素と、を含む。

(もっと読む)

磁気ランダムアクセスメモリおよびこれを備えた記録装置

【課題】製造が容易でありマルチレベルの記録状態を実現できる磁気ランダムアクセスメモリを提供する。

【解決手段】磁気ランダムアクセスメモリ2は、セル10の磁気抵抗素子領域20の同一平面内に、磁気抵抗素子30a,30bを備え、磁気抵抗素子30a,30bは、形状磁気異方性が異なるために、外部磁界によって磁化が反転するときに外部磁界の大きさがそれぞれ異なり、磁気抵抗素子30a,30bの一方の磁化が反転することによって、セル10中において生成される磁化状態に対して、セルの高抵抗状態と低抵抗状態の中間状態を割り当てたことを特徴とする。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】セル面積を縮小する。

【解決手段】磁気ランダムアクセスメモリは、側面と上面とを有する段差部が形成された半導体基板11と、段差部の側面上にゲート絶縁膜20を介して形成されたゲート電極Gと、段差部の上面内に形成されたドレイン拡散層24と、ドレイン拡散層より下方の半導体基板内にドレイン拡散層と離間して形成されたソース拡散層18と、ドレイン拡散層に接続され、磁化方向が固定された固定層31と磁化方向が反転可能な記録層33と固定層及び記録層の間に設けられた非磁性層32とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の磁化方向が平行状態又は反平行状態となる磁気抵抗効果素子MTJと、磁気抵抗効果素子に接続されたビット線BLを具備する。

(もっと読む)

磁気抵抗効果素子及び磁気メモリ装置

【課題】磁壁移動現象を利用した磁気抵抗効果素子に関し、熱揺らぎに対する安定性を低下することなく、磁壁の移動速度を向上しうる磁気抵抗効果素子を提供する。

【解決手段】 磁化方向が固定された固定磁化層36と、固定磁化層36上に形成された非磁性層40と、強磁性層42と、強磁性層42上に形成された非磁性金属層44と、非磁性金属層44上に形成された強磁性層46との積層体よりなる自由磁化層48であって、複数の磁化記録領域64を有し、磁化記録領域64のそれぞれにおいて、強磁性層42の磁化と強磁性層46の磁化とが互いに反平行に結合しており、一の磁化記録領域64が、非磁性層40を介して固定磁化層36と対向している自由磁化層48とを有する。

(もっと読む)

81 - 100 / 125

[ Back to top ]