Fターム[4M119GG01]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリセル(ユニット)間レイアウト (125)

Fターム[4M119GG01]に分類される特許

21 - 40 / 125

記憶素子、記憶装置

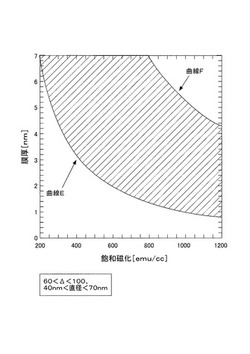

【課題】スピントルク型磁気メモリにおいて、熱安定性及び反転電流のバラツキを抑制する。

【解決手段】上記記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、上記記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。この構成において、記憶層の飽和磁化をMs(emu/cc)、上記記憶層の膜厚をt(nm)としたときに、記憶層の膜厚tは、(1489/Ms)−0.593<t<(6820/Ms)−1.55を満たすようにする。

(もっと読む)

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、異方性エネルギーを大きくし、微細化しても十分な熱揺らぎ耐性を有するようにする。

【解決手段】記憶素子は、膜面に対して垂直な磁化を有し、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる、膜面に対して垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とにより、MTJ構造を持つ。これに加え、記憶層に隣接する、Cr、Ru、W、Si、Mnの少なくとも一つからなる保磁力強化層と、保磁力強化層に隣接する酸化物によるスピンバリア層を設ける。

(もっと読む)

半導体記憶装置

【課題】セルトランジスタの電流駆動能力の劣化を抑制し、メモリセルごとの信号のばらつきを抑制し、かつ、微細化された半導体記憶装置を提供する。

【解決手段】メモリは、MTJを備える。アクティブエリアは、セルトランジスタごとに分離されており、セルトランジスタのゲートの延伸方向に対してほぼ直交する第1の方向に延伸している。アクティブエリアは、第1の方向に配列されてアクティブエリア列を構成している。第2の方向に隣接する2つのアクティブエリア列は、第1の方向に半ピッチずつずれて配置されている。アクティブエリアの表面上方から見たときに、MTJは各アクティブエリアの一端に重複するように配置されている。第1および第2の配線は、互いに隣接するアクティブエリア列のMTJに交互に重複するように第1および第2の方向に対して傾斜する方向に折り返しながら延伸している。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

半導体記憶装置

【課題】MTJ素子の形状およびサイズのばらつきを抑制し、かつ、MTJ素子を製造し易い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数の磁気トンネル接合素子は、半導体基板の上方に形成され、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能である。複数のセルトランジスタは、半導体基板に形成され、磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となる。複数のゲート電極は、セルトランジスタに含まれ、セルトランジスタの導通状態を制御する。複数のアクティブエリアは、セルトランジスタが形成され、前記ゲート電極に対して(90−atan(1/3))の角度で交差する方向に延伸している。

(もっと読む)

記憶素子及び記憶装置

【課題】書込電流を増大させることなく、高い保持力を有し熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層と、記憶層に隣接し中間層と反対側に設けられるキャップ層と、キャップ層に隣接し記憶層と反対側に設けられる金属キャップ層を有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行う。そして中間層とキャップ層は酸化物であり、金属キャップ層はPdもしくはPtで構成されているものとする。

(もっと読む)

磁気メモリ装置のためのライトドライバー回路、磁気メモリ装置及びそのレイアウト構造

【課題】本発明の技術的な課題は、共通ソースラインを含む磁気メモリ装置に対してビットラインへ記録電流を供給することができるライトドライバー回路を提供すること、集積度が向上された磁気メモリ装置を提供すること、及び、共通ソースラインを有する磁気メモリ装置のレイアウト構造を提供することにある。

【解決手段】ビットラインとソースラインとの間に接続され、前記ビットライン方向に隣接する一対の磁気メモリセルが前記ソースラインを共有する複数の磁気メモリセルよりなるメモリセルアレイを有する磁気メモリ装置のためのライトドライバー回路であり、正の記録電圧の供給端子と副の記録電圧の供給端子との間に接続されて、ライトイネーブル信号及びデータ信号によって前記正の記録電圧または前記副の記録電圧による電流を前記ビットラインに選択的に供給するスイチング部を備える磁気メモリ装置を提供する。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

半導体記憶装置

【課題】記憶素子の配置を均等にし、微細化および大容量化を実現可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と、複数のワード線と、互いに隣接する2本の前記ビット線間に直列に接続された記憶素子およびセルトランジスタを含む複数のメモリセルとを備える。2本のビット線間に接続された複数のメモリセルのそれぞれのセルトランジスタのゲートは、互いに異なるワード線に接続されている。互いに隣接する複数のメモリセルの複数の前記記憶素子および複数のセルトランジスタは、交互に直列に接続される。

(もっと読む)

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

半導体装置

【課題】メモリセルの平面視における面積を増加せずに、磁気抵抗素子の情報の読み書きに用いる電流値を低減しながら、読み書きエラーや磁気抵抗素子間の短絡が抑制された集積回路を有する半導体装置を提供する。

【解決手段】半導体基板の主表面上に配置された、電流の流れる向きに応じて磁化状態を変化させることが可能な、スピントルク書き込み方式の面内磁化型の磁気抵抗素子MRDと、磁気抵抗素子MRDと電気的に接続され、主表面に沿った方向に向けて延びる第1配線BLとを備える。上記磁気抵抗素子MRDは平面視におけるアスペクト比が1以外の値である。上記磁気抵抗素子MRDとスイッチング素子とが電気的に接続されたメモリセルMCが複数並んだメモリセル領域において、平面視における磁気抵抗素子MRDの長手方向に関して、隣接する複数の磁気抵抗素子MRDが、上記長手方向に沿って延在する同一直線上に乗らないように配置される。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

磁気異方性物質の自由磁性層を含むストレージノード、これを含む磁気メモリ素子及びその製造方法

【課題】磁気異方性物質の自由層を含むストレージノードと、これを含む磁気メモリ素子及びこれらの製造方法を提供する。

【解決手段】下部磁性層と、下部磁性層上に形成されたトンネルバリアと、トンネルバリア上に形成され、スピン電流により磁化方向がスイッチングされる自由層と、を含み、自由層は水平または垂直磁気異方性物質層を含み、自由層下に形成された少なくとも一つの物質層を包むキャップ構造を持つ磁気メモリ素子のストレージノード。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

縦型トランジスタSTRAMアレイ

【課題】複数の不揮発性可変抵抗メモリセルを含む縦型のメモリアレイを提供する。

【解決手段】方法は、半導体ウェハから垂直に伸延する複数のピラー構造を有する半導体ウェハを提供するステップを含む。導電相互接続素子が、少なくとも選択された縦型ピラートランジスタ上に堆積されるとともに、不揮発性可変抵抗メモリセルが、導電相互接続素子上に堆積されて、縦型トランジスタメモリアレイを形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

21 - 40 / 125

[ Back to top ]