Fターム[4M119GG01]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリセル(ユニット)間レイアウト (125)

Fターム[4M119GG01]に分類される特許

41 - 60 / 125

半導体装置

【課題】 スピン注入磁化反転を用いたメモリにおいて、高速動作時の低電流書き換え動作を実現し、メモリセル毎のばらつきを抑え、読み出しディスターブを抑える。

【解決手段】 書き換え前に弱いパルスを与えてスピンの状態を不安定にし、書き換え電流を低減する。書き換え電流がパルス幅により非線形に大きくなる領域で読み出しを行い

、ディスターブを抑える。更に、ビット線電荷で注入スピン量を一定とした駆動方法によりばらつきを抑える。

(もっと読む)

記憶素子及び記憶装置

【課題】書き込み電流を増大させることなく、熱安定性を改善できる記憶素子の実現。

【解決手段】

記憶素子は、情報に対応して磁化の向きが変化される記憶層17と、記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層と磁化固定層の間に設けられる非磁性体による中間層16とを有する。そして積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して情報の記録が行われる。ここで記憶層は、Fe、Coの少なくとも一方を含有する合金領域を含む。さらに記憶層は、その磁化反転過程で受ける実効的な反磁界の大きさが、上記記憶層の飽和磁化量よりも小さいものとされている。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

記憶素子、記憶素子の製造方法、及び、メモリ

【課題】消費電力化が可能な記憶素子を提供する。

【解決手段】積層方向に電流を流して、スピン偏極した電子を注入することにより、記憶層16の磁化M1の向きが変化して、記憶層16に対して情報の記憶が行われる記憶素子3を構成する。この記憶素子3は、情報を磁性体の磁化状態により保持する記憶層16と、記憶層16に対してトンネルバリア層15を介して設けられている磁化固定層14とを備える。そして、トンネルバリア層15は、厚さが0.1nm以上0.6nm以下であり、且つ、界面ラフネスが0.5nm未満である。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

抵抗変化メモリ

【課題】メモリセルアレイの面積を縮小する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のビット線BLと、第2の方向に延在する複数のワード線WLと、複数のメモリセルMCを備えたメモリセルアレイ11とを含む。各メモリセルMCは、可変抵抗素子21と選択トランジスタ22とを有し、可変抵抗素子21の第1の端子は第1のビット線に接続され、可変抵抗素子21の第2の端子は選択トランジスタ22のドレインに接続され、選択トランジスタ22のソースは第2のビット線に接続され、選択トランジスタ22のゲートはワード線に接続される。第1の方向に順に並んだ第1乃至第4の可変抵抗素子のレイアウトにおいて、第1及び第2の可変抵抗素子は1本のワード線を挟み、第2及び第3の可変抵抗素子は2本のワード線を挟み、第3及び第4の可変抵抗素子は1本のワード線を挟む。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

薄膜磁性体記憶装置

【課題】書込まれる記憶データのレベルに依存せず磁気特性が対称な磁性体メモリセルを有する薄膜磁性体記憶装置を提供する。

【解決手段】トンネル磁気抵抗素子中の自由磁化層においては、静磁性結合に起因する固定磁化層との間の結合磁界ΔHpが、磁界容易軸(EA)に沿った方向に作用している。データ書込磁界H(WWL)は、自由磁化層の磁化困難軸(HA)と完全に平行に印加されるのではではなく、磁化困難軸HAとの間に所定角度αを成すように印加される。これにより、H(WWL)の磁化容易軸(EA)方向に沿った成分によって、一様な結合磁界ΔHpが相殺される。

(もっと読む)

半導体記憶装置

【課題】活性領域の接触面積を増大でき、コンタクト抵抗を低減可能な半導体記憶装置を提供する。

【解決手段】フィン状の活性領域13は、半導体基板11内に設けられ、第1の側面、前記第1の側面に平行する第2の側面、及び前記第1、第2の側面を繋ぐ上面を有する。ワード線の一部としてのゲート電極14は、活性領域に形成された溝17内及び溝を跨いで形成され、活性領域と絶縁されている。シリサイド層16は、ゲート電極の両側の活性領域に位置し、ソース、ドレイン領域としての活性領域の少なくとも第1の側面に形成されている。少なくとも記憶素子21を接続するためのコンタクト15は、シリサイド層に接続されている。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

情報記憶素子及びその駆動方法

【課題】高い記録密度を実現することができる情報記憶素子を提供する。

【解決手段】連続して形成された導電性の第1の磁性体を含むワード電極1と、第1の磁性体に接して形成された非磁性膜と、第1の磁性体に対して、非磁性膜5を介して接続された第2の磁性体とを含む。そして、ワード電極1の両端部に配置され、ワード電極1の端部の磁化の方向を設定するための磁化設定機構2と、第2の磁性体の保磁力を低減させるための保磁力低減機構と、ワード電極1と交差するように連続して形成された導電性のビット電極3を含む情報記憶素子を構成する。ワード電極1は、第1の磁性体を兼ねていてもよい。ビット電極3は、保磁力低減機構や第2の磁性体を兼ねていてもよい。

(もっと読む)

半導体記憶装置

【課題】2つの選択トランジスタと1つの抵抗性記憶素子から成るメモリセルのレイアウト面積を縮小する。

【解決手段】半導体記憶装置は、それぞれが第1および第2のビット線から成り、且つカラム方向に延びる複数のビット線対と、各ビット線対に接続され、且つ複数のメモリセルから成るメモリセル群とを含む。各メモリセルは、第1のトランジスタT1、第2のトランジスタT2および抵抗性記憶素子10から成る。ロウ方向に隣接する2つのビット線対は、第1のビット線同士が共通接続され、もしくは第2のビット線同士が共通接続されて第1のカラムユニットを構成する。少なくとも片側の端部に配置される第1のビット線もしくは第2のビット線は、それと下層との接続部分よりも、第1のカラムユニットの中央寄りに配置される。

(もっと読む)

スピン移動トルクランダムアクセスメモリのための階層状データ経路を提供する方法およびシステム

磁気メモリを提供する方法およびシステムについて記載する。本方法およびシステムは、メモリアレイタイル(MAT)、中間回路要素、グローバルビット線、グローバルワード線、およびグローバル回路要素を提供することを含む。各MATは、磁気記憶セル、ビット線、およびワード線を含む。磁気記憶セルはそれぞれ、少なくとも1つの磁気素子および少なくとも1つの選択デバイスを含む。磁気素子は、磁気素子を通して駆動される書込み電流を使ってプログラム可能である。ビット線およびワード線は、磁気記憶セルに対応する。中間回路要素は、MAT内の読取りおよび書込み動作を制御する。各グローバルビット線は、複数のMATの第1の部分に対応する。各グローバルワード線は、MATの第2の部分に対応する。グローバル回路要素は、読取りおよび書込み動作のために、グローバルビット線の一部およびグローバルワード線の一部を選択し駆動する。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリを製造するシステムおよび方法

磁気ランダムアクセスメモリを製造するシステムおよび方法が開示される。特定の一実施形態では、磁気トンネル接合メモリシステムを作製する方法は、金属層の一部分を、ほぼ直線の部分を有する無分岐のソースラインの中に形成するステップを含む。この方法はまた、ソースラインをほぼ直線の部分で、第1のビアを使用して第1のトランジスタに結合するステップを含む。第1のトランジスタは、ソースラインから受け取った第1の電流を第1の磁気トンネル接合デバイスに供給するように構成される。この方法は、ソースラインを、第2のビアを使用して第2のトランジスタに結合するステップを含み、第2のトランジスタは、ソースラインから受け取った第2の電流を第2の磁気トンネル接合デバイスに供給するように構成される。  (もっと読む)

(もっと読む)

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

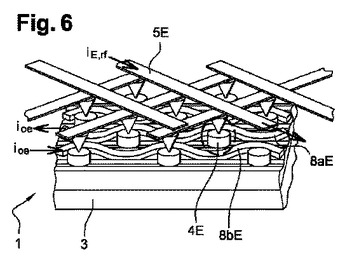

磁気渦記憶装置

本発明は、渦状態の平面磁気セル(4)のネットワークを含む磁気記憶装置(1)であって、各セルの渦コアが、反対方向でありかつセル(4)面に垂直な第1と第2の平衡位置のいずれかの磁化を有し、2つの位置のそれぞれが2進情報を表す、磁気記憶装置(1)に関する。装置(1)は、セルに格納される2進情報を書き込む手段(5、8a、8b、3)であって、各セル(4)の近傍で前記セル(4)面にほぼ垂直な第1のバイアス静磁場と前記セル(4)にほぼ平行な直線偏波無線周波数磁場とを選択的に印加する手段を含む書き込み手段(5、8a、8b、3)を含む。説明の装置はまた、点接触(7)により渦コアの周囲の領域を介し電流線を導くことにより、2つの交差する電極(6)と(9)間の選択的輸送測定を使用して、好ましくは共振的に極性を読み取る手段を含む。  (もっと読む)

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

41 - 60 / 125

[ Back to top ]