Fターム[4M119GG03]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリブロック,チップレベルレイアウト (37)

Fターム[4M119GG03]に分類される特許

1 - 20 / 37

半導体記憶装置

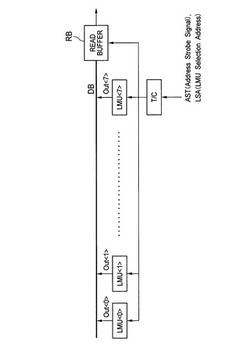

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

垂直磁化磁気抵抗効果素子及び磁気メモリ

【課題】垂直磁気異方性を有する強磁性材料を用いて作製した磁気抵抗効果素子において、ビット情報に対応する磁化の平行状態及び反平行状態の熱安定性が不均衡になり、保存している情報により記録保持時間が異なる状態を改善する。

【解決手段】磁気抵抗効果素子を構成する参照層106と記録層107の面積を異ならせることにより、保存している情報に応じた記録保持時間の差を補正する。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

半導体装置

【課題】メモリセルの平面視における面積を増加せずに、磁気抵抗素子の情報の読み書きに用いる電流値を低減しながら、読み書きエラーや磁気抵抗素子間の短絡が抑制された集積回路を有する半導体装置を提供する。

【解決手段】半導体基板の主表面上に配置された、電流の流れる向きに応じて磁化状態を変化させることが可能な、スピントルク書き込み方式の面内磁化型の磁気抵抗素子MRDと、磁気抵抗素子MRDと電気的に接続され、主表面に沿った方向に向けて延びる第1配線BLとを備える。上記磁気抵抗素子MRDは平面視におけるアスペクト比が1以外の値である。上記磁気抵抗素子MRDとスイッチング素子とが電気的に接続されたメモリセルMCが複数並んだメモリセル領域において、平面視における磁気抵抗素子MRDの長手方向に関して、隣接する複数の磁気抵抗素子MRDが、上記長手方向に沿って延在する同一直線上に乗らないように配置される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】一端がビット線に接続された磁気抵抗素子1と、一端が磁気抵抗素子1の他端に接続され、ゲートがワード線に接続され、他端がソース線に接続された選択トランジスタ2、3とで構成されたメモリセル5よりなるスピン注入方式の磁気ランダムアクセスメモリにおいて、設計工数や製造コストが増大せず、特に小容量サイズのメモリではチップ面積の増加を最小限に抑え、MTJ素子に抵抗状態を変化させるのに充分な電流をながせる磁気ランダムアクセスメモリを提供する。

【解決手段】選択トランジスタがNチャンネルMOSトランジスタ2とPチャンネルMOSトランジスタ3とを並列接続され、ゲートにそれぞれワード線と反転ワード線とが接続された構成であることを特徴とする。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

記憶装置

【課題】書き込み可能回数を増加させることを可能にする、記憶装置を提供する。

【解決手段】磁性体の磁化状態により情報を記憶する記憶層と、この記憶層に対してトンネル絶縁層を介して配置された、磁化の向きが固定された磁化固定層とを含み、記憶層及び磁化固定層の積層方向に書き込み電流を流すことにより、記憶層の磁化の向きが変化して、記憶層に情報が記憶される記憶素子2と、この記憶素子2がアレイ状に配置されて構成され、かつ、複数のセルブロック5a,5bに分割され、セルブロック5a,5b毎に記憶素子2の記憶層の熱安定性が異なる値を持つ、セルアレイ5とを含む記憶装置を構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

垂直ナノワイヤを備える情報保存装置

【課題】情報保存装置を提供する。

【解決手段】基板、基板上に垂直に配列された複数のナノワイヤを備え、複数のナノワイヤそれぞれは、情報を保存するための複数のドメインを有するメモリセルアレイ部、基板上に形成され、複数のナノワイヤのうち少なくとも一つを選択するナノワイヤ選択部、基板上に形成され、複数のナノワイヤのうち少なくとも一つに対してドメイン移動動作を制御するドメイン移動制御部、及び基板上に形成され、複数のナノワイヤのうち少なくとも一つに対する読み取り動作及び書き込み動作のうち少なくとも一つを制御する読み取り/書き込み制御部を備えるメモリセルである。

(もっと読む)

半導体集積回路装置および磁気メモリ装置

【課題】正確に書込データを選択メモリセルに書込むことのできる磁気メモリ装置を提供する。

【解決手段】メモリセルに書込み電流を伝達する書込電流線(BL0、BL1)と平行にかつ異なる配線層に、制御信号を転送する分割構造の制御信号線(210l、211a

、211b)を配置する。電流ドライブ回路が各書込み電流線に対応して配置されて、制御信号線上の制御信号と書込データとに従って対応の書込電流線に電流を流す。

(もっと読む)

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

1 - 20 / 37

[ Back to top ]