Fターム[5B005JJ11]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912) | 高速化 (1,154)

Fターム[5B005JJ11]の下位に属するFターム

W/R動作の高速化 (909)

Fターム[5B005JJ11]に分類される特許

161 - 180 / 245

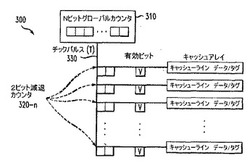

キャッシュメモリにおける漏洩電力の低減方法及び装置

【課題】キャッシュメモリにおける漏洩電力を低減する方法及び装置を提供する。

【解決手段】キャッシュメモリ300は、各キャッシュラインと関連する2ビット飽和カウンタ320−nと、Nビットグローバルカウンタ310を含む。さらに、各キャッシュラインは、主メモリの特定のブロックがキャッシュラインに現在格納されていることを示すタグと、格納されているデータが有効か否かを示す有効ビットとを含む。カウンタ320における状態遷移を最小にすることにより動作電力消費を最小にするために、いつも1ビットだけが状態変化するようにグレイコーディングを用いる。さらに、カウンタ320を簡単にし、トランジスタカウントを最小にするために、カウンタ320は、非同期的に実行することができる。

(もっと読む)

計算機システム

【課題】ストレージ仮想化技術を適用した計算機システムにおいて、計算機システムの構成変更に伴う論理ユニット単位でのデータ移動を、ストレージシステムの性能低下を抑制しつつ、可能とする。

【解決手段】移動先ストレージ130aは、移動元論理ユニット201aを仮想化するための拡張デバイス206cを作成する。ホスト計算機100は、移動先論理ユニット201b→移動先ストレージ130b→移動元ストレージ130a→外部ボリューム301のアクセス経路を通じて外部ボリューム301にアクセスする。移動元ストレージ130aのディスクキャッシュに蓄積されているダーティデータを全て外部ボリューム301にデステージしたならば、外部ボリューム301を仮想化するための拡張デバイス206bを移動先論理ユニット201bにマッピングする。

(もっと読む)

データ処理装置、データ取得方法およびデータ表示方法

【課題】キャッシュメモリを有するプロセッサにおいて、プログラムの実行を中断させることなく、外部からキャッシュメモリの内容を読み出すことを可能にする。

【解決手段】アドレス情報保持手段4は、データ転送手段3により第1の記憶手段1から第2の記憶手段5に転送されたデータのアドレス情報Aを保持する。組み合わせ判定手段8は、第1の出力手段6のアドレス情報Aの出力を意味する信号G1と、第2の出力手段7のデータ出力を意味する信号G2との間にアドレス情報変化信号Hが通知されなかった場合にデータの有効性を有効と判定し、データ有効情報Yを生成してデータ有効情報保持手段9に保持させる。データ取得手段11は、第1の出力手段6からのアドレス情報Aとデータ有効情報保持手段9からのデータ有効情報Yにより第2の出力手段7からのデータD′を判定する。異常であれば、読み出したデータを破棄する。

(もっと読む)

アドレス変換装置

【課題】 ページ・フォールトの発生を抑制し、パフォーマンスを改善したアドレス変換装置を実現する。

【解決手段】 CPUから提供される論理アドレスを、変換テーブルにより前記CPUの主メモリの物理アドレスに変換するアドレス変換装置において、

前記主メモリのデータ領域内の特定領域に専用にアクセスするための専用エントリーを前記変換テーブルに固定配置する。

(もっと読む)

キャッシュメモリ装置及びそれに用いるキャッシュメモリ制御方法並びにそのプログラム

【課題】 フェッチ処理中もキャッシュメモリをブロックすることなく、複数のアクセス要求を低いハードウェア・コストで処理可能なキャッシュメモリ装置を提供する。

【解決手段】 キャッシュメモリ1を制御するキャッシュメモリ制御部2は、ミス情報保持テーブル21の各エントリに、キャッシュミスとなった同一メモリブロックへのフェッチ要求情報を複数保持している。キャッシュメモリ1の各エントリにはフェッチ処理中であるかどうかを示すフェッチフラグと、ミス情報保持テーブル21のエントリを特定する情報とを保持している。キャッシュメモリ制御部2は、これらの情報を基に、フェッチ処理中もキャッシュメモリ1をブロックすることなく、複数のアクセス要求を処理する。

(もっと読む)

キャッシュメモリ制御装置、方法及びプログラム並びにディスクアレイ装置

【課題】 キャッシュメモリの初期化処理を不要とし、即座にキャッシュメモリへのリード転送又はライト転送を開始可能とする。

【解決手段】 管理テーブル16は、実装されたキャッシュメモリのアドレス空間をDRAMのバースト長で分割したバーストアドレス空間と、そのバーストアドレス空間単位でDRAMデータの初期化処理の完了又は未完了を示す完了フラグとを管理する。テーブル制御手段15は、転送アドレス保持手段11で示される転送アドレスから管理テーブル15を索引し、転送アドレスに対応したバーストアドレス空間及びその完了フラグの読み出し制御を行う。バースト制御手段18は、管理テーブル16から読み出した完了フラグと、転送アドレス保持手段11、転送レングス保持手段12及び転送コマンド保持手段13で保持されている転送要求との各情報を元に、DRAMアクセス時のアドレスやデータへの変換又は生成を指示する。

(もっと読む)

プロセッサおよびプロセッサ制御方法

【課題】メモリ領域の不整合の場合の原因解析の容易化および処理速度の向上を、簡単な回路構成で実現するプロセッサを提供すること。

【解決手段】プロセッサ100は、CPUコア101のブレークポイントに定められたアドレスと、CPUコア101がアクセスするデータキャッシュ102のアドレスとの一致判定を比較器104でおこなう。また、データキャッシュ102は、アクセスによるキャッシュヒット/ミスの検出結果を表すキャッシュヒット信号を出力する。また、AND回路106は、比較器104の一致判定信号と、データキャッシュ102のキャッシュヒット信号とに基づいてCPUコア101にデータブレーク信号を出力し、ブレークを実行させる。

(もっと読む)

動作のスヌーピングに応答して無効コヒーレンシー状態を更新するデータ処理システム、キャッシュ・システム、および方法

【課題】改良されたキャッシュ・コヒーレント・データ処理システム、キャッシュ・システム、およびキャッシュ・コヒーレント・データ処理システムにおけるデータ処理方法を提供する。

【解決手段】アドレス・タグが有効であることと、記憶位置が有効データを含まないこととを示す第1のデータ無効コヒーレンシー状態に設定される。アドレス・タグに一致しており、かつ排他的アクセス動作を開始した要求元の相対的ドメイン・ロケーションを示す目標アドレスを指定する排他的アクセス要求のスヌーピングに応答して、アドレス・タグが有効であることと、記憶位置が有効データを含まないことと、要求元の相対的ロケーションに基づく排他的アクセス動作が無事完了した時に、アドレス・タグと関連する目標メモリ・ブロックが、第1のコヒーレンシー・ドメイン内にキャッシュされているかどうかとを示す、第2のデータ無効コヒーレンシー状態に更新する。

(もっと読む)

情報処理装置

【課題】ソフトウェアの構成を変更することなく、プロセッサ及びバスの動作クロック周波数を処理単位に関わらずに最適に制御することにより、情報処理装置の省電力化又は高性能化を実現する。

【解決手段】プロセッサ20のメモリ50へのアクセス調停を行なうバスI/F30と、クロックをプロセッサ20へ供給する可変処理クロック発生器105と、クロックをバスI/F30へ供給する可変バスクロック発生器106と、プロセッサ20の動作の忙閑を識別する処理忙閑状態識別部103と、バスI/F30の動作の忙閑を識別するバス忙閑状態識別部104と、処理忙閑情報及びバス忙閑情報と、プロセッサ20及びバスI/F30を最適に動作させる為のクロック調整ルール101とに基づいて、可変処理クロック発生部105及び可変バスクロック発生部106に対してクロック発生指令を出すクロック調節部102とを備える。

(もっと読む)

アドレス変換用データ生成装置およびその制御方法、情報処理装置、アドレス変換用データ生成装置制御プログラム、ならびに該プログラムを記録した記録媒体

【課題】メモリ管理ユニットが参照するテーブルを不要とする。

【解決手段】アドレス変換用データ生成ユニット13は、論理アドレスの上位アドレスから、論理アドレスを物理アドレスに変換するために利用される変換アドレスを生成するものである。アドレス変換用データ生成ユニット13は、論理アドレスから物理アドレスへの変換に関して或る共通の属性を有する論理アドレスの範囲を示す設定情報を予め記憶する設定レジスタ部16と、論理アドレスの上位アドレスと、設定情報が示す論理アドレスの範囲とを比較して、論理アドレスの上位アドレスが含まれる論理アドレスの範囲を特定する比較部32〜34と、特定した論理アドレスの範囲に対応する共通の属性を示す属性情報を含む変換アドレスを生成する変換アドレス生成部35・36とを備える。

(もっと読む)

仮想計算機上でのページテーブルアドレスの変更を高速化する方法

【課題】 仮想計算機上で稼動するゲストOSがゲストページPTアドレスの更新する際の、VMMによるシャドウPT操作から冗長性を削減し、仮想計算機を高速化する。

【解決手段】 VMMが、複数のシャドウPTを、基にしたゲストPTと対応付けて保存する。そして、VMMがゲストPTアドレスの更新を検出した際に、更新後のゲストPTに対応するシャドウPTを検索する。対応するシャドウPTが存在する場合は、VMMはシャドウPTの書き換えを省略し、当該シャドウPTのアドレスをCPUに登録する。対応するシャドウPTが存在しない場合は、メモリを確保してシャドウPTを作成し、作成したシャドウPTのアドレスをCPUに登録し、更新後のゲストPTと作成したシャドウPTの対応関係を記録する。

(もっと読む)

変換索引マニピェレーション

TLBおよびTLBコントローラを含むコントローラ多段パイプラインを有するプロセッサ。TLBミス信号に応じて、TLBコントローラはメモリあるいは高いレベルのTLBのいずれかからアドレス変換情報を要求するTLB再ロードを開始し、そしてその情報をTLBの中に配置する。プロセッサはミスしている仮想アドレスを有するインストラクションをフラッシュし、そしてインストラクションをリフェッチし、結果的にインストラクションを再挿入する。TLB再ロードの開始およびインストラクションのフラッシュ/リフェッチは、直ちにパイプラインをストールすることなしに、実質的に平行して行われる。リフェッチされたインストラクションはTLB再ロードが完了するまでTLBアクセスポイント上部のパイプラインのポイントに保持され、そしてリフェッチされたインストラクションが次のアクセスに際してTLB内に「ヒット」を発生する。  (もっと読む)

(もっと読む)

マイクロプロセッサ

【課題】 システム固有のメモリ構成や入出力装置の構成に最適なプリフェッチ制御を行うことができるマイクロプロセッサを実現する。

【解決手段】 本発明のマイクロプロセッサは、CPU11がデータまたは命令コードを読み出すために必要なウェイト数16を生成するウェイト数設定レジスタ17およびアドレスデコーダ15と、CPU11のプリフェッチを許すウェイト数16の上限を示すウェイト上限値18を保持するウェイト上限値設定レジスタ19と、ウェイト数設定レジスタ17からのウェイト数16およびウェイト上限値設定レジスタ19からのウェイト上限値18を比較判定し、当該判定結果に基づいてCPU11のプリフェッチ機能を停止させるプリフェッチ禁止信号13を出力する判定回路20を有する。

(もっと読む)

デマンドページング技法を適用したシステムでページ置換実行時間を短縮させる方法および装置

【課題】 フラッシュメモリのような不揮発性格納装置の特性を考慮して、ページング技法を提供する。

【解決手段】ページング技法を適用したシステムでページ置換実行時間を短縮させる方法は、(a)ページフォールトの発生を知らせる信号を受信するステップ、(b)前記ページフォールトが生じたページを不揮発性メモリから読み取るステップ、および(c)前記フォールトが生じたページを格納する空間をメモリから検索して確保するステップを含み、前記(c)ステップは予め計算された限界時間以内に行われ、前記システムのメモリにロードされるデータの一部は前記不揮発性メモリに格納されているページング技法を適用する。

(もっと読む)

共有されるL2マッピング・キャッシュのための対称的割り当てのための方法およびシステム

タイル式メモリからデータを読み取るための方法、装置、システムおよび媒体。いくつかの実施形態では、方法は、一つのタイル式Xキャッシュ読み取り要求について、そのタイル式Xキャッシュ読み取り要求を分解することなくタイル式メモリから二つのキャッシュ・ラインを要求し、二つの要求されたキャッシュ・ラインに関連付けられたデータを返すことを含む。  (もっと読む)

(もっと読む)

有限トランザクションメモリシステム

有限トランザクションメモリシステムを提供する方法及び装置が記載される。一実施例では、ソフトウェアトランザクションメモリ(STM)アクセスに対応する処理は、先行するハードウェアトランザクションメモリ(HTM)アクセス処理が失敗する場合に実行される。  (もっと読む)

(もっと読む)

効率的かつ柔軟なメモリ・コピー動作

【課題】メモリ・コピー動作のあいだにプロセッサが後続の命令を実行し続けられるようなメモリ・コピー動作を提供し、不必要なプロセッサ・ダウンタイムを回避する。

【解決手段】半同期メモリ・コピー動作実行のためのメモリ・コピー命令を受信するステップを含む。半同期メモリ・コピー動作は、フラグ・ビットを設定することによりメモリ内のソース位置に対応する仮想ソース・アドレス及びメモリ内のターゲット位置に対応する仮想ターゲット・アドレスに関する妥当性の一時的な永続性を保つ。メモリ・コピー命令は、少なくとも仮想ソース・アドレス、仮想ターゲット・アドレス、及びコピーされるバイト数を識別する標識を含む。メモリ・コピー命令は、メモリ・コントローラによりメモリ・コピー動作を実行するために、メモリ・コントローラに結合されたキューに入れられる。後続の命令が命令パイプラインから利用可能になったときの実行が続行される。

(もっと読む)

再生装置、再生方法および再生プログラム

【課題】 着脱可能な記録媒体からのデータの読み出しを、記録媒体を入れ替えた場合でも高速に行えるようにする。

【解決手段】 光ディスク3の記録領域に対応するキャッシュ領域31をHDD4に確保すると共に、光ディスク3の識別情報に基づきキャッシュ情報30を作成する。光ディスク3から読み出したデータを領域31にキャッシュし、情報30内のビットマップにおいて、光ディスク3から読み出したセクタに対応する位置のフラグを「1」とする。光ディスク3が他のディスクに交換された後、再び光ディスク3が装填された際に、光ディスク3の識別情報が対応する情報30を取得する。光ディスク3への読み出し指示に対してこの情報30を参照し、ビットマップに基づき読み出し指示されたデータがキャッシュされていると判断したら、光ディスク3の代わりにHDD4からキャッシュされたデータを読み出す。

(もっと読む)

仮想計算機システム

【課題】

ゲストプログラムが複数のアドレス変換モードで動作可能であり且つ各アドレス変換モードにおいて同一ゲスト仮想アドレスが別ホスト実アドレスへ変換される場合、同一のページテーブルに重複登録され不正なアドレス変換によりホスト実アドレスにアクセスするのを避けかつアドレス変換機構を効率よく動作させる。

【解決手段】

主記憶に複数のホストページテーブル作成し、ゲストプログラムのアドレス変換モードが替わるのに応じてホストページテーブルの1つを選択し、PTAレジスタへ該選択したテーブルの先頭アドレスを設定してホストページテーブルを切り替える。

(もっと読む)

非対称型異種マルチプロセッサ環境でアトミック更新プリミティブを提供するための方法

【課題】 DMA転送との共有メモリを有する、非対称型単一チップ異種マルチプロセッサ・コンピュータ・システムに、アトミック更新のプリミティブを提供すること。

【解決手段】 予約付きゲット・ロック・ライン・コマンド、条件付きプット・ロック・ライン・コマンド、および無条件プット・ロック・ライン・コマンドを有するセットから、少なくとも1つのロック・ライン・コマンドが生成される。

(もっと読む)

161 - 180 / 245

[ Back to top ]