Fターム[5B005PP26]の内容

階層構造のメモリシステム (9,317) | 一致制御 (671) | バススヌーピング (99)

Fターム[5B005PP26]に分類される特許

81 - 99 / 99

データキャッシュシステム

【課題】効率の高いデータ転送を実現するデータキャッシュシステム

【解決手段】プロセッサと、主メモリと、複数のI/Oデバイスとを備えた複数のモジュールを有する情報処理システムのデータキャッシュ。本発明のデータキャッシュは、ロード演算に応答してプロセッサにデータを供給しかつ記憶演算に応答してプロセッサからのデータを書込むための、前記プロセッサに接続されたキャッシュデータメモリを有している。該キャッシュデータメモリには、特定化できるポリシーに従ってデータキャッシュの演算を制御するための補充コントローラが接続されている。キャッシュデータメモリには更に外部アクセスコントローラが接続されており、該外部アクセスコントローラは、キャッシュデータメモリのコンテンツが情報処理システムのモジュールにより発行される読取りリクエストおよび書込みリクエストに応答して読取り演算および書込み演算にアクセスできるように、外部メモリバスに接続されている。

(もっと読む)

電子システムでプロセッサキャッシュを効果的に利用するための方法論

処理動作を効率的に実行するためのシステムおよび方法は、電子装置での処理動作を制御するように構成されたプロセッサと、電子情報を格納するために電子装置に結合されたメモリとを含む。プロセッサによってメモリ内のターゲットデータからコピーされたキャッシュデータを局所的に格納するために、キャッシュが設けられる。プロセッサは一般的に、キャッシュに格納されたキャッシュデータを変更する。外部装置がターゲットデータにアクセスするために読出し動作を開始すると、プロセッサはそれに応答してターゲットデータをキャッシュデータにより更新する。加えて、プロセッサは、その後の処理動作を容易にするために、キャッシュデータ保持手順を利用してキャッシュデータをキャッシュに局所的に保持する。  (もっと読む)

(もっと読む)

キャッシュコヒーレンス装置

【課題】分散共有メモリ型のマルチプロセッサシステムにおいて、キャッシュコヒーレンシ維持を効率よく実現し、且つシステムの拡張性を損なうことのないキャッシュコヒーセンス装置の共通システムバス、更に、大規模なマルチプロセッサの利用が期待される基幹システムへの使用を考慮した信頼性の高い共有システムバス、更に、異なったバスとの接続を考慮し、既存のバス資産の有効活用を可能とする共有バスを提供する。

【解決手段】共有システムバスとして機能する第2共有バス12は、複数のプロセッサモジュールのバス接続ユニット32とバスアービタ(バス調停ユニット)とを結合して、複数のプロセッサモジュールの間でスプリット型パケット転送によりバスコマンドの転送を行い、バスコマンドに、アクセス要求元(ソースID)を示すソースフィールド、第1のアクセス要求先(第1宛先ID)を示す第1宛先フィールド、及び第2のアクセス要求先(第2宛先ID)を示す第2宛先フィールドの3つを備える。

(もっと読む)

情報処理装置

【課題】

従来のブレードサーバシステムのスケールアウト型の拡張性に加え、複数のブレードサーバモジュール間をSMP結合することによるスケールアップ型の拡張性を備えたサーバ装置を提供する。

【解決手段】

各ブレードサーバモジュール内部のノードコントローラはSMP結合インタフェースを有しており、バックプレーンを経由して結合される。バックプレーン上で各ブレードサーバモジュール間リンクを等長配線し、各ブレードサーバモジュール内にもバックプレーン上の各ブレードサーバモジュール間リンクと等長のループ配線をすることで同期をとる。各ブレードサーバモジュールに基準クロックを分配できる基準クロック分配ユニットをバックプレーンに搭載し、各ブレードサーバモジュール内部のクロック分配回路によって基準クロックを切り換えることで、SMP結合したブレードサーバモジュールの基準クロックの同期化を可能とする。

(もっと読む)

マルチプロセッサシステム

【課題】プロセッサ数に関わらず、スケーラビリティに優れ、なおかつプロセッサ間通信にかかる処理時間を短縮することができるマルチプロセッサシステムを提供する。

【解決手段】送信側のプロセッサモジュールでは、プロセッサが通信バッファプールからバッファを確保して通信データをライトした後、バッファのアドレス情報をヘッダにライトする。受信側のプロセッサモジュールでは、キャッシュコントローラが、ヘッダが書き換えられたことを検出して、ヘッダに格納されたアドレス情報に対応するバッファに格納されている通信データをリードし、アドレス情報を新たなキャッシュタグに格納するとともに、通信データをキャッシュブロックに格納した後、プロセッサに割込みをかける。そして、割込みを受けたプロセッサが、キャッシュブロックに格納されている通信データをリードする。

(もっと読む)

キャッシュコヒーレンス装置

【課題】2階層の共通バス構成により、プロセッサモジュール内でのキャッシュコヒーレンスのバス動作と、プロセッサモジュール間でのキャッシュコヒーレンスのバス動作を分離し、高速のキャッシュコヒーレンスを実現する。

【解決手段】メモリ管理ユニット26のディレクトリ記憶部30に加え、バス接続ユニット32は第2ディレクトリ記憶部を設け、この第2ディレクトリ記憶部には、他のプロセッサモジュールに対するアクセス要求で応答待ちにある状態をキャッシュライン単位に登録し、他のプロセッサモジュールからのアクセスに対し第2ディレクトリの記憶部の参照で同一キャッシュラインのアクセスを認識した場合、ビジーを応答することで、他のプロセッサモジュールのアクセス要求を、メモリ管理ユニット26側まで伝える必要がなく、ビシー応答を高速化できる。

(もっと読む)

メモリ・システムとその制御方法、データ・コヒーレンシを保つ方法

【課題】 データ・コヒーレンシを保ちつつ、ライト・アクセスを含むメモリ・アクセスの効率化を図る。

【解決手段】 バス10、11と、バスに接続するメモリ17、メモリ・コントローラ16、キャッシュを有する第1デバイス13、および第2デバイス15を備え、メモリ・コントローラは、キャッシュのデータおよび第2デバイスがメモリにライト・アクセスする場合におけるライト・データを一時記憶するためのバッファ20を含むことを特徴とするメモリ・システムを提供する。メモリ・コントローラのバッファに、キャッシュのデータおよび第2デバイスがメモリにライト・アクセスする場合におけるライト・データを一時記憶することにより、第2デバイスのライト・アクセス・リトライをなくしつつ同時にデータ・コヒーレンシを保つことができる。

(もっと読む)

情報処理装置、システム制御装置、システム制御方法

【課題】 スヌープ処理におけるSC間の同期エラーの復旧の可能性を向上させるシステム制御装置、システム制御方法を提供する。

【解決手段】 外部から受信したメモリアクセス要求を保持し、エラーリトライ指示に従って再び出力するローカルポート部11と、メモリアクセス要求をブロードキャストするブロードキャスト出力部12と、ブロードキャストされたメモリアクセス要求を受信するブロードキャスト入力部21と、受信したメモリアクセス要求を保持するグローバルポート部22と、スヌープ処理を行った結果であるキャッシュステイタスを送受信し、キャッシュステイタスに基づいて同期エラーを検出し、同期エラーとなったメモリアクセス要求を保持するローカルポート部11へエラーリトライ指示を出力するスヌープ制御部23とを備える。

(もっと読む)

マルチプロセッサの操作を管理する方法、システム、および製造物

【課題】マルチプロセッサの操作を管理する。

【解決手段】第1プロセッサはキャッシュ・ラインが第1プロセッサおよび第2プロセッサの両方が共有するリソースの共有メモリのラインからキャッシュされるキャッシュ・ラインを反復的に読み取る。共有メモリ・ラインとキャッシュ・ラインのコヒーレンシはキャッシュ・コヒーレンシ・プロトコルに従い保つ。ある側面において、反復的なキャッシュ・ラインの読み取りは第1プロセッサを占有し、第1プロセッサが共有リソースにアクセスするのを禁止する。別の側面において、共有リソースに関わる第2プロセッサの操作の完了時、第2プロセッサは共有メモリ・ラインにデータを書き込んで、共有リソースを第1プロセッサからアクセスできることを第1プロセッサに知らせる。それに応答して、第1プロセッサはキャッシュ・コヒーレンシ・プロトコルに従いキャッシュ・ラインの状態を変更し、第2プロセッサが書き込んだデータを読み取る。他の実施例を記述し特許請求する。

(もっと読む)

ロッキング・キャッシュを用いる直接的保存

【課題】 データをメイン・メモリにも書き込むことなく、キャッシュの一部又は他の高速メモリに記憶すること。

【解決手段】 本発明は、I/O装置、ネットワーク、又はディスクから転送されたデータを、メイン・メモリにも書き込むことなく、キャッシュの一部又は他の高速メモリに記憶する方法を提供する。さらに、データは、使用のためにロードされるまでキャッシュ又は他の高速メモリに「ロック」される。データは、ソフトウェアの制御下で明確に上書きされるまで、ロッキング・キャッシュ内に残る。本発明の実施形態においては、プロセッサは、データを、メイン・メモリにも書き込むことなく、キャッシュ又は他の高速メモリに書き込むことができる。キャッシュの一部又は他の高速メモリを、付加的なシステム・メモリとして用いることができる。

(もっと読む)

マルチプロセッサシステムで多重構成をサポートする方法及び装置

【課題】1つ以上のマルチプロセッサシステムを、1つ以上の外部デバイスと相互接続し、高い処理機能を実現するための新たな方法や装置に対する技術を提供する。

【解決手段】1つ以上の通信バスを介して動作可能となるように相互に結合された複数のプロセッサと、コンフィギュラブルなインターフェース回路と、を有するマルチプロセッサを提供する。このインターフェース回路は、マルチプロセッサと1つ以上の外部デバイスとを相互接続することができ、かつ、マルチプロセッサの1つ以上のメモリと、1つ以上の外部デバイスの1つ以上のメモリと、の間のキャッシュのコヒーレンシーを維持することができる、コヒーレントな対称型インターフェースを有する。

(もっと読む)

マルチプロセッサシステム制御装置、スケーラブルノード、スケーラブルマルチプロセッサシステム、マルチプロセッサシステム制御方法。

【課題】 スヌープリトライの性能を改善するマルチプロセッサシステム制御装置、スケーラブルノード、スケーラブルマルチプロセッサシステム、マルチプロセッサシステム制御方法を提供する。

【解決手段】 自ノードからのデータの要求を保持する複数のローカルポートと、ローカルスヌープを行うローカルスヌープ部と、ローカルスヌープの結果、要求データが処理できない場合に、要求を他ノードへブロードキャストするブロードキャストキューと、他ノードからブロードキャストされた要求を保持する複数のグローバルポートと、グローバルスヌープを行うグローバルスヌープ部と、グローバルスヌープの結果、要求データが処理できない場合のリトライ指示において、所定の条件に従ってグローバルリトライモードとローカルリトライモードを切り替える、複数のリトライモード制御部13とを備えた。

(もっと読む)

キャッシュメモリのライトバック装置

【課題】 システムバスの使用効率を向上させることのできるキャッシュメモリのライトバック装置を提供する。

【解決手段】 ライトバック装置1は、キャッシュメモリ100のインデックスを走査してダーティなキャッシュラインを検出するライトバック制御部2と、システムバス200を監視してシステムバス200のアイドル状態を検出するスヌープ部4と、ライトバック制御部2によりダーティであることが検出されたキャッシュラインのデータを一時保存し、その後、スヌープ部4によりシステムバス200がアイドル状態であることが検出されたときに、システムバス200を介してメインメモリ300へ1ワードごとにシングルライトでライトバックするシングルライトバックライトバッファー部5とを有する。

(もっと読む)

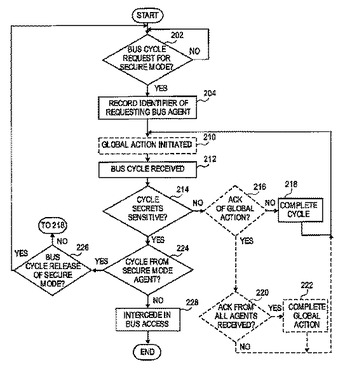

セキュアな実行中のリソースのデッドロックなしのバス保護のシステム及び方法

セキュアな実行中のメモリ・リソース及びI/Oリソースのデッドロックのないバス保護の方法及びシステム。バス・サイクルによって、セキュア実行モードへバス・エージェントが入ることが起動される。チップセットは、セキュア・モード・プロセッサの識別子を記録する。その後、チップセットは、セキュア・モード・プロセッサがセキュア・モードを出る前に別のバス・エージェントが、セキュリティ面で配慮を要するバス・サイクルを試行する場合、仲裁する。  (もっと読む)

(もっと読む)

演算処理装置

【課題】マルチプロセッサでのLinux動作時は、ひとつのタスクがCPUの数だけ実行される可能性があり、それに相当する数の外部メモリへのリフィル要求およびキャッシュ間共有によるペナルティーが発生する可能性があるため、ユニプロセッサよりマルチプロセッサの方がキャッシュの局所性によるミス率が増えることが予想される

【解決手段】キャッシュアクセスミスが発生した場合のキャッシュ間のスヌープアクセスで、他のローカルキャッシュがデータをキャッシュしているとして、偽りの情報を伝達すると同時に、そのローカルキャッシュがリフィル動作を行うことによって、複数のローカルキャッシュに対して同時にリフィル動作を行う擬似データ整合性管理部を有しており、命令とデータローカルキャッシュ間のキャッシュ同時リフィル、および、整合性管理を行うことができる擬似データ整合性管理部を提供する。

(もっと読む)

キャッシュ競合の解決

マイクロプロセッサ内及び/又はコンピュータ・システム内のキャッシュ競合の防止。特に、本発明の実施例は、特定のキャッシュ又はキャッシュ群へいくつかのアクセスを行い得るプロセッサ内及び/又はコンピュータ・システム内のキャッシュ・アクセス競合を管理するための手法に関する。

(もっと読む)

(もっと読む)

マルチコアプロセッサにおけるアイドル状態移行の調整

プロセッサを管理するシステム及び方法は、複数のコアを有するプロセッサのコアにおいてコマンドを検出し、当該コマンドは、コアのアイドル状態への移行をリクエストする。コアの電力消費は、コマンドと複数のコアのそれぞれのアイドル状態とに基づき管理される。  (もっと読む)

(もっと読む)

メモリシステム制御装置およびメモリシステム制御方法

【課題】プロセッサ毎にキャッシュメモリを有するマルチプロセッサシステムにおいて主記憶とのトランザクションを減少させること。

【解決手段】メモリシステム制御装置200が、プロセッサ100a〜100dから書込みを前提としたリード要求を受け、そのデータを要求元のプロセッサに送出した場合に、スヌープキャッシュ更新部233は、スヌープキャッシュにそのデータが「強い更新状態」であることを記憶させる。データ取得手順選択部232は、「強い更新状態」でスヌープキャッシュに存在するデータをプロセッサ100a〜100dから要求された場合には、主記憶300に対して投機リードをおこなわずに、プロセッサのキャッシュメモリからデータを取得する。

(もっと読む)

マルチインタフェースキャッシュにおけるジョイントコヒーレンシ状態のための方法及び装置

キャッシュコヒーレンシ状態のための方法及び装置が開示される。一実施例では、インナーインタフェースとアウターインタフェースの2つのインタフェースを介しアクセス可能なキャッシュは、ジョイントキャッシュコヒーレンシ状態を有する。ジョイントキャッシュコヒーレンシ状態は、インナーインタフェースに対して第1状態を、アウターインタフェースに対して第2状態を有し、第2状態は第1状態より高い優先度を有する。一実施例では、このことは、投機的無効を促進する。他の実施例では、このことは、インナーインタフェースを介したスヌープトランザクションを減少させる。  (もっと読む)

(もっと読む)

81 - 99 / 99

[ Back to top ]