Fターム[5B015JJ03]の内容

Fターム[5B015JJ03]に分類される特許

1 - 20 / 150

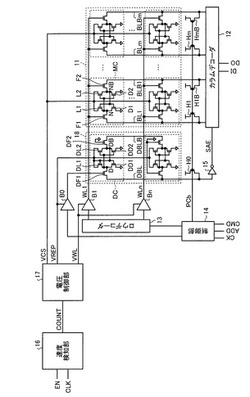

半導体記憶装置

半導体記憶装置

【課題】動作速度の低下を抑制しつつ、動作マージンを向上させることが可能な半導体記憶装置を提供する。

【解決手段】速度検知部16は、メモリセルMCの読み出し速度を検知し、電圧制御部17は、メモリセルMCの読み出し速度に基づいてワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSのいずれか少なくとも一方を制御する。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体記憶装置

【課題】低消費電力化を図れるようにした半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリセルと、メモリセルに接続された第1のビット線及び第2のビット線と、第1及び第2のビット線に接続されて第1及び第2のビット線間の電圧を増幅するセンスアンプとを備え、センスアンプが、差動増幅用のトランジスタ対を構成する第1及び第2の駆動トランジスタと、これら第1及び第2の駆動トランジスタのソースとソース制御端子との間にそれぞれ接続された第1及び第2のキャパシタとを有する。センスアンプは、センス動作に先立って、第1及び第2の駆動トランジスタのドレイン側をプリチャージすることにより、第1及び第2のキャパシタに第1及び第2の駆動トランジスタのしきい値情報を保持し、センス動作時に、第1及び第2の駆動トランジスタのソース電圧を第1及び第2のキャパシタに保持されたしきい値情報で補償する。

(もっと読む)

SRAMおよびその制御方法

【課題】

断熱的SRAM回路の回路構造と制御方法を改良し、さらなる低消費電力化を実現するためのSRAM回路を提供すること。

【解決手段】

従来の断熱的SRAMで記憶保持として用いられているインバータからなるフリップフロップ回路を抵抗負荷型のMOSトランジスタに置き換え、かつ読み込み・書き込み選択線の切り替えにCMOSトランスミッションゲートを配置することで、書き込み時における消費電力の増加を解決できる。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】SRAMは、複数列に対応して設けられた複数のセル電源線、電源電圧を供給する電源線、及び前記複数のセル電源線にそれぞれ対応して設けられ、各々はその対応するメモリセル電源線と前記電源線との間を電気的に接続する複数の電源回路を含む。メモリセルの各々は、第1及び第2のPチャネル型トランジスタと、第1ないし第4のNチャネル型トランジスタと第1及び第2の記憶ノードとを有するCMOSラッチ回路で構成される。電源回路は、第1の状態時にはその接続するセル電源線に第1の電圧を供給し、第2の状態時にはその接続するセル電源線に前記第1の電圧よりも低い第2の電圧を供給する、

(もっと読む)

半導体装置

【課題】読み書きコマンドに基づき、メモリアレイはアクティブ/非アクティブ状態に制御され、非アクティブ状態のメモリアレイにはクロック信号あるいは電源を供給しないことにより消費電力を削減することができる半導体装置を提供する。

【解決手段】複数のメモリアレイ10A〜10Nを備え、複数のメモリアレイの各々は、複数のメモリセルを含み、複数のメモリアレイにそれぞれ対応して設けられる複数のメモリアレイ制御回路12A〜12Nをさらに備える。複数のメモリアレイ制御回路の各々は、対応するメモリアレイへの読み書き動作を制御する読み書き制御回路112A〜112Nと、対応するメモリアレイの各々にクロック信号および読み書き制御回路からの出力信号に基づいて対応するメモリアレイを活性化するように選択する選択回路とを含む。

(もっと読む)

スタティックRAM

【課題】動作速度および信頼性を維持しながら、消費電力を低減したSRAMの実現。

【解決手段】複数のワード線WLと、複数のローカルビット線対LBL,LBLXと、複数のローカルビット線対の複数のワード線との交差部に設けられた複数のメモリセルC0-Cmと、複数のローカルビット線対毎に設けられた容量共通化回路BCと、複数の容量共通化回路を接続する共通接続ラインCLNと、複数のローカルビット線対に接続されるグローバルビット線対GBL,GBLXと、を有し、容量共通化回路は、対応するローカルビット線対と共通接続ラインの間に接続された2個のNチャネルトランジスタを有するスタティックRAM。

(もっと読む)

半導体装置

【課題】消費電流を低減させる。

【解決手段】半導体装置は、外部端子から供給された外部電源電圧より低い第1内部電圧を第1出力端子から出力する第1降圧回路、外部電源電圧より低い第2内部電圧を第2出力端子から出力する第1モードと第2出力端子から第1及び第2内部電圧より低い第3内部電圧を出力する第2モードとが切替えられる第2降圧回路、第1出力端子に接続され接地電圧が供給される第1SRAMを含む第1内部回路、第2出力端子に接続され接地電圧が供給される第2SRAMを含む第2内部回路とを備え、スタンバイ時に第2降圧回路は第2モードに制御され、第1内部回路の高位電源電圧として第1降圧回路から第1内部電圧が供給されて第1SRAMの記憶内容は保持され、第2内部回路の高位電源電圧として第2降圧回路から第3内部電圧が供給されて第2SRAMの記憶内容は消失される。

(もっと読む)

半導体記憶装置及び半導体記憶装置の制御方法

【課題】消費電力を低減すること。

【解決手段】グローバル入出力回路21のライトアンプWAGは一対のスイッチSW1,SW2を介してデータビット線対DBL,DBLXと接続されている。データビット線対DBL,DBLXは、スイッチSW3,SW4を介して、グローバル入出力回路21と各ブロック22,23との間でデータを転送するグローバルビット線対GBL,GBLXとそれぞれ接続されている。ライトアンプWAGは、入力データDIに応じてデータビット線対DBL,DBLXを駆動する。スイッチSW1,SW2をオフし、ライトアンプWAGからデータビット線対DBL,DBLXを切り離す。そして、スイッチSW3,SW4をオンし、データビット線対DBL,DBLXにグローバルビット線対GBL,GBLXを接続する。

(もっと読む)

半導体装置、それを用いた無線通信端末、及び電源制御方法

【課題】従来の半導体装置は、消費電力が大きくなる問題があった。

【解決手段】半導体装置1は、プログラムとプログラムによって利用されるデータとの少なくとも一方が格納される記憶領域部16と、プログラムを実行して記憶領域部16にバスを介してアクセス要求を発行する機能ブロック11と、バス23上に流れる、記憶領域部16に対するアクセス要求を示す第1の信号REQと、記憶領域部16によるバス23の占有状態を示す第2の信号GNTと、を監視して記憶領域部16へのアクセスが発生していない期間は記憶領域部16をスタンバイ状態に制御し、記憶領域部16へのアクセスが発生している期間は記憶領域部16を活性状態に制御するバス状態監視回路20と、を有し、記憶領域部16は、プログラム又はデータを記憶する記憶セルの低電位側電源電圧と高電位側電源電圧との電圧差を前記スタンバイ状態において活性状態よりも小さくする。

(もっと読む)

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

書込み用ビットラインの充放電電力を削減する半導体記憶装置

【課題】8Tr SRAMにおけるハーフセレクト問題を解決でき、同時に、従来のライトバック手法で問題となっていたハーフセレクト列における充放電電力削減を実現できる半導体記憶装置を提供する。

【解決手段】8Tr SRAMにおいて、1)列方向のメモリセル群の各メモリセルの読出し用ビットライン(RBL)から保持データを読出すことが可能で、読出されたデータに応じて、ハーフセレクト列のメモリセルのみ、書込み用ビットラインを駆動するビットラインハーフ駆動回路と、2)ビットラインハーフ駆動回路のイネーブル信号(DRN)と列選択信号(CLE)とを入力してビットラインハーフ駆動回路を活性化させる選択信号回路と、3)列方向のメモリセル群の書込み用ビットラインをイコライズし、書込み用ビットラインのプリチャージを行わないイコライザー回路を備える。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体記憶装置

【課題】消費電力低減が図られた新規な構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線と、ワード線にワード線選択信号を供給するワードドライバと、ワード線に接続されたメモリセルと、メモリセルに電源電圧を供給するセル電源線と、セル電源線への電源電圧の供給状態を制御する電源制御回路とを有し、電源制御回路は、セル電源線に電源電圧が供給されるオン状態と、セル電源線に電源電圧が供給されないオフ状態とを切り替えるスイッチ回路と、ワードドライバからワード線選択信号を供給され、ワード線選択信号が供給される前、スイッチ回路をオフ状態に保持し、ワード線選択信号が供給されると、スイッチ回路をオン状態に切り替え、ワード線選択信号の供給が終了した後も、オン状態を保持するスイッチ制御回路とを有する。

(もっと読む)

フル・スイング・メモリ・アレイを読み出すための方法及び装置

【課題】フル・スイング・メモリ・アレイを読み出す時の電力を削減する。

【解決手段】フル・スイング・メモリ・アレイは、複数のローカルビット線およびグローバルビット線を含んでいる。消費電力低減のために、グローバルビット線を駆動する方法は、トライステイト・デバイスを介してグローバルビット線に複数のローカルビット線をつなぐステップを含んでいる。方法は、複数のトライステイト・デバイスのうちの1つを有効にするためのグローバル選択信号を生成し、有効とされたトライステイト・デバイスの出力を駆動するために対応するローカルビット線を選択するステップをさらに含んでいる。グローバルビット線上で同じ値を連続して読み取る場合に、グローバルビット線の状態を遷移させないように、グローバルビット線が駆動される。

(もっと読む)

半導体記憶装置

【課題】AポートとBポートのロウアドレスが一致した場合においても、そのロウに属するメモリセルのワード線が両ポートとも開くのを防止しつつ、AポートおよびBポートからメモリセルに独立にアクセスする。

【解決手段】AポートのロウアドレスARADとBポートのロウアドレスBRADとが一致した場合、クロックACLK、BCLKに基づいて生成されたクロックXCLKに基づいてAポートのワード線電位AWLを制御することでAポートのみからメモリセルMCにアクセスさせ、クロックACLKに基づいてAポート用ビット線BLA、BLBAとAポートとの間でデータをやり取りさせるとともに、クロックBCLKに基づいてAポート用ビット線BLA、BLBAとBポートとの間でデータをやり取りさせる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

信号線駆動装置、アドレスデコーダ及びメモリ

【課題】容量素子を用いることなく、充放電電流を削減する。

【解決手段】本発明の一形態に係る信号線駆動装置100は、共通電源線102と、第1電位が供給される第1電源線との間の遮断と導通とを切り替える電源遮断スイッチ101と、共通電源線102と出力信号線SEL0との間の遮断と導通とを切り替える第1電源スイッチ130と、共通電源線102と出力信号線SEL1との間の遮断と導通とを切り替える第1電源スイッチ131と、制御回路103とを備える。制御回路103は、入力信号ISEL0が第1論理値から第2論理値に変更され、かつ、入力信号ISEL1が第2論理値から第1論理値に変更される場合に、電源遮断スイッチ101をオフ状態にするとともに、第1電源スイッチ130及び131を共にオン状態にし、その後、電源遮断スイッチ101、第1電源スイッチ131をオン状態にするとともに、第1電源スイッチ130をオフ状態にする。

(もっと読む)

1 - 20 / 150

[ Back to top ]