Fターム[5B015JJ31]の内容

Fターム[5B015JJ31]の下位に属するFターム

共通化/共有化/共用化 (56)

信号線の本数を減らす (26)

素子数の削減 (60)

Fターム[5B015JJ31]に分類される特許

1 - 20 / 65

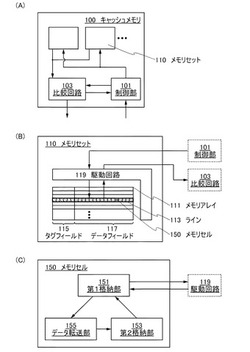

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】半導体メモリのセンス増幅器は、回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える必要がある。

【解決方法】本発明の差動センス増幅器は、第1のビットライン(BL)に接続された出力および第1のビットラインに対して相補的な第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力および第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータとを備え、それぞれのCMOSインバータはプルアップトランジスタ(M21、M22)および前記プルダウントランジスタ(M31、M32)を備え、プルアップトランジスタ(M21、M22)またはプルダウントランジスタ(M31、M32)のソースは、トランジスタのソースと電圧源との間に中間トランジスタを置くことなく、プルアップ電圧源またはプルダウン電圧源に電気的に結合され、接続されることを特徴とする。

(もっと読む)

半導体記憶装置、半導体記憶装置の設計方法、および半導体記憶装置の設計支援装置

【課題】コンパイル型マクロの階層化によるオーバーヘッドを最適化する。

【解決手段】第1ローカルメモリセルアレイと第1ローカルセンスアンプとを備える第1バンクと、第2ローカルメモリセルアレイと第2ローカルセンスアンプとを備える第2バンクとを有するメモリセルアレイを構成する。ここで、第2バンクは、グローバルビット線方向に沿って第1バンクに並んで配置されるものとする。その第1ローカルセンスアンプは、第1ローカルメモリセルアレイに含まれるメモリセルの数、または、第1ローカルセンスアンプからドライバ回路までの距離に基づいて最適設計された性能を有することが好ましい。また、その第2ローカルセンスアンプは、第2ローカルメモリセルアレイに含まれるメモリセルの数、または、第2ローカルセンスアンプからドライバ回路までの距離に基づいて最適設計された性能を有することが好ましい。

(もっと読む)

半導体装置

【課題】CMOSインバータを含むメモリセルにおいて、リーク電流によるゲート配線の制約やデザインルールの制約を起因とするメモリセルの面積の増大を抑える。

【解決手段】第1のインバータIV1と第2のインバータIV2を含むメモリセル1Aの第1の金属層として、第1の配線FL1及び第2の配線FL2が配置されている。第1の配線FL1は、第1のインバータIV1の2つのドレインDと第2のインバータIV2の第2のゲート配線GL2と接続している。第2の配線FL2は、第2のインバータIV2の2つのドレインDと第1のインバータIV1の第1のゲート配線GL1と接続している。第1の配線FL1は第2のゲート配線GL2と重畳し、第2の配線FL2は第1のゲート配線GL1と重畳して配置される。第1の金属層よりも上層には、第2の金属層と、その上層の第3の金属層が配置されている。

(もっと読む)

メモリ装置及びメモリシステム

【課題】アドレス空間の大きさが異なる複数のメモリ装置を同時にテストすることができるメモリ装置を提供することを課題とする。

【解決手段】アドレス空間の大きさが異なる複数のメモリ装置に対して複数ビットのアドレスのうちの一部のビットが共通のアドレスを入力して同時にテストを行う際のアドレス空間の小さい方のメモリ装置であって、アドレスにデータを記憶するメモリセルアレイと、メモリセルアレイのアクセスの回数をカウントするカウンタ(702)と、カウンタによりカウントされたアクセスの回数と回数設定値とを比較する比較回路(703)と、テストモードにおいて、カウンタによりカウントされたアクセスの回数が回数設定値に到達するとメモリセルアレイへのアクセスを禁止する動作停止制御回路(704)とを有するメモリ装置が提供される。

(もっと読む)

マルチ・ステート・バッファー手段、多値マルチプレクサ手段および多値デマルチプレクサ手段

【課題】マルチステートバッファー手段の提供。

【解決手段】電源線V0から電源線V9までで、電位の高さで隣同士となる各2電源線間に1つずつ設けられ、その入力端子9個を1つにまとめて入力端子Inとした9個の2値NOT手段から成る入力電位判別手段と出力端子Out1と電源線V0〜電源線V9それぞれの間に1つずつ設けられ、前記入力電位判別手段の9つの出力信号に基づき、そのいずれか1つがプルアップ又はプルダウン動作する10個のプル手段から成るプル手段群を持つ多値バッファー手段と、出力端子Out1と出力端子Out2の間に接続され、外部から与えられる出力制御信号に基づいて両出力端子Out1、Out2間を双方向にオンオフする多値トランスファーゲート手段を有する。

(もっと読む)

半導体記憶装置

【課題】従来の半導体記憶装置は、回路規模が増大する等の問題があった。

【解決手段】本発明にかかる半導体記憶装置は、データの読み出し又は書き込みが行われる第1のメモリセル101が行列状に複数配置された第1のメモリセルアレイ201と、対応する列に配置された複数の第1のメモリセル101のうち、何れかの第1のメモリセル101のデータを増幅し記憶する第2のメモリセル102が、行列状に複数配置された第2のメモリセルアレイ202と、を備える。また、第1及び第2のメモリセルアレイは、互いに列方向に対向配置され、第2のメモリセル102は第1のメモリセル101よりも面積が大きく、第1のメモリセルアレイ201は第2のメモリセルアレイ202の2倍以上の面積である。それにより、第1のメモリセル101のセル占有率を落とさずに、素子ばらつきによるデータ読み出し精度の悪化を抑制することができる。

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

半導体装置

【課題】レプリカセルの配置がチップ面積の増大に与える影響を小さくしたデュアルポートメモリ回路を備えた半導体装置を提供する。

【解決手段】デュアルポートメモリ回路(1)のメモリセルアレイ(2)は、デュアルポートの一方からのリード動作の指示に応答するために用いる第1レプリカセルアレイ(RBLKA)とデュアルポートの他方からのリード動作の指示に応答するために用いる第2レプリカセルアレイ(RBLKB)とを有し、夫々のレプリカセルアレイは、メモリセルのデータ入出力端子が接続される相補ビット線の反転ビット線と非反転ビット線の夫々を中間部で切断した長さの並列配線が相互に短絡されて成るレプリカビット線(RBLA,RBLB)と、当該レプリカビット線に接続され前記メモリセルと等価のトランジスタ配置を有するレプリカセル(RC)とを有する。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置に面積の大きな冗長メモリセルアレイ、高感度冗長センス増幅器を設けることによる、半導体記憶装置の面積に与える影響を比較的小さくすることが課題である。

【解決手段】 メモリセルアレイは行方向および列方向に沿って2次元的に配置された複数のメモリセルを有し、複数のメモリセル中の少なくとも一列の複数のメモリセルが面積の大きな冗長メモリセルとして割り当てられる。行方向に沿って配置され、各々が前記メモリセルアレイの各列の列方向上に設けられた複数のセンス増幅器中、冗長メモリセルとして割り当てられた少なくとも一列の複数のメモリセルの列方向上に設けられた少なくとも1個のセンス増幅器が高感度冗長センス増幅器として割り当てられる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、ドライバ部分の占有面積の増大、或いは、半導体記憶装置全体の消費電力の増大を招くことなく高速動作を実現することを目的とする。

【解決手段】各メモリセルがビット線と第1及び第2のワード線で選択されるメモリセルアレイと、リード時に選択される前記第1のワード線を駆動する第1のドライバと、ライト時に選択される前記第2のワード線を駆動する第2のドライバを備え、前記第1及び第2のドライバは、互いに異なる駆動能力を有するように構成する。

(もっと読む)

半導体記憶装置

【課題】ビット幅の大きなメモリにおいて入出力回路の制御信号を高速に動作させる。

【解決手段】ダミーセルアレイ201をメモリセルアレイ101内に配置し、中間バッファ300を入出力回路400の間に配置することにより、ビット幅の大きなメモリにおいても面積増大効果を最小限に抑えつつ、入出力回路400の制御信号を高速かつ高周波で動作させることを可能にする。

(もっと読む)

マルチポートメモリデバイスおよび方法

マルチポートメモリデバイスの実施形態は、複数のポートと、いくつかが各ポートにネイティブでいくつかが各ポートに非ネイティブである複数のメモリバンクを含んでよい。そのメモリデバイスは、メモリバンクをポートにマッピングすることを示す構成データを記憶する構成レジスタを含んでよい。その構成データに応答して、例えば、ステアリングロジックは、ポートの各々をネイティブメモリバンクの一つまたは全てに、あるいは非ネイティブメモリバンクの一つまたは全てに結合してよい。  (もっと読む)

(もっと読む)

集積回路のためのオンチップ電圧変換装置およびシステム

【課題】 多数の電圧ドメインを有する集積回路デバイスおよびシステムのための改良された電圧変換システムを提供する。

【解決手段】 集積回路のためのオンチップ電圧変換装置は、第1のキャパシタと、この第1のキャパシタの第1の電極を第1の電圧ドメインの低側電圧レールに選択的に結合するように構成された第1のNFETデバイスと、第1のキャパシタの第1の電極を第1の電圧ドメインの高側電圧レールに選択的に結合するように構成された第1のPFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの低側電圧レールに選択的に結合するように構成された第2のNFETデバイスであって、第2の電圧ドメインの低側電圧レールが第1の電圧ドメインの高側電圧レールに対応する、第2のNFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの高側電圧レールに選択的に結合するように構成された第2のPFETデバイスと、を含む。

(もっと読む)

半導体集積回路

【課題】電源電圧が供給されるSRAMマクロを複数備えた半導体集積回路の回路面積を削減する。

【解決手段】ロジック回路104と複数のSRAMマクロ103とを有するシステムLSI100において、システムLSI100の外部から供給された電圧VDDPよりも低い安定化電圧VDDMを生成する電源回路102を設け、複数の各SRAMマクロ103に、電源回路102により生成した電圧VDDMと外部から供給された電圧VDDとを供給する。また、ロジック回路104には、外部から供給された電圧VDDを供給する。

(もっと読む)

メモリ回路とその導電層の配線

【課題】メモリ回路のビットライン、電圧ライン、ワードラインの配線を提供する。

【解決手段】メモリ回路100のメモリアレイ100aは、データを記憶する少なくとも一つのメモリセル101aを含む。メモリセル101aは、ワードラインWL、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインに結合される。メモリ回路100は、第一導電層、第一導電層に結合される第二導電層、及び、第二導電層に結合される第三導電層を備える。第三導電層は、ワードラインWLに対して配線され、メモリセル101a内で、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインがない。

(もっと読む)

半導体記憶装置

【課題】セルサイズを縮小化しつつ、読み出し特性を向上させることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のSRAMセルMCがマトリクス状に配置されたメモリセルアレイを有する。SRAMセルMCは、第1のインバータINV1と、第1のインバータINV1と入力端及び出力端が相互に接続された第2のインバータINV2と、第1のインバータINV1又は第2のインバータINV2のいずれか一方の入力端にゲートが接続された第1の読み出しドライバトランジスタQrd1と、第1の読み出しドライバトランジスタQrd1を介して第1の読み出しビット線RBLと接続され、ゲートが読み出しワード線RWLに接続された第1の読み出し転送トランジスタQrx1とを備える。第1の読み出し転送トランジスタQrx1は、メモリセルアレイ内の少なくとも2つのSRAMセルMC1、MC2の間で共有される。

(もっと読む)

半導体記憶装置

【課題】チップサイズの拡大を抑制するとともに、信号線を形成する領域を確保すること。

【解決手段】本発明の一態様に係る半導体記憶装置1は、複数のサブアレイが行列状に配置され、複数のサブアレイ列A12を有するメモリセルアレイA13と、メモリセルアレイA13の外側に形成され、サブアレイ列A12と略平行に並ぶように配置された複数のアドレスパッドを含むアドレスパッド列A11と、メモリセルアレイの中間部に形成され、サブアレイ列と略平行に並ぶように配置されたデータI/Oパッドを含むデータI/Oパッド列A10と、メモリセルアレイの中間部に配置されたアドレス入力回路A8と、メモリセルアレイA13上に、サブアレイ列A12と略直交する方向に形成され、アドレスパッドA14とアドレス入力回路A8とを直接接続するパッド入力アドレス配線A4とを備える。

(もっと読む)

半導体記憶装置

【課題】データ保持特性及び書き込み特性に優れ、簡単な回路で構成し得るメモリセルを提供する。

【解決手段】セル情報を読み出すメモリセルMC3を選択する読み出し専用ワード線WLRと、選択されたメモリセルからセル情報を読み出す読み出し専用ビット線BLRzとを備えた半導体記憶装置において、セル情報を保持するセル部Cと、セル部の一対の出力ノードN1,N2を、書き込み動作時に電源電圧が供給される書き込み専用ワード線WLxに接続する一対のトランジスタTN11,TN12とを備えたメモリセルMC3と、一対のトランジスタTN11,TN12のゲートに相補信号を書き込みデータとして入力する一対の書き込み専用ビット線BLx,BLzとを備えた。

(もっと読む)

半導体装置とメモリマクロ

【課題】簡単な構成で使い勝手のよいデュアルポートメモリを有する半導体装置及びメモリマクロを提供する。

【解決手段】半導体装置又メモリマクロは、1つの入力及び出力ポートを持つメモリ回路及び第1タイミング信号に対応して入力又は出力動作を行う第1ポートと、上記第1タイミング信号とは非同期の第2タイミング信号に対応して入力又は出力動作を行う第2ポートを有する調停回路を備える。上記メモリ回路は、メモリ動作終了信号を上記調停回路に出力する。上記調停回路は、上記メモリ回路が非動作状態のときは上記第1又は第2ポートの上記第1又は第2タイミング信号に対応して上記メモリ回路のメモリアクセスを可能とし、上記メモリ回路が動作状態のときには上記メモリ終了信号を待って上記第1又は第2タイミング信号に対応した上記メモリ回路のメモリアクセスを可能とする。

(もっと読む)

1 - 20 / 65

[ Back to top ]