Fターム[5B015KA04]の内容

Fターム[5B015KA04]に分類される特許

1 - 20 / 90

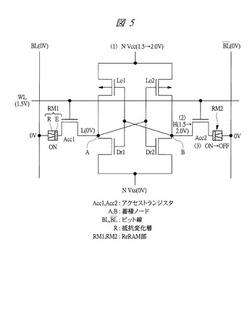

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体記憶装置

【課題】回路を構成する各トランジスタの設計サイズによらず、マージン設計なしに、安定動作可能な半導体記憶装置の提供。

【解決手段】データ入力端子D、書込許可入力端子φ、及びデータ出力端子Q−を有し、書込許可入力端子φのライト選択信号がアサートされるとデータ入力端子Dのライトデータ信号の電圧をスルーし、ライト選択信号がネゲートされるとデータライトデータ信号の電圧をホールドし、スルー/ホールドされる電圧の反転値をデータ出力端子Q−から出力するDラッチ回路2、並びにDラッチ回路2のデータ出力端子Q−とリードデータ線RDの間に接続され、リード選択信号がアサートされるとデータ出力端子Q−の電圧の反転値をリードデータ線RDへ出力しリード選択信号がネゲートされると出力が高インピーダンス状態となるトライステートバッファ3を具備するメモリセル1とを備えた。

(もっと読む)

半導体記憶装置

【課題】信号処理で重要となるマルチポート半導体記憶装置を提供する。

【解決手段】第1のビット線に接続される2つのデータ保持ノードを有してクロスカップル接続されたインバータからなるラッチ回路と、第1のビット線とインバータの各データ保持ノードとの間に設けられた第1のスイッチ部と、第1のスイッチ部の導通を制御する第1のワード線とを備えて構成されるメモリセルを備える。複数個のメモリセルの各データ保持ノードを各メモリセル毎にそれぞれ分離して1ビットが1個のメモリセルで構成される第1のモードと、複数個のメモリセルの各データ保持ノードを並列に接続して1ビットが複数個のメモリセルで構成される第2のモードを切り換える第2のスイッチ部とを備え、複数個のメモリセルの各データ保持ノードのうちの1つのデータ保持ノードを第2のビット線に接続するか否かを切り換える第3のスイッチ部をさらに含む。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置におけるマルチビットエラーの発生を抑制する。

【解決手段】複数のカラムを有し、互いに異なる1つのデータの入出力端子に各々が対応づけられるブロック(1I/Oビットに対応するセルアレイ)26A、26Bを複数有し、それらをカラム方向に隣り合わせて配置した第1のメモリセルアレイ、及びそれと同じく構成された第2のメモリセルアレイを備え、第1のメモリセルアレイのブロック26A−0、26A−2と第2のメモリセルアレイのブロックブロック26B−1、26B−3とを組とし、第1のメモリセルアレイのブロック26A−1、26A−3と第2のメモリセルアレイのブロック26B−0、26B−2とを組としてアドレスを割り当て、あるアドレスに対するアクセスにおいて、各メモリセルアレイにてそれぞれ1つおきのブロックの出力がデータとして出力されるようにする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

半導体集積回路

【課題】リード用トランジスタのソースとドレインがワード線とビット線に接続されたメモリセルを備えた半導体集積回路において、リード動作時の消費電力を低減する。

【解決手段】メモリセル10,11は、リード用トランジスタQN5を有するリードポートを備えている。トランジスタQN5は、ソースとドレインがリードワード線XRWL1とリードビット線RBL1に接続されており、ゲートが記憶ノードn1に接続されている。センスアンプ部17はPMOSクロスカップルQP13,QP14を備えており、トランジスタQP13,QP14は、ソースにリードビット線RBL1,XRBL1がそれぞれ接続されており、ドレインがセンスノードs1,xs1に接続されている。

(もっと読む)

SRAM装置

【課題】本発明は、SRAMアレイ上のすべてのセルに適切な選択トランジスタのしきい値電圧設定が可能なSRAM装置を提供することを課題とする。

【解決手段】電気的に切り離されたトランジスタ駆動用のゲート及びしきい値制御用の端子を有する電界効果トランジスタを選択トランジスタとして用い、前記選択トランジスタのしきい値制御用端子に対して与える電圧を、読み出し動作時には、読み出し開始時の電圧から徐々に増加させていく回路を具備したSRAM装置。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

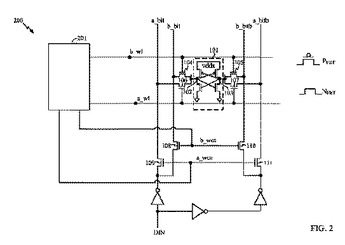

多ポートメモリ回路に書込みを行うためのシステムおよび方法

多ポートRAMは、複数のビット線および複数のビット線バーに結合されたデータ入力線を有する。この回路は複数のワード線も有する。ビット線、ビット線バー、およびワード線にメモリセルが結合される。この回路は、各ワード線が値を各ビット線から実質的に同時にメモリセルに書き込むのを可能にするコントローラをさらに含む。  (もっと読む)

(もっと読む)

半導体記憶装置およびその制御方法

【課題】低電源電圧の場合にも、メモリセルにおいて記憶内容を確実に保持することができ、しかも、メモリセルに対して確実に書き込みを行うことができる半導体記憶装置を提供すること。

【解決手段】行列状に配置される複数のメモリセルとメモリセルの列に対応して配置される複数のビットラインの対とを備えている。メモリセルは、クロスカップル接続され、各々の出力がビットラインの各々に至る経路に接続される一対のインバータと、各々のインバータを介して、電源電位から接地電位に至る経路に設けられる電源スイッチと、を含む。メモリセルの列に対応して配置され、列選択結果に応じて選択的に活性化されるカラムラインを備え、電源スイッチは、カラムラインが活性化される場合であってライト動作の場合には、非導通にされる。

(もっと読む)

半導体記憶装置

【課題】低電圧動作させた場合においても、メモリセルのサイズを低減させつつ、安定動作を実現するとともに、セルトランジスタのばらつきによる影響を低減する。

【解決手段】第1および第2のPMOSのソースは第1の電源線、第1のPMOSのドレインは第1のノード、第2のPMOSのドレインは第2のノード、第1および第2のNMOSのソースは第2の電源線、第1のNMOSのドレインは第1のノード、第1のノードは、第2のPMOSのゲートと第2のNMOSのゲート、第2のノードは、第1のPMOSのゲートと第1のNMOSのゲート、第1のトランジスタのゲートは、第1の信号線、ソースは第1のノード、ドレインは第2のノード、第2のトランジスタのゲートは、第2のノード、ソースは第3のノード、ドレインは第2の信号線、第3のトランジスタのゲートは、第3の信号線、ソースは第4の信号線、ドレインは第3のノードに接続される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の消費電流の増大を抑制しつつ、読み出しディスターブを改善する。

【解決手段】一対の駆動トランジスタN0、N1、一対の負荷トランジスタP0、P1、一対の書き込み専用伝送トランジスタN2、N3、一対の読み出し専用駆動トランジスタN4、N5および一対の伝送トランジスタN6、N7をメモリセルに設け、読み出し専用駆動トランジスタN4、N5のドレインを電源電位VDDに接続する。

(もっと読む)

半導体記憶装置

【課題】ビット幅の大きなメモリにおいて入出力回路の制御信号を高速に動作させる。

【解決手段】ダミーセルアレイ201をメモリセルアレイ101内に配置し、中間バッファ300を入出力回路400の間に配置することにより、ビット幅の大きなメモリにおいても面積増大効果を最小限に抑えつつ、入出力回路400の制御信号を高速かつ高周波で動作させることを可能にする。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、ドライバ部分の占有面積の増大、或いは、半導体記憶装置全体の消費電力の増大を招くことなく高速動作を実現することを目的とする。

【解決手段】各メモリセルがビット線と第1及び第2のワード線で選択されるメモリセルアレイと、リード時に選択される前記第1のワード線を駆動する第1のドライバと、ライト時に選択される前記第2のワード線を駆動する第2のドライバを備え、前記第1及び第2のドライバは、互いに異なる駆動能力を有するように構成する。

(もっと読む)

1 - 20 / 90

[ Back to top ]