Fターム[5B015KB62]の内容

Fターム[5B015KB62]の下位に属するFターム

電源昇圧回路 (27)

電源降圧回路 (71)

基準電圧発生回路 (24)

基板バイアス発生回路 (42)

Fターム[5B015KB62]に分類される特許

1 - 20 / 52

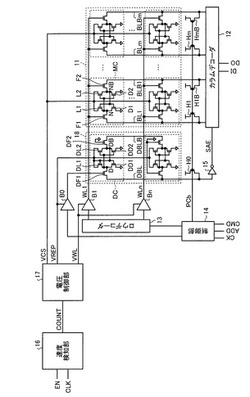

半導体記憶装置

【課題】動作速度の低下を抑制しつつ、動作マージンを向上させることが可能な半導体記憶装置を提供する。

【解決手段】速度検知部16は、メモリセルMCの読み出し速度を検知し、電圧制御部17は、メモリセルMCの読み出し速度に基づいてワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSのいずれか少なくとも一方を制御する。

(もっと読む)

半導体集積回路装置

【課題】先端プロセスではMOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷P型MOS及び駆動N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態から待機状態への変更に伴い、前記ソース線の電位を第1の電圧から当該第1の電位より高い第2の電位に変更する。前記電圧制御回路が前記ソース線の電位を前記第2の電位に変更したとき、前記スタティック型メモリセルの第1及び第2の記憶ノードのうちの一方は前記電源線の電位を保持し、前記第1及び第2の記憶ノードのうちの他方は前記第2の電位を保持する

【選択図】図5  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】SRAMの書き込み時間の増大を抑制しつつ、ライトマージンを増大させる。

【解決手段】メモリセルMCは、相補的にデータを記憶する1対の記憶ノードが設けられている。1対のビット線blt_0〜blt_k、blc_0〜blc_kは、メモリセルMCに書き込まれるデータに基づいて相補的に駆動される。ワード線wl_0〜wl_mは、メモリセルMCのロウ選択を行う。セル電源制御回路3は、メモリセルMCへのデータの書き込み時にビット線線blt_0〜blt_k、blc_0〜blc_kの電位に基づいて記憶ノードに供給されるセル電源を遮断する。

(もっと読む)

半導体装置

【課題】複数のメモリモジュールに対する低消費電力モードの解除に際して突入電流の発生を緩和する。

【解決手段】制御信号により低消費電力モードの設定と解除が制御される複数個のメモリモジュール(MDLij)の全部または一部がメモリブロック(BLK0〜BLKm)に属し、同じメモリブロックに属する複数個のメモリモジュールに並列的に前記制御信号を入力してモジュール内経路を伝播させ、その一部のメモリモジュールが前記モジュール内経路から後段のモジュール外経路(EXR_0〜EXR_m)に前記制御信号を出力させるように、制御信号の伝播経路を構成する。このとき、前記一部のメモリモジュールは、これと同一メモリブロック内における他のメモリモジュールよりも大きな記憶容量を有するメモリモジュールとする。

(もっと読む)

半導体装置

【課題】待機時のリーク電流が少なく、かつ、データ保持特性に優れたSRAMセルを備えた半導体装置を提供する。

【解決手段】それぞれ負荷MOSトランジスタを備えた複数のSRAMセルがマトリクス状に配置されたメモリセルアレイ110と、メモリセルアレイの第1の電源端子VDDMと第2の電源端子VSSMとの間に電源を供給する電源回路130と、負荷MOSトランジスタに基板バイアス電圧を与える基板バイアス発生回路140と、動作時より待機時の方が、第1の電源端子と第2の電源端子との間の電位差が小さく、かつ、負荷MOSトランジスタの基板バイアス電圧が浅くなるように電源回路と基板バイアス発生回路とを制御する電圧制御回路200と、を備える。

(もっと読む)

半導体記憶装置

【課題】消費電力低減が図られた新規な構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線と、ワード線にワード線選択信号を供給するワードドライバと、ワード線に接続されたメモリセルと、メモリセルに電源電圧を供給するセル電源線と、セル電源線への電源電圧の供給状態を制御する電源制御回路とを有し、電源制御回路は、セル電源線に電源電圧が供給されるオン状態と、セル電源線に電源電圧が供給されないオフ状態とを切り替えるスイッチ回路と、ワードドライバからワード線選択信号を供給され、ワード線選択信号が供給される前、スイッチ回路をオフ状態に保持し、ワード線選択信号が供給されると、スイッチ回路をオン状態に切り替え、ワード線選択信号の供給が終了した後も、オン状態を保持するスイッチ制御回路とを有する。

(もっと読む)

半導体集積回路装置

【課題】メモリセルのリーク電流成分に応じて、最適な電圧制御を行い、リーク電流を大幅に低減する。

【解決手段】レジュームスタンバイモードにおいて、リーク種判定回路7はリーク電流の成分がゲートリークと基板リークが多いと判断すると、VDDRレギュレータ5は電源電圧VDDよりも低い第1の電圧レベルの電源電圧VDDRを生成し、切り替えスイッチ9を介して、電源電圧VDDR1としてSRAMモジュール12に供給する。リーク種判定回路7がチャネルリークが多いと判断すると、VDDRレギュレータ5は第1の電圧レベルよりも高く、電源電圧VDDよりも低い電源電圧VDDR1をSRAMモジュール12に供給する。また、ARVSSレギュレータ6は、基準電圧VSSよりも高いセルソース電源電圧ARVSS1を領域2のSRAMモジュール12に供給する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

サブスレッショルドSRAMのための電源電圧制御回路及び制御方法

【課題】サブスレッショルド領域で動作するSRAMの書き込み動作安定性を改善する回路及び方法を提供する。

【解決手段】所定の遅延時間でサブスレッショルド領域で動作し、pMOSFETの典型値におけるしきい値電圧と、nMOSFETの典型値におけるしきい値電圧の差の絶対値が0.1V以上であるサブスレッショルドSRAMに対して制御出力電圧を電源電圧として供給する電源電圧制御回路であって、電源電圧に基づいて所定の微小電流を発生する微小電流発生回路と、発生された微小電流に基づいて遅延時間のバラツキを補正するためのpMOSFET又はnMOSFETのしきい値電圧の変化を含む制御出力電圧を発生して、制御された電源電圧としてサブスレッショルドSRAMに対して供給する制御出力電圧発生回路とを備えた。

(もっと読む)

半導体記憶装置

【課題】メモリセルからデータを読み出す際にメモリセルの保持しているデータの破壊を抑制する。

【解決手段】半導体記憶装置は、複数のメモリセルが行列状に配列されたメモリセルアレイと、前記複数のメモリセルの行方向に接続された複数のワード線と、前記複数のメモリセルの列方向に接続された複数のビット線と、前記複数のワード線を多重選択する行選択部とを備え、前記複数のビット線のそれぞれに接続されたメモリセルの数をNcellとし、前記行選択部により多重選択されるワード線の本数の単位をNWLとし、前記ビット線の静電容量をNcellで割った値をCblとし、電源電圧をVDDとし、前記複数のメモリセルのそれぞれの動作周波数をTcycとし、前記複数のビット線のそれぞれを介して読み出される電流の目標値をIcellとするとき、Ncell/NWL≦(4×Cbl×VDD)/(Icell×Tcyc)を満たす。

(もっと読む)

半導体装置

【課題】MOSトランジスタのしきい値電圧のばらつきに係らず、低電源電圧下においても安定かつ高速なデータ読出、スタンバイ電流の低減およびリテンション特性の向上を可能とする半導体装置を提供する。

【解決手段】半導体装置は、SRAMセルからなるメモリセルMCが行列状に配列されるメモリセルアレイおよび周辺回路を含むSRAMブロックと、FGTブロックと、SRAMブロックとFGTブロックとを電気的に接続するための接続ブロックとから構成される。FGTブロックは、FGT(フローティングゲートトランジスタ)50と、SRAMセルを構成するMOSトランジスタのしきい値電圧のばらつきに応じて、FGT50のしきい値電圧をチューニングするためのプログラム回路とを有する。FGT50は、SRAMブロックのスタンバイ時、ダイオード接続され、SRAM_VSS線と電気的に接続される。

(もっと読む)

安定性が改善されビットセルサイズが縮小された低出力5TSRAM

半導体装置及びデータプロセッサ

【課題】スタティックノイズマージンを劣化させずに書き込みマージンを向上させることを回路規模の物理的な増大を抑制して達成する半導体装置を提供する.

【解決手段】すなわち、相補ビット線を共有するスタティック型のメモリセルの列毎にその電源電圧を供給する電源配線(VDM[0]_0〜VDM[0]_i、VDM[1]_0〜VDM[1]_i)毎に電源スイッチ(30_0〜30_i、31_0〜31_i)を設けると共に、異なる電源スイッチの出力ノードの間を短絡する短絡スイッチ(32_0〜32_i)とを設け、相補ビット線選択信号が非選択のとき前記電源スイッチをオン状態とし、読出し動作で選択されたメモリセル列にはそのとき非選択のメモリセル列に対応する電源配線から前記短絡スイッチを介して電源電圧を供給し、書込み動作では選択されたメモリセル列への前記短絡スイッチからの電源電圧の供給を抑止する。

(もっと読む)

断熱充電メモリ回路

【課題】pMOSトランジスタのソース電極の電位を一定にしつつ、微細化に起因するエレクトロマイグレーションによる配線の断線を防止する。

【解決手段】まず、ワード線WLを零電位とし、スイッチ素子S1、S2がオン、オフの状態で、ビット線BL、NBLを正電位VDDまで昇圧する。スイッチ素子S1をオフし、スイッチ素子S2をオンし、スイッチ素子S2を介して、グラウンド線MCGLを、フリップフロップ回路FFの時定数より長い時間をかけて、正電位VDDに昇圧する。スイッチ素子S2をオフする。ワード線を正電位VDDとする。ビット線BL、NBLの内のフリップフロップ回路FFにデータ0を書き込む側のビット線、例えば、ビット線NBLを、フリップフロップ回路FFの時定数より長い時間をかけて、零電位に降圧する。

(もっと読む)

半導体装置

【課題】スタティックノイズマージンを確保して、低消費電力で、かつ、1V以下の低電圧で動作するSRAMを提供する。

【解決手段】それぞれ第1及び第2の駆動MOSトランジスタと、転送MOSトランジスタと、負荷MOSトランジスタにより構成されたスタティック型のメモリセルを有する半導体装置であって、一対のビット線と入出力回路とロジック回路とアレイ状に形成されたスタティック型のメモリセルに電源電位を供給するメモリ電源線とを有し、第1の転送MOSトランジスタは、ビット線対の一方に接続され、第2の転送MOSトランジスタは、ビット線対の他方に接続され、半導体装置には入出力回路の入出力回路用電源とロジック回路に使用されるコア電源とが入力され、メモリ電源線は、第2動作電位点に接続され、コア電源から電源が供給される。

(もっと読む)

データ記憶セルへの書き込み動作の支援

【課題】追加の回路を過度に増やすことなく、かつ他の隣接する記憶セルの安定性に過度に影響を与えることなく、記憶セルへの整合した書き込みを実現するデータストア及びデータを記憶する方法を提供する。

【解決手段】データストア10は、データストアに電力を供給するための電圧源30を備え、電圧源30は高電圧レベル及び低電圧レベルを出力し、また電圧源30及び少なくとも一つの記憶セル22の間に配置された書き込み支援回路40を備え、書き込み支援回路40は、パルス信号に応答して、高電圧レベル及び低電圧レベルの間の放電経路を提供し、パルス信号の幅に応じた期間の間、高電圧レベルより低い中間電圧レベルを生成し、フィードバックループは、パルス幅により決定される期間の間、低い中間電圧レベルを高電圧として受信し、それ以外の時間は高電圧レベルを受信するように、またパルス信号を生成するためのパルス信号生成回路50を備える。

(もっと読む)

半導体装置およびそれを用いた情報処理装置

【課題】LSIに複数の電源を供給して回路ブロックごとに必要な電圧の電源を供給し、LSIの必要情報処理能力を維持したまま消費電力を最小化するとともに、電源の供給に必要な配線を極力低減し、2種類の電源を供給することによって発生する、LSIのチップ面積の増加や信号配線の性能低下を抑えることである

【解決手段】2種類の電源が供給されるLSIにおいて、高い電圧の電源の配線の密度を、低い電圧の電源の配線の密度よりも高くする。これにより、回路ブロックの性能にしたがって供給する電源を選択することによって、LSIで処理される情報量を高く保ったまま、不必要な電力を抑制し、消費電力を低減することが可能である。

(もっと読む)

半導体装置

【課題】スタティック型半導体メモリの動作マージン不良をメモリセル特性に応じて最適に調整する。

【解決手段】各ワード線ドライバ(WDRi)に対応してドライバ電源電圧選択回路(VSWi)を設定する。このドライバ電源電圧選択回路(VSWi)は、そのメモリセル特定情報を格納する回路(32a,32b)に格納される。記憶データに従って複数の電圧(VDD1,VDD2,VDD3)の1つを選択してドライバ電源ノード12に伝達する。この電圧選択においてメモリセル特性に応じて読出マージン不良、または書込マージン不良対策を施すことができる。

(もっと読む)

メモリデバイス内の漏洩電流の低減

メモリデバイスと、メモリデバイス内に漏洩電流を低減する方法とが開示される。メモリデバイスは、複数のビットラインを含むメモリコアアレイと、このメモリコアアレイとインターフェースするように構成された周辺論理回路とを含む。メモリデバイスはさらに、周辺論理回路をグランド電圧から分離するように構成されたフットスイッチと、プリチャージ電流経路をメモリコアアレイの複数のビットラインから分離するように構成されたヘッドスイッチとを含む。メモリデバイス内の漏洩電流は、フットスイッチおよびヘッドスイッチで行われる分離によって低減することができる。  (もっと読む)

(もっと読む)

1 - 20 / 52

[ Back to top ]