Fターム[5B015QQ01]の内容

Fターム[5B015QQ01]の下位に属するFターム

可変の特性値(しきい値等) (31)

複数種類の特性値(しきい値等) (31)

Fターム[5B015QQ01]に分類される特許

1 - 20 / 32

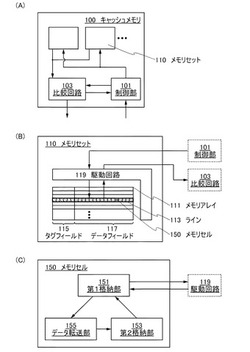

キャッシュメモリ、及びキャッシュメモリの駆動方法

【課題】低消費電力動作が可能で、且つキャッシュヒット率が向上したキャッシュメモリと、その駆動方法を提供する。

【解決手段】キャッシュメモリが有するメモリセット内の1つのメモリセルに2つのデータ格納部(第1格納部、第2格納部)と、1つのデータ転送部を設ける構成とし、2つのデータ格納部間でデータ転送部を介してそれぞれのデータを移行できる構成とする。さらに、2つのデータ格納部のうち、いずれか1つのデータ格納部は、外部から入力されるデータを格納可能で、且つメモリセットに対に設けられる比較回路にデータを出力可能な構成とすればよい。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置におけるマルチビットエラーの発生を抑制する。

【解決手段】複数のカラムを有し、互いに異なる1つのデータの入出力端子に各々が対応づけられるブロック(1I/Oビットに対応するセルアレイ)26A、26Bを複数有し、それらをカラム方向に隣り合わせて配置した第1のメモリセルアレイ、及びそれと同じく構成された第2のメモリセルアレイを備え、第1のメモリセルアレイのブロック26A−0、26A−2と第2のメモリセルアレイのブロックブロック26B−1、26B−3とを組とし、第1のメモリセルアレイのブロック26A−1、26A−3と第2のメモリセルアレイのブロック26B−0、26B−2とを組としてアドレスを割り当て、あるアドレスに対するアクセスにおいて、各メモリセルアレイにてそれぞれ1つおきのブロックの出力がデータとして出力されるようにする。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

メモリ用ワード線ドライバ

【課題】行の復号機能、及び/またはワード線の駆動機能に割り当てられたメモリデバイスの面積の割合を減少させることができる回路を提供する。

【解決手段】メモリアレイ内ワード線205を駆動する処理は、相補型金属酸化膜半導体(CMOS)トランジスタと、一以上の抵抗とからなる特定の組み合わせを組み込むワード線ドライバ200を含んでもよい。例えば、プルダウン処理は、一以上のNチャンネル金属酸化膜半導体電界効果(NMOS)トランジスタ220,222,224を用いて実行してもよく、一方、プルアップ処理は、一以上の抵抗210を用いて実行してもよい。こうしたワード線ドライバは、全てのCMOSトランジスタワード線デバイス(例えば、抵抗なし)の面積に比べて、こうしたワード線によって占有されたメモリデバイスの面積の減少を含む利点を与えることができる。

(もっと読む)

メモリ用ナノセンス増幅器

【課題】大容量化してもセンス増幅器数の増大を回避し、チップ面積の低減が可能なメモリ用センス増幅器を提供する。

【解決手段】メモリの一連のセル用のセンス増幅器であって、CMOSインバータを備えており、その入力部が前記センス増幅器の入力端子へ直接または間接的に接続され、かつ、その出力部が前記一連のセルをアドレス指定する局所ビットラインへ接続されることを意図して前記センス増幅器の出力端子へ接続されている書き込みステージと、センストランジスタを備えており、そのゲートが前記インバータの出力部へ接続され、かつ、そのドレインが前記インバータの入力部へ接続されている読み取りステージとを含む。

(もっと読む)

半導体記憶装置

【課題】従来の半導体記憶装置では、精度良くデータの書き込みを行うことができないという問題があった。

【解決手段】本発明にかかる半導体記憶装置は、記憶素子を構成する第1及び第2のインバータと、第1のインバータの出力側の記憶ノードV1と書き込み用ビット線WBL0との間に設けられ、書き込み用ワード線WWLに基づいて電流が制御される書き込み用トランジスタN3と、第2のインバータの出力側の記憶ノードV2と書き込み用ビット線WBL1との間に設けられ、書き込み用ワード線WWLに基づいて電流が制御される書き込み用トランジスタN4と、第1のインバータと高電位側電源との間に設けられ、記憶素子に書き込まれるデータに基づいて電流が制御される補助トランジスタP3と、第2のインバータと高電位側電源との間に設けられ、記憶素子に書き込まれるデータに基づいて電流が制御される補助トランジスタP4と、を備える。

(もっと読む)

半導体メモリのメモリセル間のデータコピー方法

【課題】アプリケーションやメモリ状況に応じてメモリセルのビット信頼性QoBを動的に変化させ得る半導体メモリにおいて、通常モードから高信頼モードへの移行を、高速、かつ、低電圧動作で行えるメモリセル間の一括データコピー方法を提供する。

【解決手段】通常モードから高信頼モードへとモード切り換えの際、コピー元セルからコピー先セルへ保持データを転送する方法であって、1)一対のビットラインの状態をハイレベルに、かつ、コピー先セルのワードラインの状態をハイレベルに、かつ、コピー先セルのグランドラインを電源電位にするステップと、2)コピー先セルのワードラインの状態をローレベルにするステップと、3)モード制御ラインを制御して、モード制御スイッチ部を導通させるステップと、4)コピー先セルのグランドラインをグランド電位に戻すステップと、から構成される。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11を直列又は一のpMOSトランジスタ12を備えた並列回路に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21を直列又は一のnMOSトランジスタ22を備えた並列回路に接続した第2の回路ブロック2とを備え、前記第1の回路ブロック1と前記第2の回路ブロック2との接続点Sを出力端子Voutに接続するとともに、全ての前記pMOSトランジスタ11,12のゲート及び全ての前記nMOSトランジスタ21,22のゲートを共通の入力端子Vinに接続する半導体回路。

(もっと読む)

半導体集積回路

【課題】 光照射により積極的に誤動作を誘発して機密保護情報を不正に獲得するというカードハッキングに対する防御が可能な半導体集積回路を提供する。

【解決手段】 ICカードマイコンなどの半導体集積回路に対し、標準的なロジックプロセスで構成され、他の回路と区別がつきにくく、待機電力が極めて小さい、光ディテクタを搭載する。光ディテクタは例えば、初期化動作でスタティックラッチ(120)に第1状態を保持し、第1状態のスタティックラッチを構成する非導通状態の半導体素子(112,113)に光が照射されて第2状態に反転する構成を備え、光ディテクタをメモリセルアレイに複数個配置する。スタティックラッチ型の光ディテクタをメモリアレイに組み込むことで、それを目立たずに配置することができる。光の照射によるリバースエンジニアリングを効果的に防ぐことができる。

(もっと読む)

半導体メモリ装置

【課題】低消費電力時の消費電流を抑制しながら保持マージンを確保することを可能とする。

【解決手段】MOSトランジスタTrRが、メモリセルMを構成するNMOSトランジスタTn1、Tn2と同一レイアウト構造(L)を備えており、低消費電力時においてノードN1の印加電圧から保持マージン電圧として抵抗R1の両端電圧を減圧すると共にMOSトランジスタTrRのしきい値電圧Vtを減圧したノードN7の電圧を安定化してノードN2に印加する。

(もっと読む)

半導体記憶装置

【課題】シングルエンドセンスアンプにより高速読み出しを可能とし、関連技術で設けられていたダミーメモリセルを不要とし、回路面積を縮減し、消費電力を低減する。

【解決手段】ビット線をグランド電位に放電するディスチャージ回路102と、シングルエンド入力構成のセンスアンプ108と、電源とセンスアンプの入力ノードSAin間に接続され、前記センスアンプの入力ノードからオン状態のカラム選択トランジスタ(N0、N1、・・・)を介してビット線を充電する充電用のトランジスタ106と、を備え、読み出し時、選択されたメモリセルが接続するビット線からグランドへの電流パスがオフ状態とされる場合、前記充電用のトランジスタ106により、前記センスアンプの入力ノードが充電されて電位が上昇し前記カラム選択トランジスタをオフさせた状態で前記センスアンプの入力ノードをさらに充電した後、読み出し動作が行われる。

(もっと読む)

半導体記憶装置

【課題】性能を維持したままでより小さなサイズに製造が可能なSRAMセルを有する半導体記憶装置を提供する。

【解決手段】pFETからなる一対のドライバトランジスタ302a、302bと、nFETからなる一対の負荷トランジスタ304a、304bと、pFETからなる一対のトランスファゲート306a、306bとからなる複数のスタティックランダムアクセスメモリセル300を具備する。

(もっと読む)

メモリセルへの給電の制御

【課題】プロセスのばらつきにもかかわらず、メモリセルへの「0」の書き込み性能と「1」の書き込み性能とを同じようにすること

【解決手段】半導体メモリ記憶セルおよびこれらメモリ記憶セルのアレイを含むメモリが開示されている。この半導体メモリ記憶セルは、反対の二進値を記憶するための2つのデバイスを含むフィードバックループと、前記2つのデバイスにデータを書き込み、かつこれらデバイスからデータを読み出すためのデータ入出力とを備え、前記2つのデバイスの各々は、1つの電源入力を備え、よって互いに独立して各デバイスに給電できるようになっている。

(もっと読む)

メモリ素子およびその動作方法

【課題】メモリ素子および動作方法を提供する。

【解決手段】メモリ素子は、少なくとも1つの列に配列された複数の記憶セルを有し、各列は、そこに関連する少なくとも1つのビット線および供給電圧線を有する。キャパシタンスは、各列に対して、供給電圧線と関連する少なくとも1つのビット線との間に存在する。制御回路は、各列に対して、電圧源の関連する供給電圧線への接続を制御する。メモリアクセス動作間の既定の期間に対して、制御回路は、少なくとも選択された列に対する供給電圧線を、その供給電圧線の電圧レベルが、関連する少なくとも1つのビット線の電圧における任意の変化に応答して変化するように、電圧源から切り離す。この基本的な機構は、書込み、ビットフリップ、読取り支援機構等の多様な支援機構を提供できる。本発明の技術は、このような支援機構を提供するための特に簡素で電力効率のよい技術を提供する。

(もっと読む)

ソフトエラーを減少させるための方法および記憶回路

【課題】ソフトエラーを減少させる。

【解決手段】ソフトエラーを減少させる方法には、記憶回路内の複数の節点に所定の状態を割り当てることと、記憶回路内に結合された複数の信号を評価することであって、第1の節点(節点A:NODE_A)がその所定の状態から変化することを可能にしかつ第2の節点(節点B:NODE_B)が摂動の影響を受けやすくなることを可能にすることと、第2の節点が所定の期間その所定の状態に維持することであって、該所定の状態に維持することにより前記記憶回路のソフトエラーにたいする影響の受けやすさを減少させることが含まれる。

(もっと読む)

半導体記憶装置

【課題】製造時に特別なプロセスを使用せず、低コストでデータ信号の読み出しを高速化する。

【解決手段】遅延インバータ回路10は、エンハンスメントタイプ・トランジスタTr2,Tr3から構成され、外部から入力されるクロック信号CK2を遅延した読み出し信号RS1をセンスアンプ回路に出力する。エンハンスメントタイプ・トランジスタ回路Tr1は、遅延インバータ回路10に供給される電源電圧を低く設定するために、遅延インバータ回路10と電源VDDの間に接続される。すなわち、特別なプロセスを必要としないエンハンスメントタイプ・トランジスタTr1を用いて、遅延インバータ回路10の電源電圧を低く設定し、電源電圧の許容範囲内における標準電圧、高電圧側において、データ信号の読み出しを高速化する。

(もっと読む)

SRAMメモリセルの評価方法及びSRAMメモリセルの評価プログラム

【課題】より短時間でスタティックノイズマージンの評価を行って、SRAMメモリセルの設計に要する時間を短縮化可能なSRAMメモリセルの評価方法及び評価プログラムを提供する。

【解決手段】SRAMメモリセルの第1のインバータの入出力特性データに対して座標軸を45度回転させる座標変換を行い、近似曲線へのフィッティングによって第1の近似曲線関数を特定するとともに、SRAMメモリセルの第2のインバータの入出力特性データに対して座標軸を45度回転させる座標変換を行い、近似曲線へのフィッティングによって第2の近似曲線関数を特定し、前記第2の近似曲線関数をY軸に対してミラー反転させた関数である第3の近似曲線関数を特定し、前記第1の近似曲線関数と前記第3の近似曲線関数の差分とした差分曲線関数の極値からスタティックノイズマージンを特定する。

(もっと読む)

NANDゲートを備えたNBTI耐性を有するメモリセル

NBTI耐性を有するメモリセルが、リング状の複数のNANDゲートで構成される。複数のNANDゲートは、それらNANDゲートのうちの1つがその出力に“0”を有し、残りのNANDゲートがそれらの出力に“1”を有するように構成される。このメモリセル内のPMOSトランジスタは、インバータベースのメモリセルにおいてより少ない劣化を被る。トランジスタの劣化を防止するための保護周波数帯が低減され、メモリセルの動作周波数が高められ得る。  (もっと読む)

(もっと読む)

1 - 20 / 32

[ Back to top ]