Fターム[5B018HA11]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | 冗長符号 (791)

Fターム[5B018HA11]の下位に属するFターム

Fターム[5B018HA11]に分類される特許

41 - 56 / 56

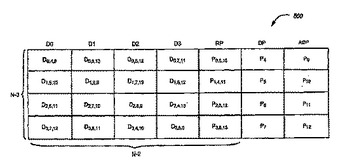

ストレージアレイにおける三重故障からの効率的な復旧を可能にする三重パリティ技術

アレイ内の3つの記憶装置の同時故障からの効率的復旧を可能にするように構成された、ストレージアレイの対角パリティ、及び反対角パリティの計算オーバヘッドを低減する三重パリティ(TP)技術。対角パリティは、アレイの全データディスク、及び行パリティディスクにわたって規定される幾つかの対角パリティ集合に沿って計算される。1つを除く全ての対角パリティ集合について、対角パリティが、対角パリティディスクに格納される。同様に、反対角パリティは、アレイの全データディスク、及び行パリティディスクにわたって規定される幾つかの反対角パリティ集合に沿って計算される。1つを除く全ての反対角パリティ集合について、反対角パリティが、反対角パリティディスクに格納される。TP技術は、均一なストライプの深さと、最適な量のパリティ情報を提供する。  (もっと読む)

(もっと読む)

半導体処理装置及び半導体集積回路

【課題】不揮発性メモリの消去対象とされる記憶情報をバックアップするのに要する時間を短縮する。

【解決手段】ページ単位で書換え動作が可能にされる複数のメモリマット(21,22)と、前記メモリマットに対するバイトアクセス制御可能なメモリ制御回路(26,37,38)とを有する。メモリ制御回路はバイトアクセス制御において複数のメモリマットを動作させ、データ書き換えでは一のメモリマットの中で選択されたページから読出したデータを書込みバイトデータでマージし、マージしたデータを他のメモリマットの中で選択された対応ページに書き込み、読出しでは複数のメモリマットの各々で選択されたページのうち有効なページであって最も最近書換えられたページから読出しを行う。一のメモリマットの中で選択されたページは他のメモリマットの中で選択されたページに対して書換え前の実質的なバックアップデータを保有することになる。

(もっと読む)

メモリ制御装置、プログラム、方法、メモリ、RFIDタグ

【課題】ビット値を1から0にする操作に比べて0から1にする操作が困難であるリセッタブルなメモリに対し、改竄を防止しつつ記憶させうるデータ数を増加させる。

【解決手段】複数ビット(例えば5ビット)の記憶容量をもつメモリに対し、ビット長m1,m2,...,mn,...,mNのN個の記憶単位(例えばビット長2,3の2個の記憶単位であるラウンドビット30とデータビット32)を設定する。各記憶単位においては、いずれか一つのビットに1、残るビットに0を割り当てて、改竄防止可能な記憶状態を設定する。そして、N個の記憶単位について組み合わせてなるm1×m2×...×mn×...×mN個の記憶状態列に対し、それぞれ一つのデータを対応づける。データの書き込みや読み込みは、この割り当てに従って行う。

(もっと読む)

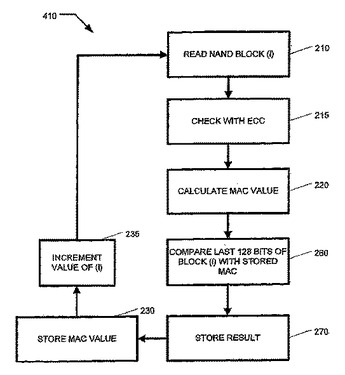

メモリカードコントローラファームウェアのハードウェアドライバ完全性チェック

メモリシステムは、コントローラのハードウェアにおいて実施される暗号化エンジンを備える。メモリシステムを起動する際に、ブートストラップ機構が実施され、ファームウェアの第1の部分が、実行時に実行すべきファームウェアの他の部分をプルインする。暗号エンジンのハードウェアは、ファームウェアの少なくとも第1の部分の完全性をベリファイするために使用される。したがって、システムを実行することになっているファームウェアのみが実行されることになる。  (もっと読む)

(もっと読む)

データ検査方法及び装置

【課題】フラッシュROMのデータ記録状態を確実に検査する。

【解決手段】フラッシュROMの各セクタの先頭部および終端部に特定コード(コード1,2)を格納する。フラッシュROMのデータ書き換えはセクタごとに行われ、データ内容をワークメモリにコピーして書き換えた後、フラッシュROMのデータ内容を消去してワークメモリから書き込む。各セクタの先頭部および終端部に格納されたコードが特定コードと一致するか否かを判定することで、記録されたデータが正常か否かを迅速に検査する。

(もっと読む)

転置状態パターンを利用するメモリ・チャネル

転置状態パターンを利用するメモリ装置および方法。メモリ・エージェントは転置状態パターンを発生させることのできるパターン発生器を含みうる。システムは、同一のリンク上でデータおよび転置状態パターンを送信する第一および第二のメモリ・エージェントを含みうる。  (もっと読む)

(もっと読む)

プログラマブル・ロジック・デバイス、情報処理装置、プログラマブル・ロジック・デバイスの制御方法

【課題】 プログラマブル・ロジック・デバイスに用いられる構成情報の異常の早期発見による予防保守を実現する。

【解決手段】 プログラマブル・ロジック・デバイス10に備えられたコンフィギュレーション回路20に、不揮発性メモリ60からコンフィギュレーションデータS4を読み出してユーザ論理の構築を行うコンフィギュレーション用メモリ制御回路24と、コンフィギュレーション操作完了後に定期的に不揮発性メモリ60からコンフィギュレーションデータS4を読み出してエラーチェックを行うメモリ監視用メモリ制御回路21を備えた。コンフィギュレーション操作完了後の不揮発性メモリ60の放置期間における当該不揮発性メモリ60内のコンフィギュレーションデータS4の異常を、次回のコンフィギュレーション操作の実行に先立って早期に発見でき、予防保守が可能になる。

(もっと読む)

半導体装置

【課題】 内部メモリを有する半導体装置にて保持されているデータの品質を保証し、かつ消費電力をさらに低減できるようにする。

【解決手段】 記憶装置2に保持しているデータを複写して保持する第1のメモリ5と、第1のメモリに保持されるデータのチェック符号を保持し、データ保持保証電圧以上の電源電圧が常に供給される第2のメモリ6と、チェック符号に基づいて第1のメモリに保持しているデータの誤りを検出するデータ検査部7と、データ誤りが検出されたブロックに対応するデータのみを記憶装置から第1のメモリに複写するリロード部8,9とを備えることで、第1のメモリに保持されるデータの誤りを検出できるようにして、データを保証し、かつ第1のメモリに供給する電源電圧をデータ保持保証電圧より低下させることができるようにする。

(もっと読む)

電子制御装置

【課題】給電の有無にかかわらずデータの保持機能を有するメモリを用いない場合であっても、所定の演算に用いられるデータである演算データをより適切に使用することのできる電子制御装置を提供する。

【解決手段】電子制御装置100では、機関始動前に取得される大気圧データがRAM114に書き込まれる。更に、この際、大気圧データの論理値を反転したデータである大気圧データの反転データもRAM114に書き込まれる。機関始動によってバッテリBの電圧が低下すると、マイクロコンピュータ110がリセットされる。このリセットからの復帰に際し、マイクロコンピュータ110では、大気圧データと大気圧データの反転データとがRAM114から読み出され、読み出された大気圧データの反転データが、読み出された大気圧データを論理反転したものに等しいか否かが判断される。

(もっと読む)

ICカード、データ出力方法、及びデータ格納方法

【課題】 ファイルの一部が破壊されている場合、そのファイル全体を読み出そうとすると、データが一切読み出されないか、あるいは全データが読み出されるものの、どこでデータ化けを起こしているかの情報が全く与えられない。

【解決手段】 本発明は、レコード型構造あるいは透過型構造のファイルにおいて、外部から受信したコマンドの種類を判断するコマンド判断部と、前記コマンド判断部が前記コマンドがレコードの読み出しコマンドであると判断した際に、読み出し要求がなされたレコード或いはフィールドの誤り検出符号を検証する誤り検証部と、前記誤り検証部により正常と判断されたレコードあるいはフィールドと異常と判断されたレコード或いはフィールドとを識別することができるように所定の識別子を付して出力する出力制御部とを有するものである。

(もっと読む)

データ記憶装置

【課題】不揮発性メモリへの書き込み中に電源の遮断が生じた場合であっても、記憶データの信頼性を確保しながら、必要な記憶領域を削減することができること。

【解決手段】CPU44と、記憶内容を電気的に書き換え可能なEEPROM45とを備えるエアコンECU40において、制御データの更新時に、更新された制御データと、所定の規則に従って変化する数値データとを組として、EEPROM45に書き込む。EEPROM45には、最新から順に古くなる少なくとも3組の数値データ及び制御データを保持しておく。これにより、数値データの規則性を利用して、制御データが正常に書き込まれた否かを判別できるので、制御データの信頼性を確保しながら、必要な記憶容量を削減することができる。

(もっと読む)

メモリへのデータ保持方法

【課題】メモリの信頼性を確保しながら、必要なメモリの容量を下げる。

【解決手段】メモリへのデータを書き込むにあたって、最上位に任意の値を書き込み、中間位置に必要な情報を書き込み、最下位に、最上位に書き込んだ任意の値を基にして任意の条件で作成した値を書き込むようにした。更に、任意の条件は、最上位に書き込んだ任意の値のミラー値とするようにした。また、繰り返し複数の情報を書き込むようにし、繰り返しの回数より1多い値までを使って任意の値をカウントアップ又はカウントダウンして得るようにした。

(もっと読む)

可変マッピングを備えたレーン検査

メモリ装置及びメモリ方法は、第1のレーンを第2のレーンに選択的にマッピングする。メモリ・エージェントは、別々のレーン・マッピングを用いて訓練シーケンス及び戻りシーケンスを転送し得る。戻りシーケンスを解析して障害レーンを識別し得る。他の実施例を本明細書及び特許請求の範囲に記載する。  (もっと読む)

(もっと読む)

一部のフレームについての早期CRC供給

メモリ装置及びメモリ方法は、フレームの第1の部分のCRCコードを、フレームの第2の部分の転送が終わる前に送信し、受信する。CRCを用いて、フレームの第1の部分を、フレームの第2の部分が完全に受信される前に確かめ得る。フレームの第1の部分におけるコマンドや他の情報を、フレームの残りの部分を待つことなく用い得る。他の実施例を本明細書及び特許請求の範囲に記載する。  (もっと読む)

(もっと読む)

1つまたは複数のメモリモジュールを接続するハブコンポーネント

本発明は、1つまたは複数のメモリチップを、対応するメモリチップインタフェースを介して接続するためのハブチップに関する。このハブチップは、ハブチップをアドレスバスに接続するためのアドレス入力部と、別のアドレスバスに接続するためのアドレス出力部と、アドレス入力部に与えられたアドレスを用いて、接続されたメモリチップのうちの1つをアドレス指定するため、または、与えられたアドレスをアドレス出力部に与えるためのアドレス復号器ユニットとを有する。このハブチップの特徴は、与えられたチェック用データを用いて、1つまたは複数のメモリチップのメモリ領域中のエラーを検出するためのエラー認識ユニットを有する点にある。  (もっと読む)

(もっと読む)

ポインタのリンクのチェック回路

【課題】本発明は、パケットデータの処理遅延を少なくすることができ、データの連続性が正しく復元できたかを確実にチェックできるポインタのリンクのチェック回路を提供することを目的とする。

【解決手段】第1のデータから演算した演算結果を第1のデータのポインタにより示される次の第2のデータに対応させて記憶する記憶手段40と、記憶手段から読み出した第1のデータから演算した演算結果と該読み出した前記第1のデータのポインタにより示される次のデータに対応させて記憶された演算結果を比較する比較手段46とを有する。

(もっと読む)

41 - 56 / 56

[ Back to top ]