Fターム[5B018JA12]の内容

記憶装置の信頼性向上技術 (13,264) | 試験 (271) | 試験パターン (63) | データパターン (29)

Fターム[5B018JA12]に分類される特許

1 - 20 / 29

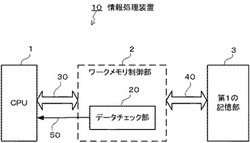

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

試験方法,試験プログラム,及び試験装置

【課題】情報処理装置の記憶部に対する試験にかかる時間の短縮又は試験精度の向上を実現する。

【解決手段】同一の基礎パターンを隣り合わせて配設した基礎パターン対を含むテストパターン42を、記憶部4の試験領域40のうちの第1領域40Aに書き込み、書き込まれた前記テストパターン42を前記試験領域40のうちの第2領域40Bに転送し、転送されたテストパターン42を、前記第1領域40Aにおける前記書き込みが行なわれたアドレスから所定のシフト量だけシフトされたアドレスに転送するとともに、前記第1領域40Aあるいは前記第2領域40Bの一方から他方に転送されたテストパターンにおける基礎パターン対の隣り合わせて配設された基礎パターン同士が等しいか否かを比較、判定することにより前記試験領域40に対する書き込み及び読み出しを正しく行なえるか否かを検証する。

(もっと読む)

RAM故障診断装置、そのプログラム

【課題】RAM故障を確実にかつ早期に検出する。

【解決手段】安全関連アプリケーション処理11による安全関連データ領域21内の安全関連データへのアクセス時に、安全関連データアクセス関数13によって当該安全関連データの格納領域に関してダブルRAM方式のRAM診断を行う。これに加えて、RAMテストパターン診断処理12によって、定期的に、各安全関連データの格納領域等に対して、複数のテストパターンを用いたRAM診断を行う。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】バーストエラーが発生したために、読み出されたデータに含まれる全てのビットの論理値が、“1”又は“0”になったときに、そのバーストエラーの発生を高い確率で検出すること。

【解決手段】ビットエラーを訂正するためのECCに符号化されたデータと共に、論理値0のビットと論理値1のビットの双方を複数ビットずつ含む整合性符号をフラッシュメモリ内のページに書き込む。そして、そのデータをフラッシュメモリから読み出したときに、そのデータ及びそのデータと共に書き込まれた整合性符号に含まれる全てのビットが論理値0のビットであるとき、又は、その全てのビットが論理値1のビットであるとき、ECCに基づいて訂正不能エラーの発生が検出されなかった場合でも、訂正不能エラーが発生したと判断し、ホストシステムにその旨を通知する。

(もっと読む)

メモリエラー箇所検出装置、及びメモリエラー箇所検出方法。

【課題】ソフトエラー等による一時的な論理アドレスと物理アドレスとの誤変換によるデータの位置誤算出を防ぐことができて信頼性を保てるストレージ制御装置を提供する。

【解決手段】ストレージシステムは、記憶装置と、ストレージ制御装置を備え、ストレージ制御装置が、ホストから書き込み指示を受け取ったとき、ホストからの書き込み指示に含まれる論理アドレスを含む読み込み指示を記憶装置へ送るデータ読み込み指示手段と、データ読み込み指示手段からの読み込み指示に基づき、記憶装置が読み取った該当位置のデータに論理アドレスが含まれている場合に、ホストから受け取った書き込み指示に含まれる論理アドレスと読み取ったデータに含まれた論理アドレスとが異なるとき、システム領域からアドレス変換情報を読み出し、読み出したアドレス変換情報をメモリに書き込むアドレス変換情報訂正手段とを有する。

(もっと読む)

不揮発性メモリのデータ破壊検出装置

【課題】不揮発性メモリに記憶されたデータがビット破壊しているか否かを検出する不揮発性メモリのデータ破壊検出装置を提供する。

【解決手段】不揮発性メモリ5は、アプリケーションの動作に使用するプログラムが書き込まれた使用アドレスとプログラムが書き込まれていない未使用アドレスとからなる。不揮発性メモリ5のデータ破壊検出装置6は、未使用アドレスに0/1の混合値と混合値の0/1が反転されたミラー値とを交互に書き込む書き込み部11と、混合値とミラー値とを読み出してデータが破壊されているか否かを判定するデータ破壊判定部12とを備えた。

(もっと読む)

システムの立ち上げ時間を早めるための方法、装置およびコンピュータ・プログラム

【課題】システムの立ち上げ時間を早めるための方法を提供する。

【解決手段】システム上にストアされたオペレーティング・システムの起動動作と並行しかつその後に、追加量のメモリを割り当てのためにスクラビングして利用することができるようにするステップとを含む。システムは、各々が最少ノード資源構成に関連付けられた1個もしくは複数個のノードを含むことができ、前記最少ノード資源構成は、前記ノードを活性化するために、活性化される必要のあるノードに含まれる最少数のプロセッサに対応する。システムは、各パーティションが少なくとも1個のノードを包含する1個もしくは複数個のパーティションを更に含むことができる。各パーティションには他のパーティションに対する優先度が割り当てられることができ、そのパーティションはその割り当てられた優先度に基づき活性化される。

(もっと読む)

誤り検出技術に基づくメモリ書き込みタイミングの調節

【解決手段】

誤り検出機能の結果に基づきメモリデバイスにおける書き込みタイミングを調節するための方法、システム及びコンピュータプログラム製品が提供される。例えば方法は、誤り検出機能の結果に基づきデータバス上の信号と書き込みクロック信号との間の書き込みタイミング窓を決定することを含むことができる。方法はまた、書き込みタイミング窓に基づきデータバス上の信号と書き込みクロック信号との間の位相差を調節することを含むことができる。メモリデバイスは、調節された位相差に基づきデータバス上の信号を回復することができる。

(もっと読む)

メモリ診断方法及びメモリ回路

【課題】メモリ回路において、運用中に自動でメモリ全体の故障検出を行うことを目的とする。

【解決手段】ネットワークから受信したフレームのフレーム間ギャップを含む空きタイムスロットで、メモリのテストを行うためのテストアドレスを順次変化させて生成するテストアドレス生成手段と、メモリのテストアドレスから読み出したデータを退避する退避手段と、メモリのテストアドレスにテストデータを書き込むテスト書き込み手段と、メモリのテストアドレスからテストデータを読み出すテスト読み出し手段と、テスト読み出し手段で読み出されたテストデータを予め保持している基準データと比較して障害の有無を判定する判定手段と、退避手段に退避されているデータを前記メモリの前記テストアドレスに書き戻す書き戻し手段とを有する。

(もっと読む)

メモリ初期化回路、メモリ初期化方法、及び情報処理装置

【課題】ソフトウエアのバグをハードウエアで検出することができるメモリ初期化回路を提供する。

【解決手段】メモリ初期化回路は、特定のデータパターンを持つ初期化データを生成する初期化データ生成手段と、メモリにECCとデータを書き込んで初期化するときにそのデータとして特定のデータパターンを持つ初期化データを書き込むようにメモリ初期化動作を制御するメモリ初期化制御手段と、初期化データの判別により、ソフトウエアのバグを検出する手段とを備える。

(もっと読む)

コンピュータ装置、データ記憶方法、および、記憶処理プログラム

【課題】揮発性記憶部に、一定期間の間、データを一定に保持するために必要な処理が行われなくても、当該揮発性記憶部に記憶されたデータの消失を防止可能な技術を提供することを目的とする。

【解決手段】コンピュータ装置1は、DRAM4と、保持能力値取得部6と、個数決定部7と、制御部8とを備える。保持能力値取得部6は、DRAM4の保持能力値を決定する。個数決定部7は、保持能力値に基づいて、記憶対象のデータが、DRAM4に記憶されるべき個数を決定する。制御部8は、記憶対象のデータを、個数決定部7で決定した個数だけDRAM4に記憶する。

(もっと読む)

固体メモリデバイスにおけるデータ復帰

【課題】固体メモリデバイスのデータ復帰技術および構成を提供する。

【解決手段】固体メモリデバイスのセルに関するハード誤りを特定する段階と、特定されたハード誤りを有するセルの位置を、セルに元々プログラミングされていたデータを復帰させる復号器に提供する段階と、復号器を利用して、セルに元々プログラミングされていたデータを復帰させる段階と、を備える。また、固体メモリデバイスのセルに格納されているデータを、データの読み出しに通常利用される参照信号とは異なる、修正された参照信号を利用して読み出す段階と、セルから読み出されたデータに基づいて、セルから読み出されたデータの少なくとも1つの値が消失用にマークされる消失フラグを形成する段階と、消失フラグを利用して、セルから読み出されたデータを復号する段階と、を備える方法を提供する。

(もっと読む)

メモリ診断装置、及び情報処理装置

【課題】メモリのメンテナンス性を向上させることができるメモリ診断装置、及びこれを備えた情報処理装置を提供する。

【解決手段】メモリ3にデータの書き込みを実行した後、メモリ3の当該アドレスからデータを読み出すテストアクセスを実行するテスト制御部201と、テスト制御部201により書き込まれたデータと読み出されたデータとを比較し、当該書き込まれたデータと当該読み出されたデータとが一致しない場合にエラーを検出するエラー検出処理を実行する比較回路242と、比較回路242においてエラーが検出された場合、書き込まれたデータと読み出されたデータとアドレスとを含むエラー情報を記憶するエラー情報記憶部243とを備えた。

(もっと読む)

メモリの検査方法

【課題】従来のメモリ検査方法では、異常が生じているアドレス信号線の位置を知ることができても、それが短絡しているのか開放しているのかは判別できないという問題があった。

【解決手段】メモリのアドレスを指定する複数のアドレス信号線を有するメモリの検査方法であって、前記基準アドレスと、検査アドレスと、検査隣接アドレスとを特定するビットを前記第1検査アドレス信号線のビットと、前記第2検査アドレス信号線のビットとの組合せが異なり、前記第1検査アドレス信号線のビット及び前記第2検査アドレス信号線のビットを除く他のビットは共通となるように決定するステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスにそれぞれ異なるデータを書き込むステップと、前記基準アドレスと、検査アドレスと、検査隣接アドレスからデータを読み取り、書き込んだデータと同一か否かを判断するステップとを有する。

(もっと読む)

情報処理装置

【課題】メモリチェックに要する時間の短縮化を図るとともに、メモリチェックの確実性を向上させることのできる情報処理装置を提供する。

【解決手段】外部メモリ3に書き込むライトデータを擬似乱数生成処理で生成するデータ生成回路10と、前記ライトデータを書き込むアドレスを擬似乱数生成処理で生成するアドレス生成回路9と、各アドレスに前記ライトデータが書き込まれると、データを読み出すアドレスを擬似乱数生成処理により生成するアドレス生成回路111と、該生成回路111で生成されたアドレスからリードデータを読み出すデータ読出し回路112と、擬似乱数生成処理で基準値を生成する基準値生成回路113と、アドレス生成回路111で生成されたアドレスごとに前記リードデータと前記基準値とを比較し、両者が不一致のとき異常信号を出力する比較回路114とを有するメモリテスト回路7をASIC4に備えた。

(もっと読む)

書き込み保護装置

【課題】本発明の目的は、プロセッサからのデータを記憶する記憶装置を診断し、プロセッサからのデータを確実に記憶装置に記憶する書き込み保護装置を提供することである。

【解決手段】本発明では、試験データを第1のレジスタに記憶し、プロセッサが第1のレジスタから読み出した試験データを第2のレジスタに書き込み、データ判定手段が第1のレジスタの試験データと第2のレジスタのデータとを比較して一致した時に、プロセッサのデータが第3のレジスタへ書き込み許可される書き込み保護装置を用いる。

(もっと読む)

複数デバイスシステムをテストするための回路および方法

複数デバイスシステムの個々のデバイスがシリアル相互接続構成に構成された、複数デバイスシステム内の、メモリの高速テストのための方法およびシステム。高速テストは、最初に複数デバイスシステムの各デバイスのメモリバンクにテストパターンデータを書き込むことと、その後に続く、各デバイス内のデータのローカルテスト読み出しおよび比較によって実現される。各デバイスは、デバイス内の障害ビット位置の有無を表すローカル結果データを発生する。各デバイス内のシリアルテスト回路は、ローカル結果データを、前のデバイスからのグローバル結果データと比較する。テスト回路は、この比較の結果を圧縮し、それを更新されたグローバル結果データとして、次のデバイスに供給する。したがって、更新されたグローバル結果データは、すべての前のデバイスのローカル結果データを表すことになる。  (もっと読む)

(もっと読む)

エラー検出装置及びエラー検出方法

【課題】 エラー検出機能の詳細な故障診断を行うことができるエラー検出装置を提供する。

【解決手段】 CPU I/F1100からメモリ1200に送られるデータ列に対するエラー検出データを生成するパリティビット生成部1301と、

エラー検出データに基づいて、メモリ1200から出力されるデータ列のエラーを検出するパリティチェック部1401と、データ列に対するエラー検出データとして、パリティビット生成部1301からのデータと、診断用のデータを送信するCPUから送られてくるデータとを切り替えて出力する選択回路1302と、選択回路1302がCPUから送られてくるデータを出力する状態にあるときに、選択回路1302から出力されたエラー検出データに基づいて、パリティビット生成部1301とパリティチェック部1401の少なくとも一方を含むエラー検出機能の故障診断を行うことを特徴としている。

(もっと読む)

負荷発生装置及び負荷試験方法

【課題】比較的少ないハードウェア資源により、高効率で高負荷を試験対象システムに与える。

【解決手段】試験対象システムのバスに負荷を与える負荷発生装置において、動作モード設定レジスタと、データ転送サイズが設定されるデータサイズレジスタと、最初のアクセス対象アドレスであるベースアドレスとストライド毎のアドレス間隔とストライド回数とが設定されるレジスタ群と、動作モードに応じて、データサイズレジスタに設定されているデータサイズ及びレジスタ群に設定されている情報に基づいて試験対象システム内のメモリ空間にアクセスするアクセス手段とを備え、アクセス手段は、アクセス対象アドレスを自動的にアドレス間隔でメモリ空間に変更する変更機構と、アクセス対象のメモリ空間に対してアドレス間隔とデータサイズに応じたデータパターンを生成する生成機構とを含み、アドレス毎にデータを変更するように構成する。

(もっと読む)

1 - 20 / 29

[ Back to top ]