Fターム[5B018MA33]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | メモリ制御回路、制御線 (30)

Fターム[5B018MA33]に分類される特許

1 - 20 / 30

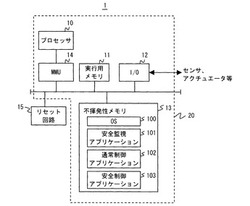

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

サーバ装置、メモリ装置

【課題】レジスタチップを搭載するためのコストを抑えつつ、メモリモジュールとメモリコントローラの間の通信を安定化させることのできる技術を提供する。

【解決手段】本発明に係るサーバ装置は、複数のメモリモジュールに対する命令を格納する共用レジスタを備える。メモリコントローラは、複数のメモリモジュールに対する命令を共用レジスタに格納し、共用レジスタは、メモリコントローラから受け取った命令を複数のメモリモジュールに対して並列出力する。

(もっと読む)

書込み制御装置

【課題】 メモリへのデータの書込みを禁止する際に誤書込みを確実に防止する。

【解決手段】 コントローラ1からメモリ2への書込み信号ライン3に、書込み信号を伝送する伝送回路4を介装する。書込み許可・禁止信号発生部5は、書込み許可信号として交番信号を発生し、書込み禁止信号として非交番信号を発生するように構成する。信号発生部5からの信号は整流回路6に入力し、整流回路6は交番信号が入力されるときにのみ電源電圧を発生させる。ここにおいて、前記伝送回路4は、その作動用電源として、前記整流回路6を用い、電源電圧が供給されているときのみ、書込み信号を伝送し、電源電圧が供給されていないときは、書込み信号の伝送を遮断する。

(もっと読む)

記憶装置、電子機器及び誤りデータの訂正方法

【課題】アドレス変換テーブルのエントリデータに誤り訂正符号を付与することなく、そのエントリデータに生じたビット異常の訂正を可能とする。

【解決手段】半導体記憶装置2は、論理アドレスに対応する物理アドレスへの変換にかかるアドレス変換テーブル31のエントリデータに付与された誤り検出符号をもとに、エントリデータに生じたビット異常を検出するアドレス変換テーブル異常検出部21と、ビット異常が検出されたエントリデータに含まれる所定のビットを反転させたデータが、正常なエントリデータであるか否かを検査するエントリデータ検査部22と、ビット異常が検出されたエントリデータを、検査された正常なエントリデータに置き換えるエントリデータ置換部23と、を備える。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】復号化回路を備えたメモリコントローラにおいて、シンドロームを算出する処理から誤り位置多項式を導出する処理への処理の引継ぎの円滑化と、誤り位置多項式を導出する処理の効率化を図る。

【解決手段】データ保持回路内の領域、シンドローム保持回路内の領域及び係数保持回路内の領域は、相互に対応関係が定められており、データ保持回路内の第1の領域に保持されたデータに基づいて算出されたシンドロームは、当該第1の領域に対応するシンドローム保持回路内の領域である第2の領域に保持され、当該第2の領域に保持されたシンドロームに基づいて算出された係数は、当該第2の領域に対応する係数保持回路内の領域である第3の領域に保持され、当該第3の領域に保持された係数に基づいて、当該第1の領域に保持されたデータのビットエラーが訂正される。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

メモリ回路及びメモリ回路制御方法

【課題】出力するデータ量を増加させることなく、チップ間のアドレスの転送誤りを検出することができるメモリ回路を提供すること

【解決手段】本発明のメモリ回路は、アドレス毎にデータが対応付けられたメモリ103を搭載するメモリチップ102と、メモリチップ102に接続されメモリ103のアドレスを指定してアドレスに対応するデータを読み出すメインチップ101と、を備える。メモリチップ102は、メインチップ101において指定され入力されたアドレスを取得するアドレス情報取得部105と、メモリ103内のデータをアドレスを用いて暗号化し、メインチップ101へ出力する暗号部104を備え、メインチップ101は、暗号部104から出力された暗号化データを、指定したアドレスを用いて復号化する復号部113と、復号化されたデータに誤りがあるか否かを判定する判定部116とを備えるものである。

(もっと読む)

記憶装置、基板、液体容器、システム及び記憶装置の制御方法

【課題】不揮発性の記憶部に記憶されたデータの破壊を抑止できる記憶装置、基板、液体容器、システム及び不揮発性の記憶部の制御方法等を提供すること。

【解決手段】記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60を制御する制御部30を含む。制御部30は、ホスト装置10からの電源電圧VDDが供給されるホスト側電源端子TVHに接続される電源端子TV及び、ホスト装置10からのグランド電圧VSSが供給されるホスト側グランド端子TGHに接続されるグランド端子TGの少なくとも一方のフローティング状態を検出する検出回路32と、システムクロックSCKのマスク処理を行うマスク処理部34を有する。そして、マスク処理部34は、検出回路32によりフローティング状態が検出された場合に、システムクロックSCKをマスクする。

(もっと読む)

誤り検出技術に基づくメモリ書き込みタイミングの調節

【解決手段】

誤り検出機能の結果に基づきメモリデバイスにおける書き込みタイミングを調節するための方法、システム及びコンピュータプログラム製品が提供される。例えば方法は、誤り検出機能の結果に基づきデータバス上の信号と書き込みクロック信号との間の書き込みタイミング窓を決定することを含むことができる。方法はまた、書き込みタイミング窓に基づきデータバス上の信号と書き込みクロック信号との間の位相差を調節することを含むことができる。メモリデバイスは、調節された位相差に基づきデータバス上の信号を回復することができる。

(もっと読む)

メモリ制御装置及びその遅延量測定方法

【課題】 量産に適用されるような一般的なテスタでも遅延回路の遅延量の測定が可能なメモリ制御装置及びその遅延量測定方法を提供することを課題とする。

【解決手段】 本メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、入力信号を遅延させて出力する複数の遅延回路を有し、通常動作時に、前記複数の遅延回路は、互いに独立し、個々の遅延回路に入力される信号を個々に遅延して出力し、テスト動作時に、前記複数の遅延回路は、テスト用入力信号が全ての遅延回路を経由し、それぞれの遅延量の合計分だけ遅延するように接続され、遅延後の前記テスト用入力信号は、テスト用出力信号として、前記メモリ制御装置の外部に出力されていることを要件とする。

(もっと読む)

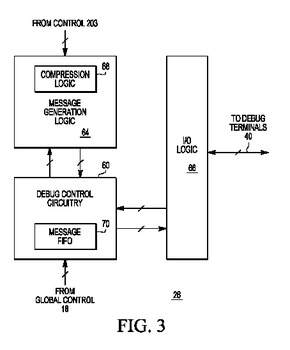

デバッグ用のアドレス変換トレースメッセージ生成

データ処理システム(10)及び方法は、外部デバッグツールをリアルタイムトレース機能を有するように許可することによってデバッグメッセージを生成する。データプロセッサ(20、22、24)は複数のデータ命令を実行し、情報記憶のためにメモリ(30)を使用する。デバッグ回路26はアドレス変換トレースメッセージを含むデバッグメッセージを生成する。仮想形態及び物理形態との間にアドレスを変換するようにアドレス変換を実行するために、メモリ管理ユニット(16)はアドレス変換論理(205)を有する。デバッグ回路(26)は、1つ以上のアドレス変換マッピングは変更される時に通信を受信するためにメモリ管理ユニット(16)に接続されるメッセージ生成回路(64)を含む。メッセージ生成回路(64)は、アドレスマッピングの変更を検出したことに応答してアドレス変換トレースメッセージを生成し、デバッグ回路(26)の外部にアドレス変換トレースメッセージを与える。  (もっと読む)

(もっと読む)

半導体記憶装置及びその自己テスト方法

【課題】テストコストの低減に対して有利な半導体記憶装置及びその自己テスト方法を提供する。

【解決手段】半導体記憶装置は、不揮発性メモリ11と前記不揮発性メモリの入出力データを格納するバッファ13とを備える主記憶部1と、揮発性メモリを備える前記主記憶部のバッファ部2と、データ入出力ピンを有する自己テストインターフェイス50と、前記主記憶部と前記バッファ部とを制御する制御部30とを具備し、前記制御部は、前記データ入出力ピンを介して自己テストインターフェイスから前記バッファへデータを格納し(S1)、前記バッファの格納データを、前記揮発性メモリへ書き込み(S2)、前記揮発性メモリから読み出したデータを前記バッファへ格納し(S4)、前記バッファの格納データを前記自己テストインターフェイスから読み出し、判定させる(S5)。

(もっと読む)

メモリの誤り訂正方法,誤り検出方法、及びそれを用いたコントローラ

【課題】

メモリとの接続故障の誤り訂正,検出方法が必要になってきた。

【解決手段】

プロセッサと、メモリ制御装置と、メモリ装置とを備えたコントローラにおいて、アドレスに対して任意のデータをライトアクセスするとき、アドレスと任意のデータから決定される誤り検出符号CRCと、誤り検出符号CRCと任意のデータから決定される誤り訂正符合ECCを生成し、任意のデータと伴に誤り検出符号CRCと誤り訂正符号ECCをメモリ装置に書き込み、プロセッサが任意のアドレスに対してリードアクセスするとき、メモリ装置に書き込まれている誤り訂正符号ECCと、誤り検出符号CRCとデータを読み出し、読み出した誤り訂正符号ECCに基づき読み出した誤り検出符号CRCと読み出したデータの誤りを訂正し、訂正された誤り検出符号CRCと読み出したデータに誤りが有るか検出する。

(もっと読む)

メモリシステム、及び、メモリエラー要因特定方法

【課題】エラーを特定することができるメモリシステムを提供すること。

【解決手段】本発明のメモリシステムによれば、ライト時において、ライトデータをループバックし、そのライトデータがエラーである場合、そのエラーは、第1処理部(51〜53)、第2処理部(56〜58)と入出力部(60)間で発生している。これにより、第1処理部(51〜53)、第2処理部(56〜58)と入出力部(60)間で発生するエラーであるのか、メモリ(8)で発生するエラーであるのかを特定することができる。

(もっと読む)

メモリ制御装置

【課題】メモリセルの状態が異常状態になっても、メモリ装置を正常に作動させることが可能なメモリ制御装置を提供すること。

【解決手段】このメモリ制御装置は、第1のアドレス制御部及び第2のアドレス制御部を有する。メモリ制御装置は、第1のアドレス制御部を用いることにより、アドレス情報に基づいてメモリセルを特定する。メモリ制御装置は、アドレス情報及び書込用情報を含む書込指示情報に応じて、上記特定されたメモリセルに書込用情報を保持させる。メモリ制御装置は、メモリセルが保持している情報に基づいて当該メモリセルの状態が異常状態であるか否かを検出する。メモリ制御装置は、メモリセルの状態が異常状態であると検出された場合に、メモリセルを特定するために用いるアドレス制御部を第1のアドレス制御部から第2のアドレス制御部へ変更する。

(もっと読む)

読み取りレベル制御装置およびその方法

読み取りレベル制御装置およびその方法を開示する。本発明の一実施形態に係る読み取りレベル制御装置は、格納手段から読み取ったデータをECC復号するECC復号部と、ECC復号されたデータおよび読み取ったデータに基づいてビットエラー率をモニタリングするモニタリング部と、モニタリングされたビットエラー率に基づいて読み取ったデータのエラー率を判断するエラー判断部と、エラー率に基づいて格納手段の読み取りレベルを制御するレベル制御部とを備えることを特徴とする。  (もっと読む)

(もっと読む)

二重化情報処理システム

【課題】コストを抑制しつつシステムの信頼性を向上させることができる二重化情報処理システムを提供する。

【解決手段】データのライト時には、第1のサブシステム10では、メモリインタフェースコントローラ13からデータをデータ用メモリ装置41に書き込む。またこのとき、第2のサブシステム20では、同一データに基づいて、誤り検出訂正回路24で生成したチェックコードをチェック用メモリ装置42に書き込む。データのリード時には、両サブシステム10,20により、メモリインタフェースコントローラ13,23により、データ用メモリ装置41から所定のデータを読み込むとともに、チェック用メモリ装置42からそのデータに対応するチェックコードを読み込む。

(もっと読む)

メモリ制御装置、メモリ装置及びこれらを用いた画像形成装置

【課題】メモリモジュールとメモリコントローラとの間で発生した異常を検出すると共に、該異常が発生した箇所を判定することが可能なメモリ制御装置及びそれを備える画像形成装置を提供すること。

【解決手段】メモリI/Fコントローラ19は、Vcc電源、及びGND電源に対してメモリモジュール11と接続された制御線CL1,CL2,・・・,CLnのうち何れかの制御線にVcc電圧又はGND電圧を交互に印加させるスイッチ制御部41と、スイッチ制御部41によって制御線CL1,CL2,・・・,CLnに印加させられたVcc電圧、及びGND電圧を検出するI/O制御部21と、Vcc電圧及びGND電圧の検出値と、Vcc電圧及びGND電圧の印加値を比較し、比較結果に基づいて制御線CL1,CL2,・・・,CLnの異常原因を判定する比較/判定部43と、異常原因に関する情報を出力する入出力部24とを備える

(もっと読む)

メモリー制御装置

【課題】メモリー制御装置において物理的に故障しているかどうかのみの確認しか可能でなく、タイミング的に問題がある場合などの検証を行うことができない。

【解決手段】高速インターフェイスを所有するDDR−SDRAMなどのメモリー制御装置において、物理的に故障しているかどうかのみならずタイミング的に問題があるかどうかを含めて確認を行うことを目的として、外部メモリー(例えばDDR−SDRAM)への書込み信号と外部メモリー(例えばDDR−SDRAM)からの読み出し信号を比較判別することによって、メモリー制御装置のCLK及び外部メモリーのCLKの周波数を変化させることを特徴としたメモリー制御装置。

(もっと読む)

メモリ制御システム

【課題】バックアップ処理を容易にするとともに、バックアップ時の消費電力を削減し、SDRAMを高速動作させる。

【解決手段】プロセッサMPUと、セルフリフレッシュ機能を有するSDRAMと、SDRAM制御手段を内蔵するメモリコントローラとを含むメモリ制御システムにおいて、前記SDRAMがバックアップ状態であるか否かを検知して前記メモリコントローラに通知する電源監視手段を備え、前記メモリコントローラが、前記電源監視手段からの通知に基づいてシステムパワーオン時における前記SDRAMのクロック無効化期間を選択することを特徴とする。

(もっと読む)

1 - 20 / 30

[ Back to top ]